# United **SiC**

### 750V-11m $\Omega$ SiC FET

Rev. B, July 2021

#### DATASHEET

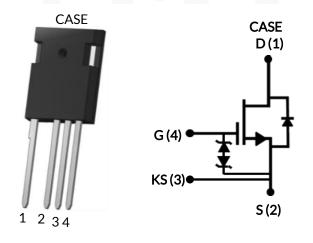

## UJ4SC075011K4S

| Part Number    | Package   | Marking        |  |  |

|----------------|-----------|----------------|--|--|

| UJ4SC075011K4S | TO-247-4L | UJ4SC075011K4S |  |  |

#### Description

The UJ4SC075011K4S is a 750V,  $11m\Omega$  G4 SiC FET. It is based on a unique 'cascode' circuit configuration, in which a normally-on SiC JFET is co-packaged with a Si MOSFET to produce a normally-off SiC FET device. The device's standard gate-drive characteristics allows for a true "drop-in replacement" to Si IGBTs, Si FETs, SiC MOSFETs or Si superjunction devices. Available in the TO-247-4L package, this device exhibits ultra-low gate charge and exceptional reverse recovery characteristics, making it ideal for switching inductive loads and any application requiring standard gate drive.

#### Features

- On-resistance R<sub>DS(on)</sub>: 11mΩ (typ)

- Operating temperature: 175°C (max)

- Excellent reverse recovery: Q<sub>rr</sub> = 288nC

- Low body diode V<sub>FSD</sub>: 1.1V

- Low gate charge:  $Q_G = 75nC$

- Threshold voltage V<sub>G(th)</sub>: 4.5V (typ) allowing 0 to 15V drive

- Low intrinsic capacitance

- ESD protected, HBM class 2

- TO-247-4L package for faster switching, clean gate waveforms

#### **Typical applications**

- EV charging

- PV inverters

- Switch mode power supplies

- Power factor correction modules

- Motor drives

- Induction heating

#### **Maximum Ratings**

| Parameter                                                         | Symbol               | Test Conditions                | Value      | Units |

|-------------------------------------------------------------------|----------------------|--------------------------------|------------|-------|

| Drain-source voltage                                              | V <sub>DS</sub>      |                                | 750        | V     |

| Cata aquiraq valtaga                                              | V                    | DC                             | -20 to +20 | V     |

| Gate-source voltage                                               | V <sub>GS</sub>      | AC (f > 1Hz)                   | -25 to +25 | V     |

| Continuous drain current <sup>1</sup>                             | 1                    | T <sub>C</sub> = 25°C          | 104        | А     |

| Continuous drain current                                          | I <sub>D</sub>       | T <sub>C</sub> = 100°C         | 75         | А     |

| Pulsed drain current <sup>2</sup>                                 | I <sub>DM</sub>      | T <sub>C</sub> = 25°C          | 300        | А     |

| Single pulsed avalanche energy <sup>3</sup>                       | E <sub>AS</sub>      | L=15mH, I <sub>AS</sub> = 4.5A | 151        | mJ    |

| SiC FET dv/dt ruggedness                                          | dv/dt                | $V_{DS} \le 500V$              | 100        | V/ns  |

| Power dissipation                                                 | P <sub>tot</sub>     | T <sub>C</sub> = 25°C          | 357        | W     |

| Maximum junction temperature                                      | T <sub>J,max</sub>   |                                | 175        | °C    |

| Operating and storage temperature                                 | TJ, T <sub>STG</sub> |                                | -55 to 175 | °C    |

| Max. lead temperature for soldering, 1/8" from case for 5 seconds | TL                   |                                | 250        | °C    |

1. Limited by  $T_{J,max}$

2. Pulse width  $t_p$  limited by  $T_{J,max}$

3. Starting  $T_J = 25^{\circ}C$

4. Short circuit current is independent of the gate voltage  $V_{\text{GS}}{>}12V$

#### **Thermal Characteristics**

| Parameter                            | Symbol Test Conditions |     | Units |      |       |      |

|--------------------------------------|------------------------|-----|-------|------|-------|------|

|                                      |                        | Min | Тур   | Max  | Units |      |

| Thermal resistance, junction-to-case | $R_{\theta JC}$        |     |       | 0.33 | 0.42  | °C/W |

#### Electrical Characteristics (T<sub>J</sub> = +25°C unless otherwise specified)

#### **Typical Performance - Static**

| Parameter                      | Cump al                                              | Test Canditions                                                            |            | Linte |      |       |  |

|--------------------------------|------------------------------------------------------|----------------------------------------------------------------------------|------------|-------|------|-------|--|

| Parameter                      | Symbol                                               | Test Conditions                                                            | Min        | Тур   | Max  | Units |  |

| Drain-source breakdown voltage | eakdown voltage BV <sub>DS</sub> V <sub>GS</sub> =0V |                                                                            | 750        |       |      | V     |  |

|                                |                                                      | V <sub>DS</sub> =750V,<br>V <sub>GS</sub> =0V, T <sub>J</sub> =25°C        |            | 3.5   | 60   |       |  |

| Total drain leakage current    | I <sub>DSS</sub>                                     | V <sub>DS</sub> =750V,<br>V <sub>GS</sub> =0V, T <sub>J</sub> =175°C       | 45         |       |      | μA    |  |

| Total gate leakage current     | I <sub>GSS</sub>                                     | V <sub>DS</sub> =0V, T <sub>J</sub> =25°C,<br>V <sub>GS</sub> =-20V / +20V | 1 - 2 + 20 |       | μΑ   |       |  |

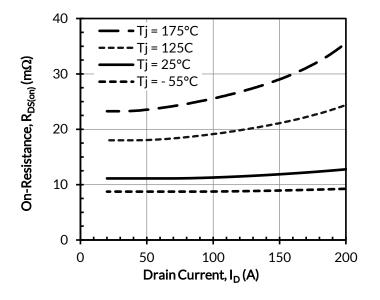

|                                | $R_{DS(on)}$                                         | V <sub>GS</sub> =12V, I <sub>D</sub> =60A,<br>T <sub>J</sub> =25°C         |            | 11    | 14.2 |       |  |

| Drain-source on-resistance     |                                                      | V <sub>GS</sub> =12V, I <sub>D</sub> =60A,<br>T <sub>J</sub> =125°C        |            | 18.4  |      | mΩ    |  |

|                                |                                                      | V <sub>GS</sub> =12V, I <sub>D</sub> =60A,<br>T <sub>J</sub> =175°C        |            | 24.2  |      |       |  |

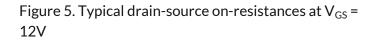

| Gate threshold voltage         | V <sub>G(th)</sub>                                   | $V_{DS}$ =5V, $I_{D}$ =10mA                                                | 3.5        | 4.5   | 5.5  | V     |  |

| Gate resistance                | R <sub>G</sub>                                       | f=1MHz, open drain                                                         |            | 2.3   |      | Ω     |  |

#### Typical Performance - Reverse Diode

| Parameter                                     | Symbol               | Test Conditions                                                             |     | - Units |      |       |

|-----------------------------------------------|----------------------|-----------------------------------------------------------------------------|-----|---------|------|-------|

| Parameter                                     | Symbol               | Test Conditions                                                             | Min | Тур     | Max  | Units |

| Diode continuous forward current <sup>1</sup> | ls                   | T <sub>C</sub> =25°C                                                        |     |         | 104  | А     |

| Diode pulse current <sup>2</sup>              | I <sub>S,pulse</sub> | T <sub>C</sub> =25°C                                                        |     |         | 300  | А     |

| Forward voltage                               | V <sub>FSD</sub>     | V <sub>GS</sub> =0V, I <sub>F</sub> =30A,<br>T <sub>J</sub> =25°C           |     | 1.1     | 1.24 | V     |

|                                               | * FSD                | V <sub>GS</sub> =0V, I <sub>F</sub> =30A,<br>T <sub>J</sub> =175°C          |     | 1.2     |      | •     |

| Reverse recovery charge                       | Q <sub>rr</sub>      | $V_{R}$ =400V, I <sub>F</sub> =60A,<br>$V_{GS}$ =0V, R <sub>G_EXT</sub> =5Ω |     | 288     |      | nC    |

| Reverse recovery time                         | t <sub>rr</sub>      | di/dt=2500A/µs,<br>T_=25°C                                                  |     | 26      |      | ns    |

| Reverse recovery charge                       | Q <sub>rr</sub>      | $V_{R}$ =400V, I <sub>F</sub> =60A,<br>$V_{GS}$ =0V, R <sub>G_EXT</sub> =5Ω |     | 292     |      | nC    |

| Reverse recovery time                         | t <sub>rr</sub>      | di/dt=2500A/μs,<br>Τ <sub>J</sub> =150°C                                    |     | 26      |      | ns    |

#### **Typical Performance - Dynamic**

| Description                                   | Currence of          | Test Conditions                                                                     |     | L la te |     |       |

|-----------------------------------------------|----------------------|-------------------------------------------------------------------------------------|-----|---------|-----|-------|

| Parameter                                     | Symbol               | Test Conditions                                                                     | Min | Тур     | Max | Units |

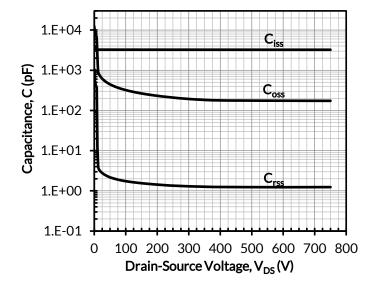

| Input capacitance                             | C <sub>iss</sub>     | - V <sub>DS</sub> =400V, V <sub>GS</sub> =0V -                                      |     | 3245    |     |       |

| Output capacitance                            | C <sub>oss</sub>     | $ v_{DS}$ =4000, $v_{GS}$ =00 $-$ f=100kHz $-$                                      |     | 178     |     | pF    |

| Reverse transfer capacitance                  | C <sub>rss</sub>     |                                                                                     |     | 1.2     |     |       |

| Effective output capacitance, energy related  | C <sub>oss(er)</sub> | V <sub>DS</sub> =0V to 400V,<br>V <sub>GS</sub> =0V                                 |     | 225     |     | pF    |

| Effective output capacitance, time related    | C <sub>oss(tr)</sub> | V <sub>DS</sub> =0V to 400V,<br>V <sub>GS</sub> =0V                                 |     | 470     |     | pF    |

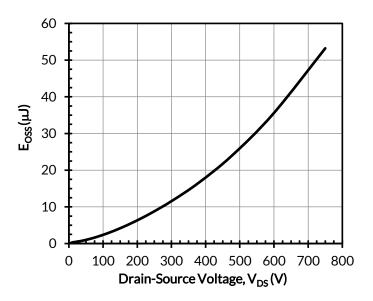

| C <sub>OSS</sub> stored energy                | E <sub>oss</sub>     | V <sub>DS</sub> =400V, V <sub>GS</sub> =0V                                          |     | 18      |     | μJ    |

| Total gate charge                             | Q <sub>G</sub>       | – V <sub>DS</sub> =400V, I <sub>D</sub> =60A, –                                     |     | 75      |     |       |

| Gate-drain charge                             | $Q_{GD}$             | $V_{DS} = -0V \text{ to } 15V$                                                      |     | 13      |     | nC    |

| Gate-source charge                            | Q <sub>GS</sub>      | VGS - 0V to 15V                                                                     |     | 22      |     |       |

| Turn-on delay time                            | t <sub>d(on)</sub>   |                                                                                     |     | 19      |     |       |

| Rise time                                     | t <sub>r</sub>       | Notes 5 and 6,<br>$V_{DS}$ =400V, $I_D$ =60A, Gate                                  |     | 26      |     | 20    |

| Turn-off delay time                           | t <sub>d(off)</sub>  | Driver =0V to +15V,                                                                 |     | 65      |     | ns    |

| Fall time                                     | t <sub>f</sub>       | Turn-on $R_{G,EXT}=1\Omega$ ,                                                       |     | 9       |     |       |

| Turn-on energy including $R_s$ energy         | E <sub>ON</sub>      | Turn-off $R_{G,EXT}=5\Omega$ ,<br>inductive Load, FWD:                              |     | 257     |     |       |

| Turn-off energy including $R_s$ energy        | E <sub>OFF</sub>     | same device with $V_{GS}$ = 0V                                                      |     | 107     |     |       |

| Total switching energy                        | E <sub>TOTAL</sub>   | and $R_G = 5\Omega$ , RC snubber:                                                   |     | 364     |     | μJ    |

| Snubber $R_s$ energy during turn-on           | E <sub>RS_ON</sub>   | $-$ R <sub>s</sub> =10 $\Omega$ and C <sub>s</sub> =400pF, $-$ T <sub>1</sub> =25°C |     | 8       |     |       |

| Snubber $R_s$ energy during turn-off          | $E_{RS_OFF}$         |                                                                                     |     | 21      |     |       |

| Turn-on delay time                            | t <sub>d(on)</sub>   |                                                                                     |     | 19      |     |       |

| Rise time                                     | t <sub>r</sub>       | Notes 5 and 6,<br>V <sub>DS</sub> =400V, I <sub>D</sub> =60A, Gate                  |     | 28      |     |       |

| Turn-off delay time                           | t <sub>d(off)</sub>  | Driver = $0V$ to +15V,                                                              |     | 73      |     | ns    |

| Fall time                                     | t <sub>f</sub>       | Turn-on $R_{G,EXT} = 1\Omega$ ,                                                     |     | 9       |     |       |

| Turn-on energy including $R_s$ energy         | E <sub>ON</sub>      | Turn-off R <sub>G,EXT</sub> =5Ω,<br>_ inductive Load, FWD: same _                   |     | 320     |     |       |

| Turn-off energy including $R_s$ energy        | E <sub>OFF</sub>     | device with $V_{GS}$ = 0V and                                                       |     | 125     |     |       |

| Total switching energy                        | E <sub>TOTAL</sub>   | $R_{G} = 5\Omega$ , RC snubber:                                                     |     | 445     |     | μJ    |

| Snubber $R_s$ energy during turn-on           | E <sub>RS_ON</sub>   | $R_{s}=10\Omega \text{ and } C_{s}=400 \text{pF},$ $T_{j}=150^{\circ}\text{C}$      |     | 8       |     |       |

| Snubber R <sub>s</sub> energy during turn-off | $E_{RS_OFF}$         |                                                                                     |     | 19      |     |       |

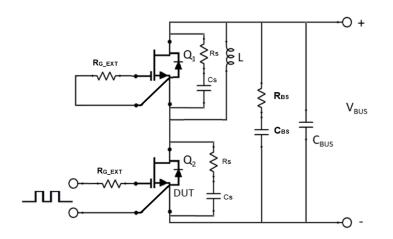

5. Measured with the switching test circuit in Figure 29.

6. In this datasheet, all the switching energies (turn-on energy, turn-off energy and total energy) presented in the tables and Figures include the device RC snubber energy losses.

#### **Typical Performance Diagrams**

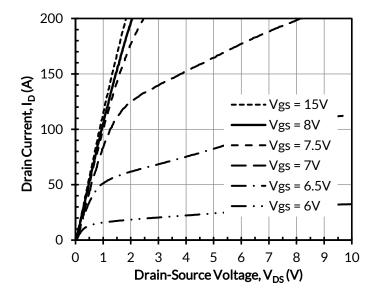

Figure 1. Typical output characteristics at  $T_{\rm J}$  = - 55°C, tp < 250 $\mu s$

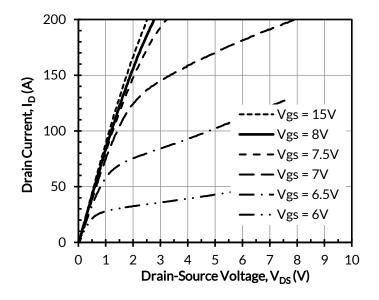

Figure 2. Typical output characteristics at T  $_{\rm J}$  = 25°C, tp < 250 $\mu s$

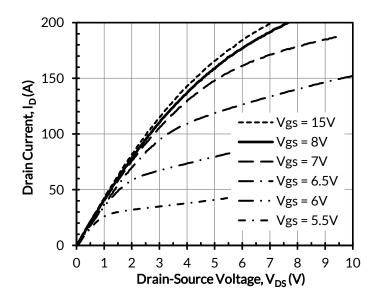

Figure 3. Typical output characteristics at T  $_{\rm J}$  = 175°C, tp < 250 $\mu s$

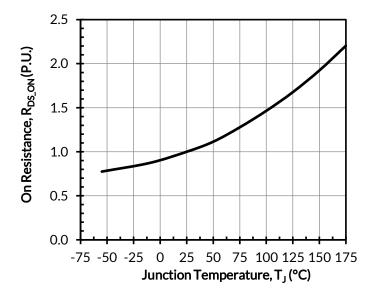

Figure 4. Normalized on-resistance vs. temperature at  $V_{GS}$  = 12V and  $I_{D}$  = 60A

|  | FET-Jet<br>Calculator | P | Buy<br>Online | <del>و</del><br>و | Spice<br>Models | $\bigcirc$ | Contact<br>Sales |  | Learn<br>More |

|--|-----------------------|---|---------------|-------------------|-----------------|------------|------------------|--|---------------|

|--|-----------------------|---|---------------|-------------------|-----------------|------------|------------------|--|---------------|

Figure 6. Typical transfer characteristics at  $V_{DS}$  = 5V

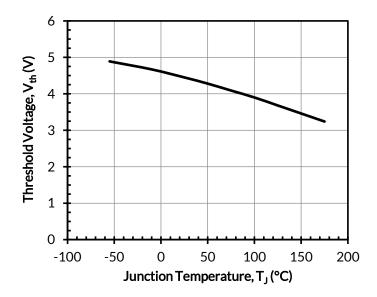

Figure 7. Threshold voltage vs. junction temperature at  $V_{\text{DS}}$  = 5V and  $I_{\text{D}}$  = 10mA

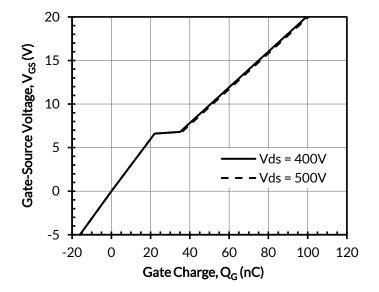

Figure 8. Typical gate charge at  $I_D$  = 60A

# United **SiC**

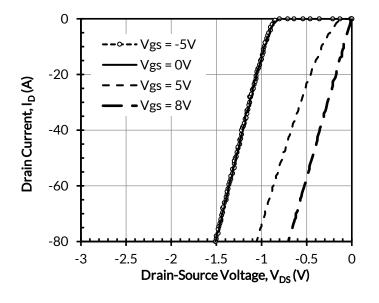

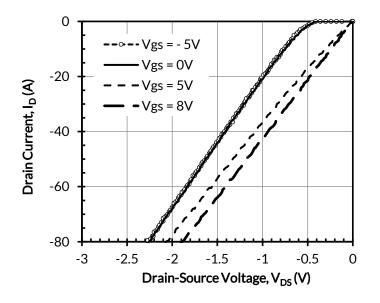

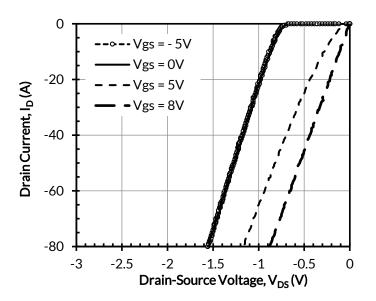

Figure 11. 3rd quadrant characteristics at T<sub>J</sub> = 175°C

Figure 10. 3rd quadrant characteristics at  $T_J = 25^{\circ}C$

Figure 12. Typical stored energy in  $C_{OSS}$  at  $V_{GS}$  = 0V

Figure 13. Typical capacitances at f = 100kHz and  $V_{GS}$  = 0V

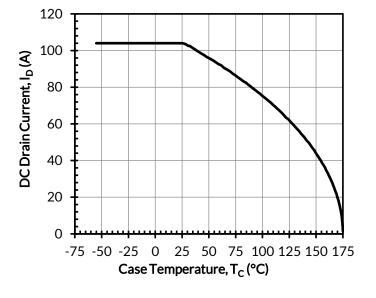

Figure 14. DC drain current derating

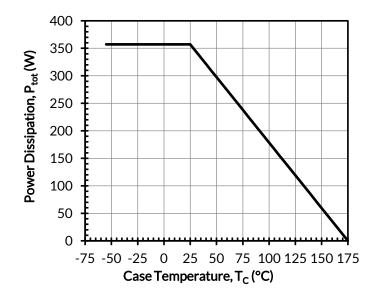

Figure 15. Total power dissipation

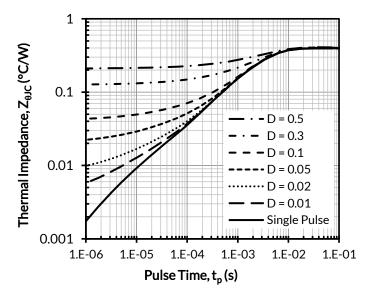

Figure 16. Maximum transient thermal impedance

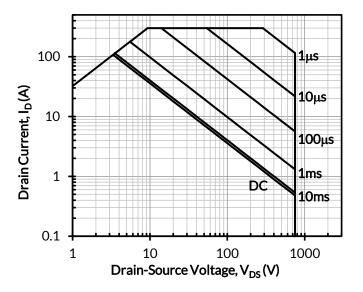

Figure 17. Safe operation area at  $T_C$  = 25°C, D = 0, Parameter  $t_p$

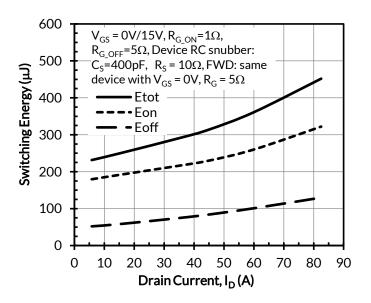

Figure 19. Clamped inductive switching energy vs. drain current at  $V_{DS}$  = 400V and  $T_J$  = 25°C

Spice

Models

Contact

Sales

Learn

More

0

FET-Jet

Calculator

III

Buy

Online

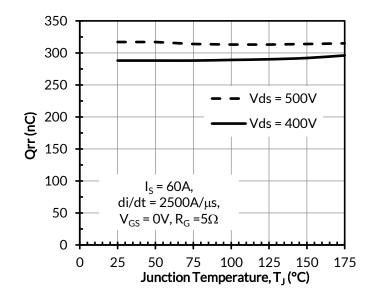

Figure 18. Reverse recovery charge Qrr vs. junction temperature

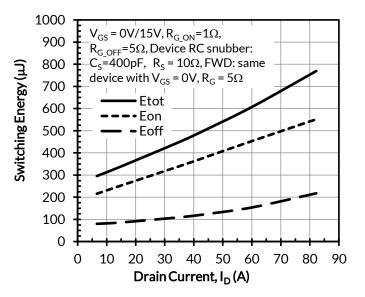

Figure 20. Clamped inductive switching energy vs. drain current at  $V_{DS}$  = 500V and  $T_J$  = 25°C

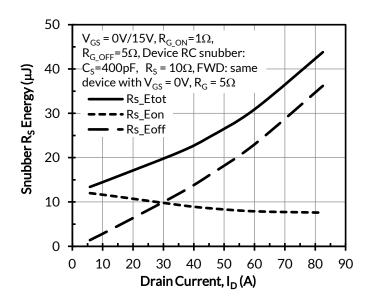

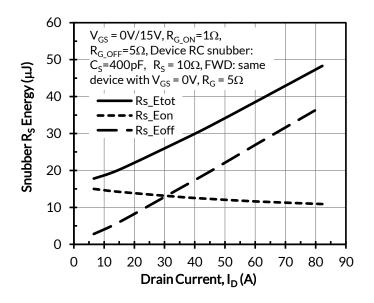

Figure 21. RC snubber energy loss vs. drain current at  $V_{DS}$  = 400V and T<sub>J</sub> = 25°C

Figure 22. RC snubber energy losses vs. drain current at  $V_{DS}$  = 500V and  $T_J$  = 25°C

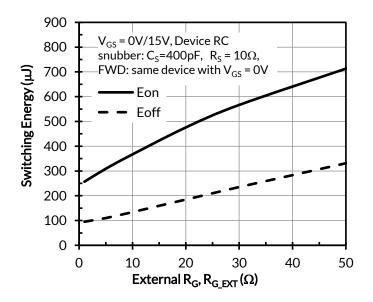

Figure 23. Clamped inductive switching energies vs.  $R_{G,EXT}$  at  $V_{DS}$  = 400V,  $I_D$  = 60A, and  $T_J$  = 25°C

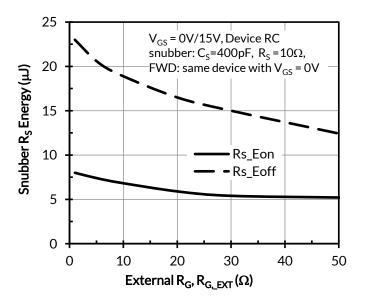

Figure 24. RC snubber energy losses vs.  $R_{G,EXT}$  at  $V_{DS}$  = 400V,  $I_D$  = 60A, and  $T_1$  = 25°C

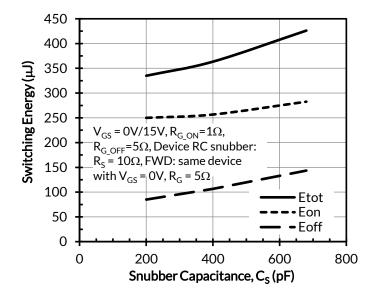

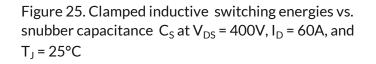

Figure 26. RC snubber energy losses vs. snubber capacitance  $C_s$  at  $V_{DS}$  = 400V,  $I_D$  = 60A, and  $T_J$  = 25°C

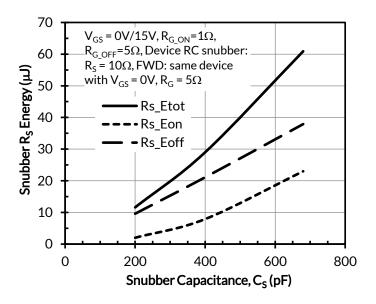

Figure 27. Clamped inductive switching energy vs. junction temperature at  $V_{DS}$  =400V and  $I_D$  = 60A

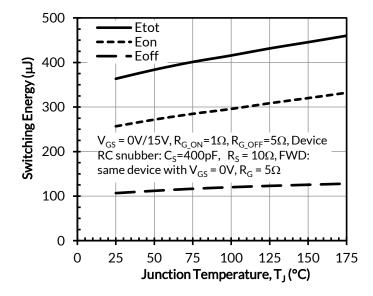

Figure 28. Clamped inductive switching energy vs. junction temperature at  $V_{DS}$  =500V and  $I_D$  = 60A

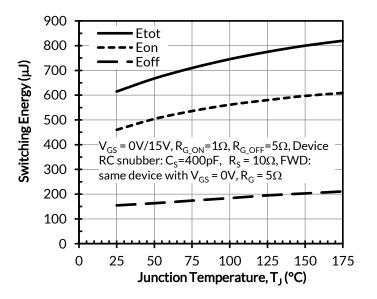

Figure 29. Schematic of the half-bridge mode switching test circuit. Note, a bus RC snubber ( $R_{BS} = 1\Omega$ ,  $C_{BS} = 100$ nF) is used to reduce the power loop high frequency oscillations.

#### **Applications Information**

SiC FETs are enhancement-mode power switches formed by a highvoltage SiC depletion-mode JFET and a low-voltage silicon MOSFET connected in series. The silicon MOSFET serves as the control unit while the SiC JFET provides high voltage blocking in the off state. This combination of devices in a single package provides compatibility with standard gate drivers and offers superior performance in terms of low on-resistance ( $R_{DS(on)}$ ), output capacitance ( $C_{oss}$ ), gate charge ( $Q_G$ ), and reverse recovery charge (Qrr) leading to low conduction and switching losses. The SiC FETs also provide excellent reverse conduction capability eliminating the need for an external anti-parallel diode.

Like other high performance power switches, proper PCB layout design to minimize circuit parasitics is strongly recommended due to the high dv/dt and di/dt rates. An external gate resistor is recommended when the FET is working in the diode mode in order to achieve the optimum reverse recovery performance. For more information on SiC FET operation, see www.unitedsic.com.

#### Disclaimer

UnitedSiC reserves the right to change or modify any of the products and their inherent physical and technical specifications without prior notice. UnitedSiC assumes no responsibility or liability for any errors or inaccuracies within. Information on all products and contained herein is intended for description only. No license, express or implied, to any intellectual property rights is granted within this document.

UnitedSiC assumes no liability whatsoever relating to the choice, selection or use of the UnitedSiC products and services described herein.

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Qorvo: UJ4SC075011K4S