# **CCM Buck Controller for Precise Current Regulation** and Wide Analog Dimming

## NCL35076

The NCL35076 is a DC-DC buck controller for wide dimming range down to 1% by analog dimming control to relieve audible noise and flicker in PWM dimming. ON Semiconductor's proprietary LED current calculation technique driven by zero input offset amplifiers performs precise constant current in the whole analog dimming range. Multi-mode operation provides low LED current ripple with small output capacitor by CCM at heavy load and deep analog dimming by DCM at light load.

PWM dimming is also provided in case that constant LED color temperature is required. NCL35076 ensures high system reliability with LED short protection, over current protection and thermal shutdown.

#### **Features**

- Wide Analog Dimming Range: 1~100%

- Low CC Tolerance: ±2% at 100% Load & ±20% at 1% Load

- Low System BOM

- LED Off Mode at Standby

- Low Standby Current

- PWM Dimming Available

- Gate Sourcing and Sinking Current of 0.5 A/0.8 A

- Robust Protection Features

- ◆ LED Short Protection

- Over Current Protection

- ◆ Thermal Shutdown

- V<sub>DD</sub> Over Voltage Protection

#### **Typical Applications**

• LED Lighting System

#### ON Semiconductor®

www.onsemi.com

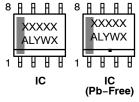

#### MARKING DIAGRAM

L30076 = Specific Device Code AA = Default Trimming Option Α = Assembly Location WL = Wafer Lot Traceability Code YYWW

= 4 Digit Data Code

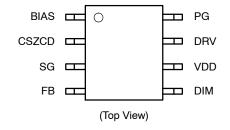

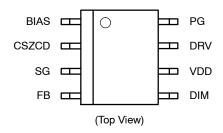

#### **PIN ASSIGNMENT**

#### **ORDERING INFORMATION**

| Device         | Package   | Shipping              |

|----------------|-----------|-----------------------|

| NCL35076AADR2G | SOIC-8 NB | 3000 /<br>Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

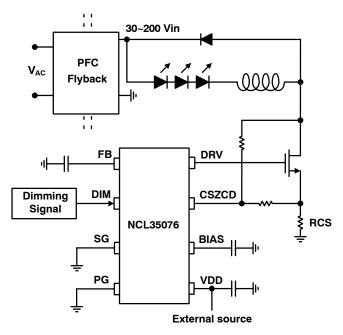

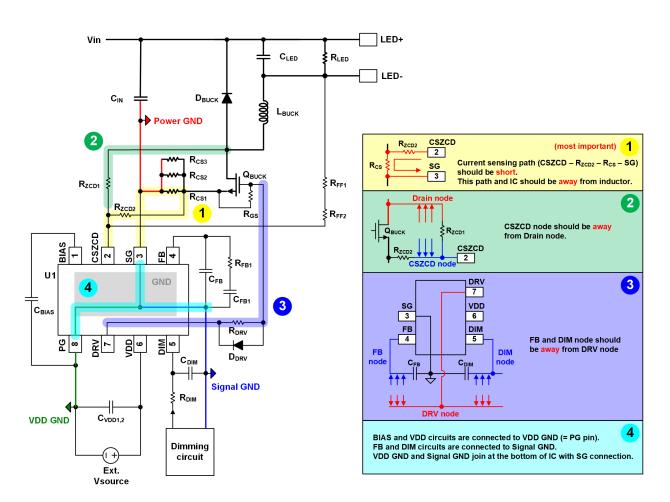

### **APPLICATION SCHEMATIC**

Figure 1. Application Schematic

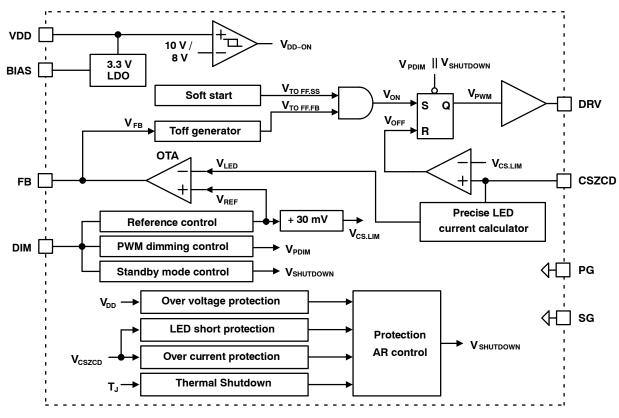

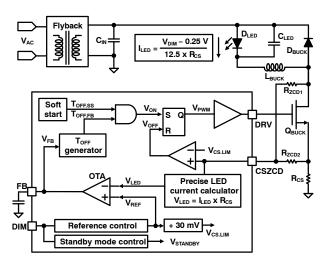

### **BLOCK DIAGRAM**

Figure 2. Simplified Block Diagram

### **PIN CONFIGURATION**

Figure 3. Pin Configuration

### PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name | Function           | Description                                                                  |

|---------|----------|--------------------|------------------------------------------------------------------------------|

| 1       | BIAS     | 3.3 V BIAS         | This pin is 3.3 V LDO output to bias the internal digital circuit            |

| 2       | CSZCD    | CS and ZCD Sensing | This pin detects the switch current and the inductor current zero cross time |

| 3       | SG       | Signal Ground      | Signal Ground is close to control pin circuit such as CSZCD, DIM and FB      |

| 4       | FB       | Feedback           | Output of feedback OTA                                                       |

| 5       | DIM      | Dimming Input      | Dimming signal is provided to this pin                                       |

| 6       | VDD      | Power Supply       | IC operating current is supplied to this pin                                 |

| 7       | DRV      | Output Drive       | This pin is connected to drive external switch                               |

| 8       | PG       | Power Ground       | Power Ground is close to the capacitors at BIAS and VDD pin                  |

#### **SPECIFICATIONS**

#### **MAXIMUM RATINGS**

| Parameter                                         | Symbol               | Value       | Unit |

|---------------------------------------------------|----------------------|-------------|------|

| VDD, DRV Pin Voltage Range                        | V <sub>MV(MAX)</sub> | -0.3 to 30  | V    |

| DIM, FB, CSZCD, BIAS Pin Voltage Range            | V <sub>LV(MAX)</sub> | -0.3 to 5.5 | V    |

| Maximum Power Dissipation (T <sub>A</sub> < 50°C) | P <sub>D(MAX)</sub>  | 550         | mW   |

| Maximum Junction Temperature                      | T <sub>J(max)</sub>  | 150         | °C   |

| Storage Temperature Range                         | T <sub>STG</sub>     | -55 to 150  | °C   |

| Junction-to-Ambient Thermal Impedance             | $R_{	heta JA}$       | 145         | °C/W |

| ESD Capability, Human Body Model (Note 2)         | ESD <sub>HBM</sub>   | 2           | kV   |

| ESD Capability, Charged Device Model (Note 2)     | ESD <sub>CDM</sub>   | 1           | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHĂRACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

- 2. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model per JEDEC Standard JESD22-A114

- ESD Charged Device Model per JEDEC Standard JESD22-C101

- Latch-up Current Maximum Rating ±100 mA per JEDEC Standard JESD78

#### **RECOMMENDED OPERATING RANGES**

| Parameter            | Symbol | Min | Max | Unit |

|----------------------|--------|-----|-----|------|

| Junction Temperature | $T_J$  | -40 | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### **ELECTRICAL CHARACTERISTICS** ( $V_{DD} = 15 \text{ V}$ and $T_J = -40 \sim 125 ^{\circ}\text{C}$ unless otherwise specified)

| Parameter                             | Test Conditions                                                                                                                | Symbol                    | Min   | Тур   | Max   | Unit |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|-------|-------|------|

| VDD SECTION                           | <b>-</b>                                                                                                                       |                           |       |       |       |      |

| IC Turn-On Threshold Voltage          |                                                                                                                                | V <sub>DD(ON)</sub>       | 9.3   | 10.0  | 10.7  | V    |

| IC Turn-Off Threshold Voltage         |                                                                                                                                | V <sub>DD(OFF)</sub>      | 7.4   | 8.0   | 8.6   | V    |

| Startup Current                       | $V_{DD} = V_{DD(ON)} - 1.6 \text{ V}$                                                                                          | I <sub>DD(ST)</sub>       | -     | 250   | 400   | μΑ   |

| Operating Current                     |                                                                                                                                | I <sub>DD(OP)</sub>       | -     | 6.5   | 8.0   | mA   |

| Standby Current                       |                                                                                                                                | I <sub>DD(SB)</sub>       | -     | 200   | 300   | μΑ   |

| BIAS SECTION                          |                                                                                                                                |                           |       |       |       |      |

| BIAS Voltage                          |                                                                                                                                | V <sub>BIAS</sub>         | 3.23  | 3.30  | 3.37  | V    |

|                                       | T <sub>J</sub> = 25~100°C (Note 4)                                                                                             |                           | 3.25  | 3.30  | 3.35  | V    |

| DIM SECTION                           |                                                                                                                                |                           |       |       |       |      |

| DIM Voltage for 100% V <sub>REF</sub> | V <sub>DIM</sub> = 2.6 V                                                                                                       | V <sub>DIM(REF-MAX)</sub> | 2.44  | 2.50  | 2.56  | V    |

| DIM Voltage for 99% V <sub>REF</sub>  |                                                                                                                                | V <sub>DIM(MAX-EFF)</sub> | 2.400 | 2.475 | 2.528 | V    |

| Standby Enabling DIM Voltage          |                                                                                                                                | V <sub>DIM(SB-ENA)</sub>  | 50    | 75    | 100   | mV   |

| Standby Disabling DIM Voltage         |                                                                                                                                | $V_{DIM(SB-DIS)}$         | 60    | 100   | 140   | mV   |

| Standby Delay Time                    |                                                                                                                                | t <sub>SB(DELAY)</sub>    | 9     | 10    | 11    | ms   |

| FB SECTION                            |                                                                                                                                |                           |       |       |       |      |

| FB OTA Source Current                 | IFB = $(V_{LED} - V_{REF}) \times g_{M(FB)} \times 12.5$<br>$V_{REF} = 120 \text{ mV}, V_{LED} = 80 \text{ mV}$                | I <sub>FB(SOURCE)</sub>   | -14.0 | -11.5 | -9.0  | μΑ   |

| FB OTA Sink Current                   | IFB = (V <sub>LED</sub> - V <sub>REF</sub> ) x g <sub>M(FB)</sub> x 12.5<br>V <sub>REF</sub> = 40 mV, V <sub>LED</sub> = 80 mV | I <sub>FB(SINK)</sub>     | 9.0   | 11.5  | 14.0  | μΑ   |

$\textbf{ELECTRICAL CHARACTERISTICS} \ (V_{DD} = 15 \ V \ \text{and} \ T_{J} = -40 \sim 125 ^{\circ} C \ \text{unless otherwise specified)} \ (continued)$

| Parameter                                | Test Conditions                                            | Symbol                     | Min  | Тур  | Max  | Unit |

|------------------------------------------|------------------------------------------------------------|----------------------------|------|------|------|------|

| FB SECTION                               |                                                            | •                          |      |      |      |      |

| FB OTA Transconductance                  | $g_{M(FB)} = I_{FB} / \{(V_{REF} - V_{LED}) \times 12.5\}$ | 9 <sub>M(FB)</sub>         | 18   | 23   | 28   | μmho |

| FB OTA High Voltage                      | V <sub>REF</sub> = 120 mV, V <sub>LED</sub> = 80 mV        | V <sub>FB(HIGH)</sub>      | 4.7  | -    | -    | V    |

| FB Minimum Clamping Voltage              | V <sub>REF</sub> = 0 mV, V <sub>LED</sub> = 80 mV          | V <sub>FB(CLP)</sub>       | 0.4  | 0.5  | 0.6  | V    |

| CS SECTION                               |                                                            |                            |      |      |      |      |

| CS Regulation                            |                                                            | V <sub>CS(REG-MAX)</sub>   | 175  | 180  | 185  | mV   |

| CS Current Ripple Voltage                |                                                            | V <sub>CS(RIPPLE)</sub>    | 25   | 30   | 35   | mV   |

| CS Current Limit Minimum                 |                                                            | V <sub>CS(LIM-MIN)</sub>   | 72   | 80   | 88   | mV   |

| DUTY SECTION                             |                                                            |                            |      |      |      |      |

| Leading Edge Blanking Time at<br>Turn-on |                                                            | t <sub>LEB(TON)</sub>      | 360  | 400  | 440  | ns   |

| Maximum Ton Time                         |                                                            | t <sub>ON(MAX)</sub>       | 45   | 50   | 55   | μs   |

| Minimum Toff Time                        | V <sub>FB</sub> = 3.8 V                                    | t <sub>OFF(MIN)</sub>      | 400  | 850  | 1000 | ns   |

| Maximum Toff Time                        | V <sub>FB</sub> = 0.5 V                                    | t <sub>OFF(MAX)</sub>      | 1.17 | 1.30 | 1.43 | ms   |

| Maximum FB Voltage for Min. Toff         |                                                            | V <sub>FB(MAX-TOFF)</sub>  | 3.30 | 3.43 | 3.55 | V    |

| Minimum FB Voltage for Max. Toff         |                                                            | V <sub>FB(MIN-TOFF)</sub>  | 0.9  | 1.1  | 1.3  | V    |

| DRV SECTION                              |                                                            |                            |      |      |      |      |

| DRV Low Voltage                          |                                                            | $V_{DRV(LOW)}$             | -    | -    | 0.2  | V    |

| DRV High Voltage                         | V <sub>DD</sub> = 15 V                                     | V <sub>DRV(HIGH)</sub>     | 11   | 12   | 13   | V    |

| DRV Rising Time                          | C <sub>DRV</sub> = 3.3 nF                                  | t <sub>DRV(R)</sub>        | 60   | 100  | 145  | ns   |

| DRV Falling Time                         | C <sub>DRV</sub> = 3.3 nF                                  | t <sub>DRV(F)</sub>        | 25   | 55   | 105  | ns   |

| AUTO RESTART SECTION                     |                                                            |                            |      |      |      |      |

| Auto Restart Time at Protection          |                                                            | t <sub>AR(PROT)</sub>      | 0.9  | 1.0  | 1.1  | S    |

| VDD OVER VOLTAGE PROTECTION              | SECTION                                                    |                            |      |      |      |      |

| VDD Over Voltage Threshold Voltage       |                                                            | $V_{DD(OVP)}$              | 22   | 23   | 24   | V    |

| SHORT LED PROTECTION SECTION             | l .                                                        |                            |      |      |      |      |

| SLP Monitoring Triggering Delay<br>Time  |                                                            | t <sub>SLP</sub> (MON-DEL) | 18   | 20   | 22   | ms   |

| SLP Monitoring Disable Time at Startup   |                                                            | t <sub>SLP(MON-DIS)</sub>  | 10.8 | 12.0 | 13.2 | ms   |

| OVER CURRENT PROTECTION SEC              | TION                                                       | · '                        |      |      |      | -    |

| CS Over Current Protection Threshold     |                                                            | V <sub>CS(OCP)</sub>       | 0.4  | 0.5  | 0.6  | V    |

| THERMAL SHUTDOWN SECTION                 |                                                            | •                          |      |      |      |      |

| Thermal Shut Down Temperature (Note 3)   |                                                            | T <sub>SD</sub>            | 130  | 150  | 170  | °C   |

| Thermal Shut Down Hysteresis (Note 3)    |                                                            | T <sub>SD(HYS)</sub>       | 25   | 30   | 35   | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Guaranteed by design.

Guaranteed by characterization.

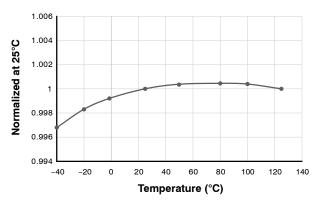

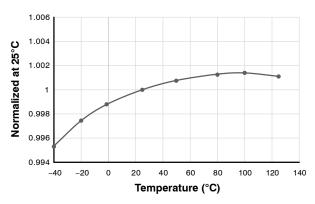

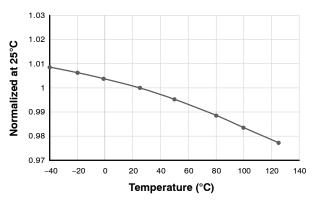

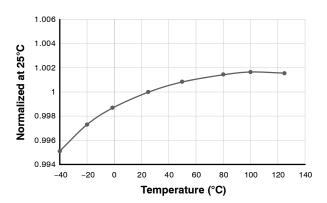

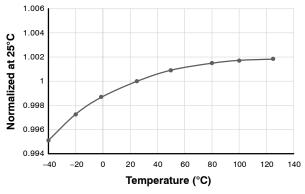

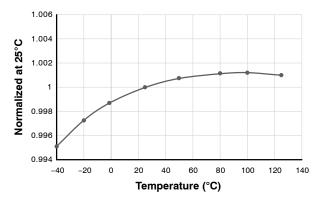

### TYPICAL CHARACTERISTICS

(These characteristic graphs are normalized at  $T_A = 25$ °C)

Figure 4. V<sub>BIAS</sub> vs. Temperature

Figure 5. V<sub>DIM(MAX)</sub> vs. Temperature

Figure 6.  $g_{M(FB)}$  vs. Temperature

Figure 7.  $V_{CS(REG-MAX)}$  vs. Temperature

Figure 8.  $V_{CS(LIM-MIN)}$  vs. Temperature

Figure 9. V<sub>DD(OVP)</sub> vs. Temperature

#### APPLICATION INFORMATION

#### General

NCL35076 provides wide analog dimming down to 1% with high CC accuracy. According to buck inductor, input voltage and output voltage, deep dimming down to 0.1~0.2% load can be achieved. Thanks to the ON semiconductor's proprietary LED current calculation technique, NCL35076 is able to measure the current of LED load connected at input voltage node without the upper limit of the input voltage with high system reliability. LED current is sensed and regulated by internal zero input offset amplifiers so that NCL35076 performs precise CC regulation in the whole analog dimming range. Therefore, CC tolerance is tightly controlled in ±2% at 100% load and ±20% at 1% load.

#### **Wide Analog Dimming**

Wide analog dimming range is obtained by transitioning multi-mode between CCM and DCM according to the dimming condition. At full load condition, CCM with  $\pm 17\%$  inductor current ripple minimizes the conduction loss with high efficiency and DCM is entered at light load condition to perform analog deep dimming. Dimming curve linearity is obtained by a digital compensator in the entire dimming range.

### **PWM Dimming**

Analog dimming has benefits for less audible noise and flicker compared to PWM dimming. However, there is a need of PWM dimming method to keep the constant LED color temperature in specific applications. NCL35076 supports PWM dimming by simply inputting PWM dimming signal to DIM pin.

#### **Precise CC Regulation**

CC regulation is very important especially in programmable LED driver because the driver should keep precise CC control under the system variation of LED load, inductor, temperature, etc. Since NCL35076 applies zero input offset amplifiers at LED current calculator block and

OTA, CC tolerance is less than  $\pm 2\%$  at 100% load and  $\pm 20\%$  at 1% load in the system variation.

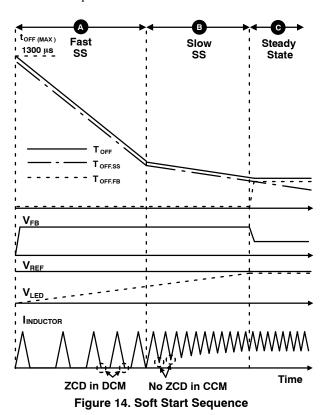

#### Soft start

Without soft start in the closed loop CC control, the LED current overshoot is easily occurred at startup so that the overshoot can affect a lifetime of LEDs and incur an undesirable flash. NCL35076 provides soft start technique to prevent the LED current overshoot by T<sub>OFF</sub> time control.

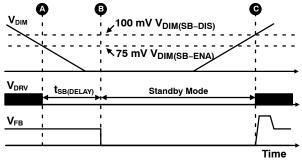

#### **Standby Mode**

When  $V_{DIM}$  is lower than a standby threshold voltage for 10 ms, standby mode is triggered with LED turn-off and IC current consumption is minimized.

### Auto Restart (AR) at Protection

Once protection is triggered, IC operation stops for 1 second and begins soft start operation after the auto restart time delay.

### **VDD Over Voltage Protection (OVP)**

When VDD is higher than 23 V, over voltage protection is triggered.

### **Short LED Protection (SLP)**

When LED is short circuited, the buck stage operates in CCM with maximum turn-off time. By detecting this condition, short LED protection is triggered.

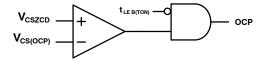

#### **Over Current Protection (OCP)**

When CSZCD voltage exceeds the over current threshold voltage, switching is immediately shut down after leading edge blanking time in the short circuit condition of the inductor, the freewheeling diode or the LED load.

### Thermal Shot Down (TSD)

When IC junction temperature is higher than 150°C, TSD is triggered and released when the temperature is lower than 120°C.

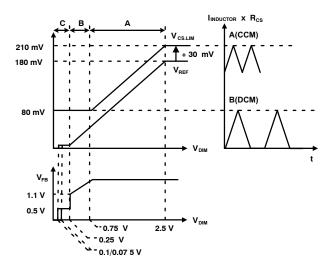

#### **BASIC OPERATION**

NCL35076 is the current mode buck controller in which DRV is off when  $V_{CSZCD}$  reaches to  $V_{CS.LIM}$  (=  $V_{REF}$  + 30 mV) and DRV is on by  $T_{OFF}$  generator controlled by  $V_{FB}$ .  $V_{LED}$  is calculated based on  $V_{CSZCD}$  in precise LED current calculator block composed of zero input offset amplifiers and  $V_{REF}$  is controlled by DIM signal. In reference control block,  $V_{REF}$  is obtained by below equation.

$$V_{REF}[V] = \frac{V_{DIM} - 0.25 V}{12.5}$$

(eq. 1)

$V_{LED}$  is compared with  $V_{REF}$  at OTA to generate  $V_{FB}$  which controls  $T_{OFF}$  time in  $T_{OFF}$  generator.  $T_{OFF}$  is inversely proportional to  $V_{FB}$ . Therefore,  $T_{OFF}$  is shorter as  $V_{FB}$  increases.  $T_{OFF}$  is set by below equation.

$$T_{OFF} [\mu s] = \frac{1.8}{V_{FB} - 1.1} + 0.1$$

(eq. 2)

Figure 10. NCL35076 Block Diagram

#### **Wide Analog Dimming**

NCL35076 operates in CCM at heavy load and in DCM at light load for a wide analog dimming. Figure 11 shows how NCL35076 operates with  $V_{DIM}$ .

- <u>A:</u>  $V_{CS.LIM}$  follows  $V_{REF}$  + 30 mV which is  $\pm 17\%$  inductor current ripple at 2.5  $V_{DIM}$ .  $V_{FB}$  is almost constant with same  $T_{OFF}$  in the CCM region.

- <u>B:</u> V<sub>CS,LIM</sub> is clamped to 80 mV and doesn't changed by V<sub>DIM</sub>. T<sub>OFF</sub> is lengthened for dimming as V<sub>FB</sub> is decreased. Operating mode is transitioned from CCM to DCM at the boundary of A and B region.

- <u>C:</u> When V<sub>DIM</sub> is lower than 0.25 V, V<sub>REF</sub> is set to 0 V and V<sub>FB</sub> is pulled down to 0.5 V clamping voltage with min.

LED current under open loop control. When V<sub>DIM</sub> is further lower than 0.1/0.075 V, standby is triggered with LED turn-off.

Figure 11. Operation Mode vs. V<sub>DIM</sub>

#### **Precise CC Regulation**

The output of the precise LED current calculator,  $V_{LED}$ , is generated by analog sensing amplifiers and  $V_{LED}$  is compared with  $V_{REF}$  by OTA to generate  $V_{FB}$ . Those sensing amplifiers and OTA have zero input offset compensation technique which performs the excellent CC regulation.

Figure 12 shows dimming curves and CC tolerance. They are measured by changing inductor ( $\pm 20\%$ ), temperature (-10, 25, 90°C) and output voltage (10, 30, 50 V) in 60 V input 75 W driver. As a result, CC tolerance at 1% deep dimming condition is less than  $\pm 10\%$  and less than  $\pm 1.5\%$  at full load condition.

Figure 12. NCL35076 Dimming Curve and CC Tolerance

#### **Standby Mode**

Standby mode is triggered by  $V_{DIM}$  as shown in Figure 13.

- <u>A:</u> When V<sub>DIM</sub> is lower than V<sub>DIM(SB-ENA)</sub>, DRV block is shut down. So, LED lamps turn off.

- <u>B:</u> After t<sub>SB(DELAY)</sub> (10 ms), standby mode is entered and NCL35076 current consumption drops to I<sub>DD(SB)</sub>.

- <u>C:</u> When V<sub>DIM</sub> is higher than V<sub>DIM(SB-DIS)</sub>, standby mode is immediately terminated and IC starts up.

Figure 13. NCL35076 Standby Mode

#### **Soft Start**

During soft start operation, T<sub>OFF</sub> is decided by either T<sub>OFF</sub><sub>SS</sub> or T<sub>OFF</sub><sub>FB</sub>. T<sub>OFF</sub> is governed by T<sub>OFF</sub><sub>SS</sub> in early start up because T<sub>OFF</sub><sub>SS</sub> decreases from t<sub>OFF</sub><sub>(MAX)</sub>. When T<sub>OFF</sub><sub>SS</sub> reaches to the steady state level, V<sub>FB</sub> is settled to the regulation level and T<sub>OFF</sub> is finally decided by T<sub>OFF</sub><sub>FB</sub>. In the end of the soft start time, T<sub>OFF</sub><sub>SS</sub> reaches to 0 and doesn't affect T<sub>OFF</sub> control anymore. Figure 14 shows how the soft start operates.

- A: V<sub>FB</sub> is pulled up as V<sub>LED</sub> is far below V<sub>REF</sub>. T<sub>OFF\_SS</sub> is reduced quickly from t<sub>OFF(MAX)</sub> in Fast SS. Fast SS ends when inductor current zero cross (ZCD) is not detected.

- B: Slow SS starts when there is no ZCD in CCM.

- <u>C:</u> V<sub>LED</sub> is closer to V<sub>REF</sub>, and V<sub>FB</sub> starts falling. Then, T<sub>OFF</sub> is determined by T<sub>OFF</sub> F<sub>B</sub> and the steady state starts.

#### **Protections**

When protection is triggered, all functional blocks stop operating and begin to start up after 1 second AR time.

- VDD Over Voltage Protection (OVP)

When VDD is higher than V<sub>DD(OVP)</sub> (23 V), VDD OVP is triggered. Open LED protection can be implemented by VDD OVP when VDD is supplied by auxiliary winding in the buck inductor.

- Over Current Protection (OCP)

When CSZCD voltage is higher than V<sub>CS(OCP)</sub> (0.5 V) after leading edge blanking time, t<sub>LEB(TON)</sub> (400 ns), IC immediately shuts down.

Figure 15. OCP Block

#### • Short LED Protection (SLP)

When LED load is short–circuited, demagnetizing time of the inductor is very long due to zero output voltage so that  $T_{OFF}$  is lengthened and  $T_{ON}$  is very short. If CCM and  $t_{OFF(MAX)}$  are detected for SLP monitoring time,  $t_{SLP(MON-DEL)}$  (20 ms), SLP is triggered. In order to prevent abnormal SLP triggering at startup, SLP monitoring is disabled for  $t_{SLP(MON-DIS)}$  (12 ms) after  $1^{st}$  switching begins.

### Thermal Shut Down (TSD)

When the junction temperature is higher than  $T_{SD}$ , the system shuts down and the junction temperature is monitored at every 1 second delay time (AR time). When the temperature is lower than  $T_{SD}-T_{SD(HYS)}$ , the system restarts.

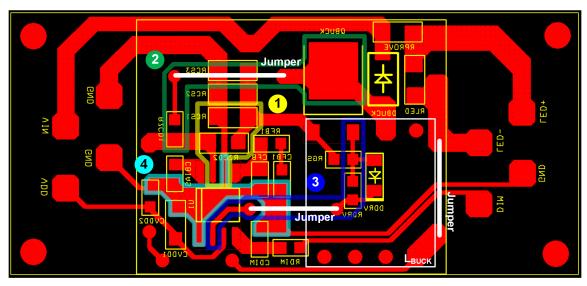

#### **PCB LAYOUT GUIDANCE**

(75-W Demo Board Schematic)

(PCB Layout Guidance)

(75-W Demo Board PCB Layout - Bottom)

Figure 16. Layout Guidance

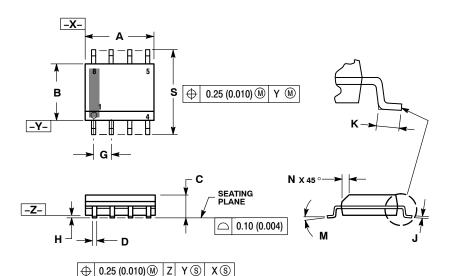

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |       | INC       | HES   |

|-----|-------------|-------|-----------|-------|

| DIM | MIN         | MAX   | MIN       | MAX   |

| Α   | 4.80        | 5.00  | 0.189     | 0.197 |

| В   | 3.80        | 4.00  | 0.150     | 0.157 |

| С   | 1.35        | 1.75  | 0.053     | 0.069 |

| D   | 0.33        | 0.51  | 0.013     | 0.020 |

| G   | 1.27        | 7 BSC | 0.050 BSC |       |

| Н   | 0.10        | 0.25  | 0.004     | 0.010 |

| J   | 0.19        | 0.25  | 0.007     | 0.010 |

| K   | 0.40        | 1.27  | 0.016     | 0.050 |

| М   | 0 °         | 8 °   | 0 °       | 8 °   |

| N   | 0.25        | 0.50  | 0.010     | 0.020 |

| S   | 5.80        | 6.20  | 0.228     | 0.244 |

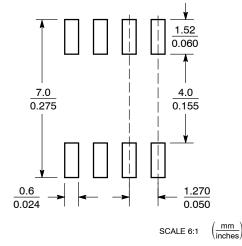

### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

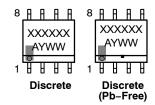

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location

= Wafer Lot = Year = Work Week

= Pb-Free Package

XXXXXX = Specific Device Code = Assembly Location Α

= Year ww = Work Week

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Rep<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                             | PAGE 1 OF 2 |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

### SOIC-8 NB CASE 751-07 ISSUE AK

### DATE 16 FEB 2011

| STYLE 3: PIN 1. DRAIN, PIE #1 CTOR, #1 CTOR, #2 CTOR, #1 CTOR, #2 CTOR, #2 CTOR, #2 CTOR, #2 CTOR, #1 | 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE  STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #1 Vd  STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN 8. TYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #1 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E PIN 1. INPUT 2. EXTERNAL BY 3. THIRD STAGE 4. GROUND E 5. DRAIN 6. GATE 3 7. SECOND STAGE 8. FIRST STAGE STYLE 11: ID PIN 1. SOURCE 1 2. GATE 1 T 3. SOURCE 2 ID 4. GATE 2 ID 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 ID 8. DRAIN 1 ID | PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 Vd 8. COLLECTOR, #1  STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN 8. TYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2                                                                                                                                                                               |

| ID PIN 1. SOURCE 1 2. GATE 1 T 3. SOURCE 2 ID 4. GATE 2 ID 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 ID 8. DRAIN 1 STYLE 15: RCE PIN 1. ANODE 1 E 2. ANODE 1 RCE 3. ANODE 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2                                                                                                                                                                                                                                                                                                                                 |

| STYLE 15:  RCE PIN 1. ANODE 1 E 2. ANODE 1 RCE 3. ANODE 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PIN 1. EMITTER, DIE #1<br>2. BASE, DIE #1<br>3. EMITTER, DIE #2                                                                                                                                                                                                                                                                                                                                                                                                                   |

| N 7. CATHODE, CON<br>N 8. CATHODE, CON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MMON         5. COLLECTOR, DIE #2           MMON         6. COLLECTOR, DIE #2           MMON         7. COLLECTOR, DIE #1           MMON         8. COLLECTOR, DIE #1                                                                                                                                                                                                                                                                                                             |

| STYLE 19: PIN 1. SOURCE 1 E 2. GATE 1 E 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 DE 7. DRAIN 1 DE 8. MIRROR 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                                                                                                                                                                                                                                                                                                             |

| STYLE 23: E1 PIN 1. LINE 1 IN DN CATHODE/VCC 2. COMMON ANC DN CATHODE/VCC 3. COMMON ANC E3 4. LINE 2 IN DN ANODE/GND 5. LINE 2 OUT E4 6. COMMON ANC E5 7. COMMON ANC DN ANODE/GND 8. LINE 1 OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ODE/GND 2. EMITTER ODE/GND 3. COLLECTOR/ANODE                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V MON 6. VBULK 7. VBULK 8. VIN                                                                                                                                                                                                                                                                                                                                                                                  |

| 1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ E 5. SOURCE E 6. SOURCE E 7. SOURCE 8. DRAIN                                                                                                                                                                                                                                                                                                                                                                                    |

| DOCUMENT NUMBER: | 98ASB42564B | Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|---------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                 | PAGE 2 OF 2 |  |

ON Semiconductor and IN are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability. arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative