SLLS509E - AUGUST 2001 - REVISED JUNE 2010

- **Integrated Asynchronous-Communications Element**

- Consists of Four Improved TL16C550C **ACEs Plus Steering Logic**

- In FIFO Mode, Each ACE Transmitter and Receiver Is Buffered With 16-Byte FIFO to **Reduce the Number of Interrupts to CPU**

- In TL16C450 Mode, Hold and Shift **Registers Eliminate Need for Precise** Synchronization Between the CPU and **Serial Data**

- Up to 16-MHz Clock Rate for up to 1-Mbaud Operation with  $V_{CC} = 3.3 \text{ V}$  and 5 V

- **Programmable Baud-Rate Generators Which Allow Division of Any Input** Reference Clock by 1 to (2<sup>16</sup>-1) and Generate an Internal 16 × Clock

- **Adds or Deletes Standard Asynchronous** Communication Bits (Start, Stop, and Parity) to or From the Serial-Data Stream

- Independently Controlled Transmit, Receive, Line Status, and Data Set Interrupts

- 5-V and 3.3-V Operation

- **Fully Programmable Serial Interface Characteristics:**

- 5-, 6-, 7-, or 8-Bit Characters

- Even-, Odd-, or No-Parity Bit

- 1-, 1 1/2-, or 2-Stop Bit Generation

- Baud Generation (DC to 1-Mbit Per Second)

- **False Start Bit Detection**

- **Complete Status Reporting Capabilities**

- **Line Break Generation and Detection**

- **Internal Diagnostic Capabilities:**

- Loopback Controls for Communications **Link Fault Isolation**

- Break, Parity, Overrun, Framing Error **Simulation**

- Fully Prioritized Interrupt System Controls

- Modem Control Functions (CTS, RTS, DSR,  $\overline{DTR}$ ,  $\overline{RI}$ , and  $\overline{DCD}$ )

- 3-State Outputs Provide TTL Drive **Capabilities for Bidirectional Data Bus and Control Bus**

- Programmable Auto-RTS and Auto-CTS

- **CTS** Controls Transmitter in Auto-CTS Mode.

- **RCV FIFO Contents and Threshold Control** RTS in Auto-RTS Mode.

#### description

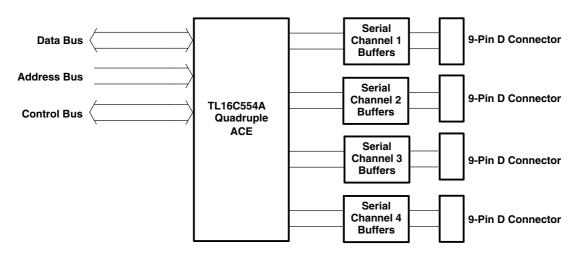

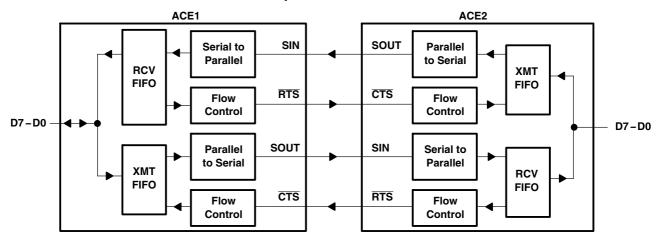

The TL16C554A is an enhanced quadruple version of the TL16C550C asynchronous-communications element (ACE). Each channel performs serial-to-parallel conversion on data characters received from peripheral devices or modems and parallel-to-serial conversion on data characters transmitted by the CPU. The complete status of each channel of the quadruple ACE can be read by the CPU at any time during operation. The information obtained includes the type and condition of the operation performed and any error conditions encountered.

The TL16C554A quadruple ACE can be placed in an alternate FIFO mode, which activates the internal FIFOs to allow 16 bytes (plus three bits of error data per byte in the receiver FIFO) to be stored in both receive and transmit modes. In the FIFO mode of operation, there is a selectable autoflow control feature that can significantly reduce software overhead and increase system efficiency by automatically controlling serial-data flow using RTS output and CTS input signals. All logic is on the chip to minimize system overhead and maximize system efficiency. Two terminal functions allow signaling of direct-memory access (DMA) transfers. Each ACE includes a programmable baud-rate generator that can divide the timing reference clock input by a divisor between 1 and 216-1.

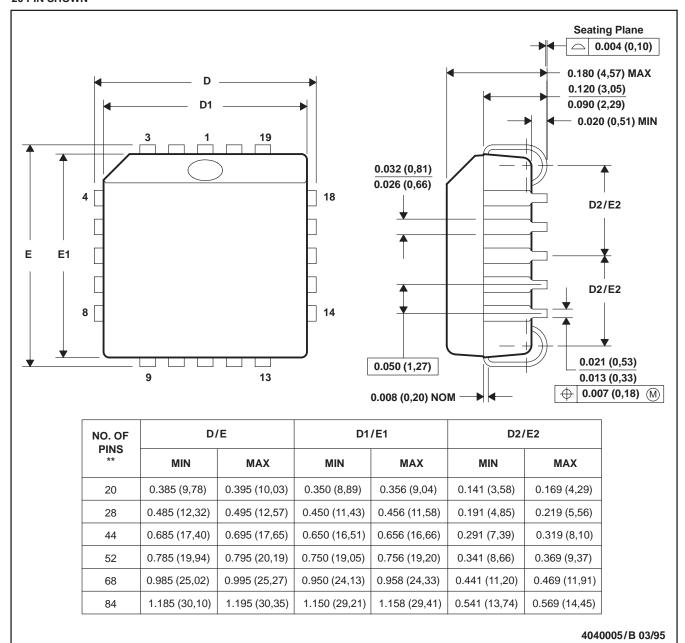

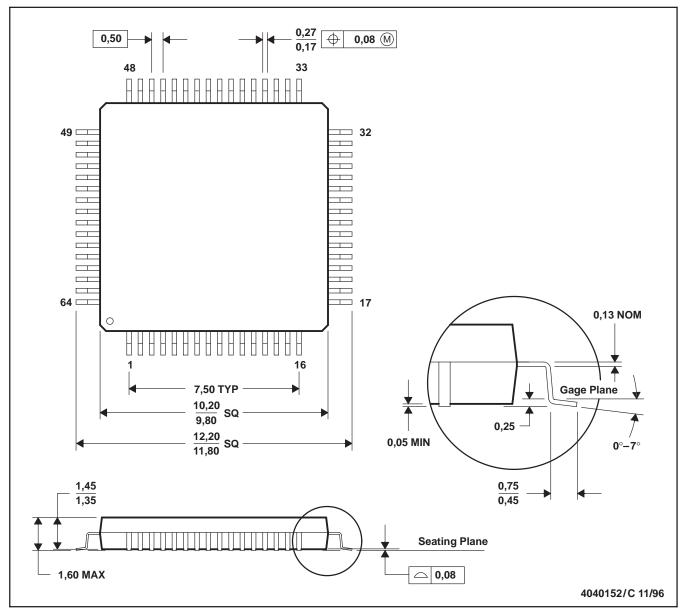

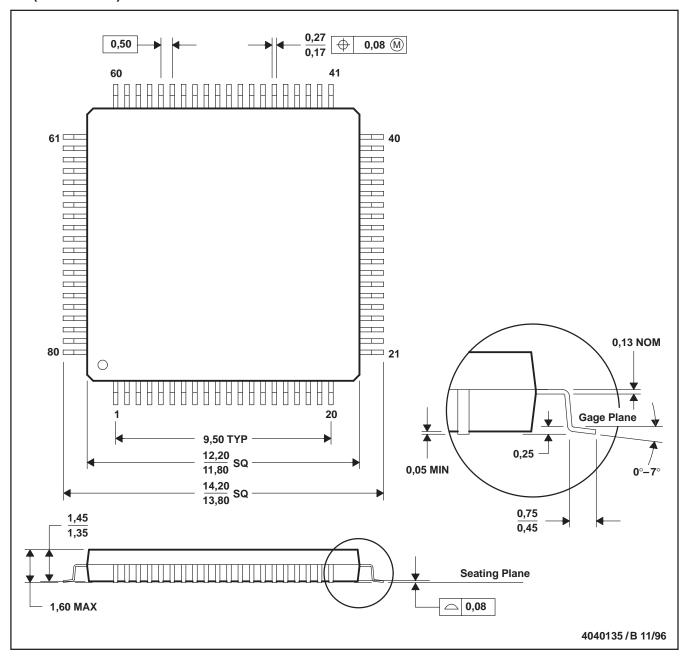

The TL16C554A is available in a 68-pin plastic-leaded chip-carrier (PLCC) FN package, 64-pin plastic quad flatpack (PQFP) PM package and in an 80-pin (TQFP) PN package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

NC - No internal connection

NC - No internal connection

## PN PACKAGE (TOP VIEW)

NC - No internal connection

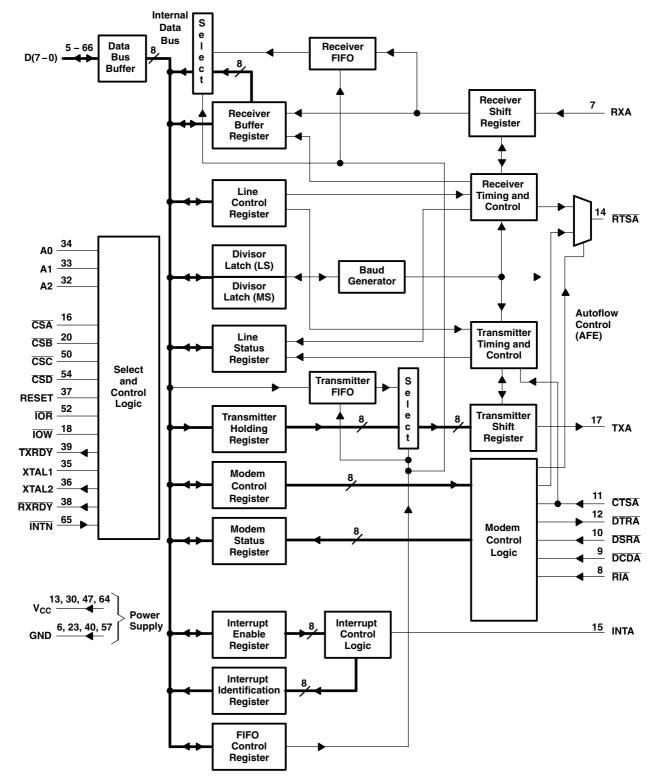

## functional block diagram (per channel)

NOTE A: Terminal numbers shown are for the FN package and channel A.

## **Terminal Functions**

| Т                         | ΓERMINA           | L                    |                   |     |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|---------------------------|-------------------|----------------------|-------------------|-----|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                      | FN<br>NO.         | PM<br>NO.            | PN<br>NO.         | I/O |                                                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| A0<br>A1<br>A2            | 34<br>33<br>32    | 22,<br>23,<br>24     | 48<br>47<br>46    | I   |                                                               | erminals. A0, A1, and A2 are three inputs used during read and write ect the ACE register to read or write.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| CSA, CSB,<br>CSC, CSD     | 16, 20,<br>50, 54 | 7, 11,<br>38, 42     | 28, 33,<br>68, 73 | I   | Chip select. Each channel.                                    | h chip select (CSx) enables read and write operations to its respective                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| CTSA, CTSB,<br>CTSC, CTSD | 11, 25,<br>45, 59 | 2, 16,<br>33, 47     | 23, 38,<br>63, 78 | I   | 4 (CTS) of the mothst CTS has character modern-status in      | $\overline{\text{IS}}$ is a modem status signal. Its condition can be checked by reading bit odem-status register. Bit 0 ( $\Delta$ CTS) of the modem-status register indicates anged state since the last read from the modem-status register. If the terrupt is enabled when $\overline{\text{CTS}}$ changes levels and the auto- $\overline{\text{CTS}}$ mode is interrupt is generated. $\overline{\text{CTS}}$ is also used in the auto- $\overline{\text{CTS}}$ mode to control |  |  |  |  |

| D7-D0                     | 66-68<br>1-5      | 53–60                | 15–11,<br>9–7     | I/O |                                                               | ata lines with 3-state outputs provide a bidirectional path for data, control, nation between the TL16C554A and the CPU. D0 is the least-significant                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| DCDA, DCDB,<br>DCDC, DCDD | 9, 27,<br>43, 61  | 18, 31,<br>49, 64    | 19,42,<br>59, 2   | I   |                                                               | ct. A low on $\overline{DCDx}$ indicates the carrier has been detected by the modem. this signal is checked by reading bit 7 of the modem-status register.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| DSRA, DSRB,<br>DSRC, DSRD | 10, 26,<br>44, 60 | 1, 17,<br>32, 48     | 22, 39,<br>62, 79 | I   | ,                                                             | OSRx is a modem-status signal. Its condition can be checked by reading e modem-status register. DSR has no effect on the transmit or receive                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DTRA, DTRB,<br>DTRC, DTRD | 12, 24,<br>46, 58 | 3, 15,<br>34, 46     | 24, 37,<br>64, 77 | 0   | is ready to establ<br>of<br>control register. I               | Data terminal ready. $\overline{\text{DTRx}}$ is an output that indicates to a modem or data set that the ACE is ready to establish communications. It is placed in the active state by setting the DTR bit of the modem-control register. $\overline{\text{DTRx}}$ is placed in the inactive state (high) either as a result of the master reset during loop-mode operation, or when clearing bit 0 ( $\overline{\text{DTR}}$ ) of the modem-control                                 |  |  |  |  |

| GND                       | 6, 23,<br>40, 57  | 14,<br>28, 45,<br>61 | 16, 36,<br>56, 76 |     | Signal and power                                              | r ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| INTN                      | 65                |                      | 6                 | I   | affects operation                                             | INTN operates in conjunction with bit 3 of the modem-status register and of the interrupts (INTA, INTB, INTC, and INTD) for the four universal ceiver/transceivers (UARTs) per the following table.                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                           |                   |                      |                   |     | INTN                                                          | OPERATION OF INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                           |                   |                      |                   |     | Brought low or allowed to float                               | Interrupts are enabled according to the state of OUT2 (MCR bit 3). When the MCR bit 3 is cleared, the 3-state interrupt output of that UART is in the high-impedance state. When the MCR bit 3 is set, the interrupt output of the UART is enabled.                                                                                                                                                                                                                                   |  |  |  |  |

|                           |                   |                      |                   |     | Brought high                                                  | Interrupts are always enabled, overriding the OUT2 enables.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| INTA, INTB,<br>INTC, INTD | 15, 21,<br>49, 55 | 6, 12,<br>37, 43     | 27, 34,<br>67, 74 | 0   | and inform the CF<br>an interrupt to be<br>only), transmitter | External interrupt output. The INTx outputs go high (when enabled by the interrupt register) and inform the CPU that the ACE has an interrupt to be serviced. Four conditions that cause an interrupt to be issued are: receiver error, receiver data available or timeout (FIFO mode only), transmitter holding register empty, and an enabled modem-status interrupt. The interrupt is disabled when it is serviced or as the result of a master reset.                             |  |  |  |  |

| IOR                       | 52                | 40                   | 70                | I   | Read strobe. A I external CPU bus                             | ow level on $\overline{\text{IOR}}$ transfers the contents of the selected register to the s.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| ĪOW                       | 18                | 9                    | 31                | ı   | Write strobe. IOV                                             | V allows the the CPU to write to the register selected by the address.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RESET                     | 37                | 27                   | 53                | I   |                                                               | en active, RESET clears most ACE registers and sets the state of various smitter output and the receiver input are disabled during reset time.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

SLLS509E - AUGUST 2001 - REVISED JUNE 2010

## **Terminal Functions (Continued)**

| TERMINAL                  |                   |                   |                   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------|-------------------|-------------------|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                      | FN<br>NO.         | PM<br>NO.         | PN<br>NO.         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RIA, RIB,<br>RIC, RID     |                   | 19, 30,<br>50, 63 | 18, 43,<br>58, 3  | I   | Ring detect indicator. A low on $\overline{\text{RIx}}$ indicates the modem has received a ring signal from the telephone line. The condition of this signal can be checked by reading bit 6 of the modem-status register.                                                                                                                                                                                                                |

| RTSA, RTSB,<br>RTSC, RTSD |                   | 5, 13,<br>36, 44  | 26, 35,<br>66, 75 | 0   | Request to send. When active, RTS informs the modem or data set that the ACE is ready to receive data. RTS is set to the active level by setting the RTS modem-control register bit, and is set to the inactive (high) level either as a result of a master reset, or during loop-mode operations, or by clearing bit 1 (RTS) of the MCR. In the auto-RTS mode, RTS is set to the inactive level by the receiver threshold-control logic. |

| RXA, RXB<br>RXC, RXD      | 7, 29,<br>41, 63  | 20, 29,<br>51, 62 | 17, 44,<br>57, 4  | I   | Serial input. RXx is a serial-data input from a connected communications device. During loopback mode, the RXx input is disabled from external connection and connected to the TXx output internally.                                                                                                                                                                                                                                     |

| RXRDY                     | 38                |                   | 54                | 0   | Receive ready. RXRDY goes low when the receive FIFO is full. It can be used as a single transfer or multitransfer.                                                                                                                                                                                                                                                                                                                        |

| TXA, TXB<br>TXC, TXD      | 17, 19,<br>51, 53 | 8, 10,<br>39, 41  | 29, 32,<br>69, 72 | 0   | Transmit outputs. TXx is a composite serial-data output connected to a communications device. TXA, TXB, TXC, and TXD are set to the marking (high) state as a result of reset.                                                                                                                                                                                                                                                            |

| TXRDY                     | 39                |                   | 55                | 0   | Transmit ready. TXRDY goes low when the transmit FIFO is full. It can be used as a single transfer or multitransfer function.                                                                                                                                                                                                                                                                                                             |

| V <sub>CC</sub>           | 13, 30,<br>47, 64 | 21, 35,<br>52     | 5, 25,<br>45, 65  |     | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                              |

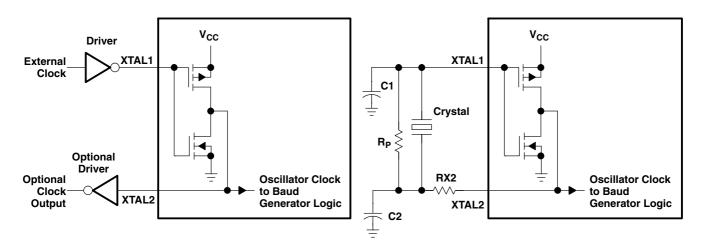

| XTAL1                     | 35                | 25                | 50                | I   | Crystal input 1 or external clock input. A crystal can be connected to XTAL1 and XTAL2 to utilize the internal oscillator circuit. An external clock can be connected to drive the internal-clock circuits.                                                                                                                                                                                                                               |

| XTAL2                     | 36                | 26                | 51                | 0   | Crystal output 2 or buffered clock output (see XTAL1).                                                                                                                                                                                                                                                                                                                                                                                    |

## absolute maximum ratings over free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1) |            | –0.5 V to 7 V                            |

|----------------------------------------------------|------------|------------------------------------------|

| Input voltage range at any input, V <sub>1</sub>   |            | 0.5 V to 7 V                             |

| Output voltage range, V <sub>O</sub>               |            | $-0.5 \text{ V to V}_{CC} + 3 \text{ V}$ |

| Continuous total-power dissipation at (or bel      | low) 70°C  |                                          |

| Operating free-air temperature range, TA: T        | TL16C554A  | 0°C to 70°C                              |

| Т                                                  | ΓL16C554AI | 40°C to 85°C                             |

| Storage temperature range, T <sub>stq</sub>        |            | 65°C to 150°C                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage levels are with respect to GND.

SLLS509E - AUGUST 2001 - REVISED JUNE 2010

## recommended operating conditions, standard voltage (5 V-nominal)

|                                                |                         | MIN  | NOM | MAX      | UNIT |

|------------------------------------------------|-------------------------|------|-----|----------|------|

| Supply voltage, V <sub>CC</sub>                |                         | 4.75 | 5   | 5.25     | V    |

| Clock high-level input voltage at XTAL         | 1, V <sub>IH(CLK)</sub> | 2    |     | $V_{CC}$ | V    |

| Clock low-level input voltage at XTAL          | , V <sub>IL(CLK)</sub>  | -0.5 |     | 8.0      | V    |

| High-level input voltage, V <sub>IH</sub>      |                         | 2    |     | $V_{CC}$ | V    |

| Low-level input voltage, V <sub>IL</sub>       |                         | -0.5 |     | 8.0      | V    |

| Clock frequency, f <sub>clock</sub>            |                         |      |     | 16       | MHz  |

| Operating free six temperature T               | TL16C554A               | 0    |     | 70       | °C   |

| Operating free-air temperature, T <sub>A</sub> | TL16C554AI              | -40  |     | 85       | °C   |

## electrical characteristics over recommended ranges of operating free-air temperature and supply voltage, standard voltage (5-V nominal) (unless otherwise noted)

|                              | PARAMETER                     | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                          | MIN | TYP† | MAX | UNIT |

|------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| V <sub>OH</sub> <sup>‡</sup> | High-level output voltage     | $I_{OH} = -1 \text{ mA}$                                                                                                                                                                                                                                                                                                                                 | 2.4 |      |     | V    |

| V <sub>OL</sub> ‡            | Low-level output voltage      | I <sub>OL</sub> = 1.6 mA                                                                                                                                                                                                                                                                                                                                 |     |      | 0.4 | V    |

| I <sub>Ikg</sub>             | Input leakage current         | $V_{CC} = 5.25 \text{ V},$ GND = 0,<br>$V_{I} = 0 \text{ to } 5.25 \text{ V},$ All other terminals floating                                                                                                                                                                                                                                              |     |      | ±10 | μΑ   |

| loz                          | High-impedance output current | $V_{CC} = 5.25 \text{ V},$ GND = 0, $V_{O} = 0 \text{ to } 5.25 \text{ V},$ Chip selected in write mode or chip deselected                                                                                                                                                                                                                               |     |      | ±20 | μΑ   |

| Icc                          | Supply current                | $\begin{array}{ll} V_{CC} = 5.25 \text{ V}, & T_A = 25^{\circ}\text{C}, \\ \text{RX, } \overline{\text{DSR}}, \overline{\text{DCD}}, \text{CTS, and } \overline{\text{RI}} \text{ at 2 V,} \\ \text{All other inputs at 0.8 V, } & \text{XTAL1 at 4 MHz,} \\ \text{No load on outputs,} & \text{Baud rate} = 50 \text{ kilobits per second} \end{array}$ |     |      | 50  | mA   |

| C <sub>i(XTAL1)</sub>        | Clock input capacitance       |                                                                                                                                                                                                                                                                                                                                                          |     | 15   | 20  | pF   |

| C <sub>o(XTAL2)</sub>        | Clock output capacitance      | $V_{CC} = 0$ , $V_{SS} = 0$ , all other terminals grounded,                                                                                                                                                                                                                                                                                              |     | 20   | 30  | рF   |

| C <sub>i</sub>               | Input capacitance             | $f = 1 \text{ MHz}, T_A = 25^{\circ}\text{C}$                                                                                                                                                                                                                                                                                                            |     | 6    | 10  | pF   |

| Co                           | Output capacitance            | ]                                                                                                                                                                                                                                                                                                                                                        |     | 10   | 20  | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>&</sup>lt;sup>‡</sup> These parameters apply for all outputs except XTAL2.

SLLS509E - AUGUST 2001 - REVISED JUNE 2010

## recommended operating conditions, low voltage (3.3-V nominal)

|                                                |                        | MIN   | NOM | MAX      | UNIT |

|------------------------------------------------|------------------------|-------|-----|----------|------|

| Supply voltage, V <sub>CC</sub>                |                        | 3     | 3.3 | 3.6      | V    |

| Clock high-level input voltage at XTAI         | , V <sub>IH(CLK)</sub> | 2     |     | $V_{CC}$ | V    |

| Clock low-level input voltage at XTAL          | V <sub>IL(CLK)</sub>   | -0.5  |     | 0.8      | V    |

| High-level input voltage, V <sub>IH</sub>      |                        | 2     |     | $V_{CC}$ | ٧    |

| Low-level input voltage, V <sub>IL</sub>       |                        | -0.5  |     | 8.0      | ٧    |

| Clock frequency, f <sub>clock</sub>            |                        |       |     | 16       | MHz  |

| Operating free six temperature T               | TL16C554A              | <br>0 | •   | 70       | °C   |

| Operating free-air temperature, T <sub>A</sub> | TL16C554AI             | -40   |     | 85       | °C   |

## electrical characteristics over recommended ranges of operating free-air temperature and supply voltage, low voltage (3.3-V nominal) (unless otherwise noted)

|                              | PARAMETER                     | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                          | MIN | TYP† | MAX | UNIT |

|------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| V <sub>OH</sub> <sup>‡</sup> | High-level output voltage     | $I_{OH} = -1 \text{ mA}$                                                                                                                                                                                                                                                                                                                                 | 2.4 |      |     | V    |

| V <sub>OL</sub> ‡            | Low-level output voltage      | I <sub>OL</sub> = 1.6 mA                                                                                                                                                                                                                                                                                                                                 |     |      | 0.4 | V    |

| I <sub>lkg</sub>             | Input leakage current         | $V_{CC} = 3.6 \text{ V},$ GND = 0,<br>$V_{I} = 0 \text{ to } 3.6 \text{ V},$ All other terminals floating                                                                                                                                                                                                                                                |     |      | ±10 | μА   |

| I <sub>OZ</sub>              | High-impedance output current | $V_{CC} = 3.6 \text{ V}, \qquad \qquad \text{GND} = 0,  V_O = 0 \text{ to } 3.6 \text{ V},$ Chip selected in write mode or chip deselected                                                                                                                                                                                                               |     |      | ±20 | μΑ   |

| Icc                          | Supply current                | $\begin{array}{lll} V_{CC} = 3.6 \text{ V}, & T_A = 25^{\circ}\text{C}, \\ \text{RX, } \overline{\text{DSR}}, \overline{\text{DCD}}, \text{CTS, and } \overline{\text{RI}} \text{ at 2 V,} \\ \text{All other inputs at 0.8 V, } & \text{XTAL1 at 4 MHz,} \\ \text{No load on outputs,} & \text{Baud rate} = 50 \text{ kilobits per second} \end{array}$ |     |      | 40  | mA   |

| C <sub>i(XTAL1)</sub>        | Clock input capacitance       |                                                                                                                                                                                                                                                                                                                                                          |     | 15   | 20  | pF   |

| C <sub>o(XTAL2)</sub>        | Clock output capacitance      | $V_{CC} = 0$ , $V_{SS} = 0$ , all other terminals grounded,                                                                                                                                                                                                                                                                                              |     | 20   | 30  | pF   |

| Ci                           | Input capacitance             | $f = 1 \text{ MHz}, T_A = 25^{\circ}\text{C}$                                                                                                                                                                                                                                                                                                            |     | 6    | 10  | pF   |

| Co                           | Output capacitance            | ]                                                                                                                                                                                                                                                                                                                                                        |     | 10   | 20  | pF   |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

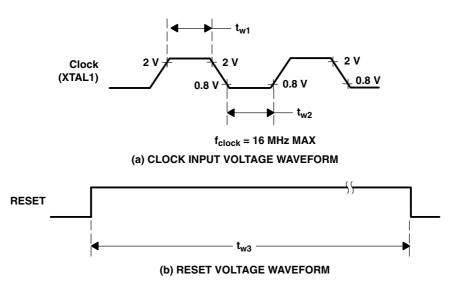

## clock timing requirements over recommended ranges of operating free-air temperature and supply voltage (see Figure 1)

|                 |                                             | MIN  | MAX | UNIT |

|-----------------|---------------------------------------------|------|-----|------|

| t <sub>w1</sub> | Pulse duration, clock high (external clock) | 31   |     | ns   |

| t <sub>w2</sub> | Pulse duration, clock low (external clock)  | 31   |     | ns   |

| t <sub>w3</sub> | Pulse duration, RESET                       | 1000 |     | ns   |

<sup>&</sup>lt;sup>‡</sup> These parameters apply for all outputs except XTAL2.

SLLS509E - AUGUST 2001 - REVISED JUNE 2010

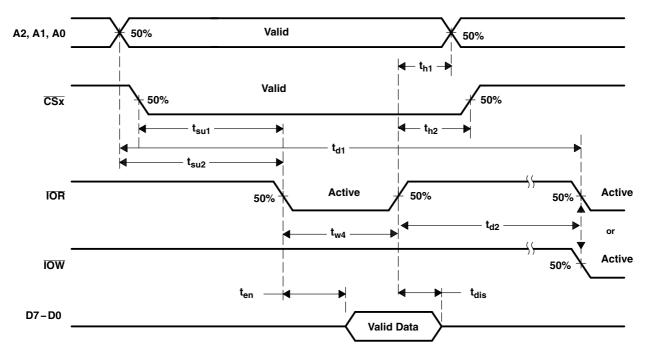

## read cycle timing requirements over recommended ranges of operating free-air temperature and supply voltage (see Figure 4)

|                  |                                                                                           | MIN | MAX | UNIT |

|------------------|-------------------------------------------------------------------------------------------|-----|-----|------|

| t <sub>w4</sub>  | Pulse duration, IOR low                                                                   | 75  |     | ns   |

| t <sub>su1</sub> | Setup time, $\overline{\text{CSx}}$ valid before $\overline{\text{IOR}}$ low (see Note 2) | 10  |     | ns   |

| t <sub>su2</sub> | Setup time, A2 – A0 valid before IOR low (see Note 2)                                     | 15  |     | ns   |

| t <sub>h1</sub>  | Hold time, A2 – A0 valid after IOR high (see Note 2)                                      | 0   |     | ns   |

| t <sub>h2</sub>  | Hold time, $\overline{\text{CSx}}$ valid after $\overline{\text{IOR}}$ high (see Note 2)  | 0   |     | ns   |

| t <sub>d1</sub>  | Delay time, $t_{su2} + t_{w4} + t_{d2}$ (see Note 3)                                      | 140 |     | ns   |

| t <sub>d2</sub>  | Delay time, IOR high to IOR or IOW low                                                    | 50  |     | ns   |

NOTES: 2. The internal address strobe is always active.

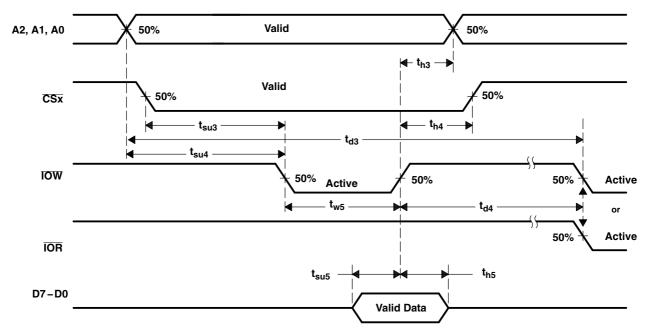

## write cycle timing requirements over recommended ranges of operating free-air temperature and supply voltage (see Figure 5)

|                  |                                                                     | MIN | MAX | UNIT |

|------------------|---------------------------------------------------------------------|-----|-----|------|

| t <sub>w5</sub>  | Pulse duration, <del>IOW</del> ↓                                    | 50  |     | ns   |

| t <sub>su3</sub> | Setup time, <del>CSx</del> valid before <del>IOW</del> (see Note 2) | 10  |     | ns   |

| t <sub>su4</sub> | Setup time, A2 – A0 valid before IOW↓ (see Note 2)                  | 15  |     | ns   |

| t <sub>su5</sub> | Setup time, D7 – D0 valid before <del>IOW</del> ↑                   | 10  |     | ns   |

| t <sub>h3</sub>  | Hold time, A2 – A0 valid after IOW↑ (see Note 2)                    | 5   |     | ns   |

| t <sub>h4</sub>  | Hold time, <del>CSx</del> valid after <del>IOW</del> ↑ (see Note 2) | 5   |     | ns   |

| t <sub>h5</sub>  | Hold time, D7 – D0 valid after IOW↑                                 | 25  |     | ns   |

| t <sub>d3</sub>  | Delay time, $t_{SU4} + t_{W5} + t_{d4}$                             | 120 |     | ns   |

| t <sub>d4</sub>  | Delay time, <del>IOW</del> ↑ to <del>IOW</del> or <del>IOR</del> ↓  | 55  |     | ns   |

NOTE 2: The internal address strobe is always active.

## read cycle switching characteristics over recommended ranges of operating free-air temperature and supply voltage, $C_1 = 100 \text{ pF}$ (see Note 4 and Figure 4)

|                  | PARAMETER                                      | MIN | MAX | UNIT |

|------------------|------------------------------------------------|-----|-----|------|

| t <sub>en</sub>  | Enable time, <del>IOR</del> ↓ to D7 – D0 valid |     | 30  | ns   |

| t <sub>dis</sub> | Disable time, IOR↑ to D7 – D0 released         | 0   | 20  | ns   |

NOTE 4:  $V_{OL}$  and  $V_{OH}$  (and the external loading) determine the charge and discharge time.

<sup>3.</sup> In the FIFO mode, t<sub>d1</sub> = 425 ns (min) between reads of the receiver FIFO and the status registers (interrupt-identification register and line-status register).

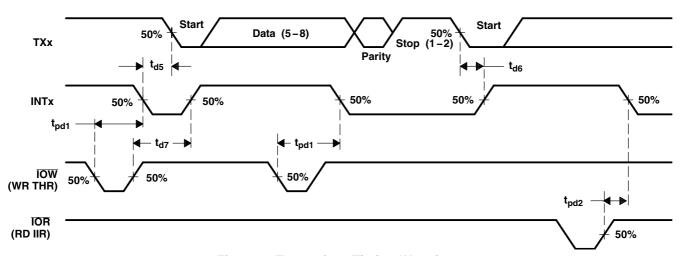

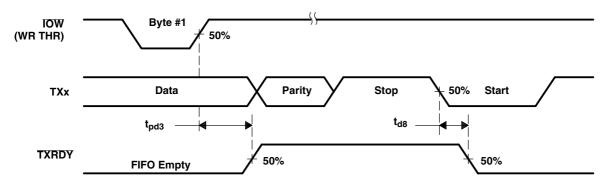

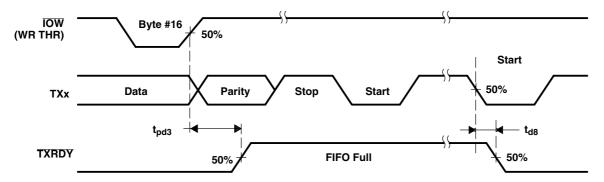

## transmitter switching characteristics over recommended ranges of operating free-air temperature and supply voltage (see Figures 6, 7, and 8)

|                  | PARAMETER                                                  | TEST CONDITIONS         | MIN | MAX | UNIT           |

|------------------|------------------------------------------------------------|-------------------------|-----|-----|----------------|

| t <sub>d5</sub>  | Delay time, INTx↓ to TXx↓ at start                         | See Note 7              | 8   | 24  | RCLK<br>cycles |

| t <sub>d6</sub>  | Delay time, TXx↓ at start to INTx↑                         | See Note 5              | 8   | 8   | RCLK<br>cycles |

| t <sub>d7</sub>  | Delay time, <del>IOW</del> high or low (WR THR) to INTx↑   | See Note 5              | 16  | 32  | RCLK<br>cycles |

| t <sub>d8</sub>  | Delay time, TXx↓ at start to TXRDY↓                        | C <sub>L</sub> = 100 pF |     | 8   | RCLK<br>cycles |

| t <sub>pd1</sub> | Propagation delay time, <del>IOW</del> (WR THR)↓ to INTx↓  | C <sub>L</sub> = 100 pF |     | 35  | ns             |

| t <sub>pd2</sub> | Propagation delay time, <del>IOR</del> (RD IIR)↑ to INTx↓  | C <sub>L</sub> = 100 pF |     | 30  | ns             |

| t <sub>pd3</sub> | Propagation delay time, <del>IOW</del> (WR THR)↑ to TXRDY↑ | C <sub>L</sub> = 100 pF |     | 50  | ns             |

NOTE 5: If the transmitter interrupt delay is active, this delay is lengthened by one character time minus the last stop-bit time.

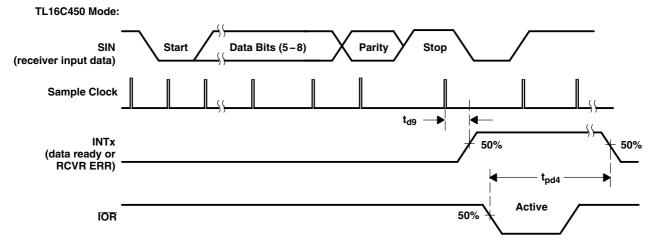

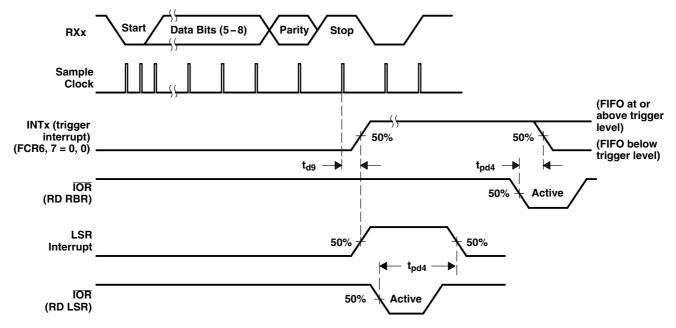

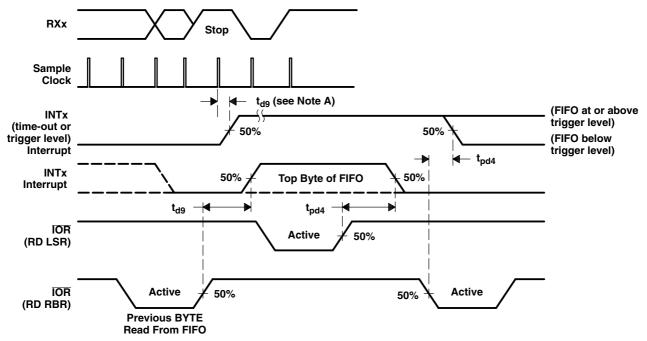

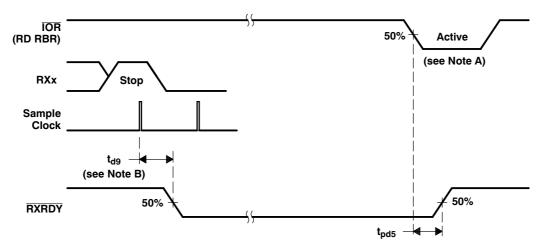

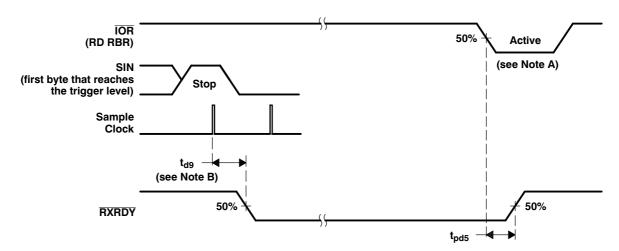

## receiver switching characteristics over recommended ranges of operating free-air temperature and supply voltage (see Figures 9 through 13)

|                  | PARAMETER                                                                                                         | TEST CONDITIONS                        | MIN | MAX | UNIT          |

|------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|-----|---------------|

| t <sub>d9</sub>  | Delay time, stop bit to INTx $\uparrow$ or stop bit to $\overline{RXRDY} \downarrow$ or read RBR to set interrupt | See Note 6                             |     | 1   | RCLK<br>cycle |

| t <sub>pd4</sub> | Propagation delay time, Read RBR/LSR to INTx↓/LSR interrupt↓                                                      | C <sub>L</sub> = 100 pF,<br>See Note 7 |     | 40  | ns            |

| t <sub>pd5</sub> | Propagation delay time, <del>IOR</del> RCLK↓ to RXRDY↑                                                            | See Note 7                             |     | 30  | ns            |

- NOTES: 6. The receiver data available indicator, the overrun error indicator, the trigger level interrupts, and the active RXRDY indicator are delayed three RCLK (internal receiver timing clock) cycles in the FIFO mode (FCR0 = 1). After the first byte has been received, status indicators (PE, FE, BI) are delayed three RCLK cycles. These indicators are updated immediately for any further bytes received after IOR goes active for a read from the RBR register. There are eight RCLK cycle delays for trigger change level interrupts.

- 7. RCLK and baudout are internal signals derived from divisor latches LSB (DLL) and MSB (DLM) and input clock.

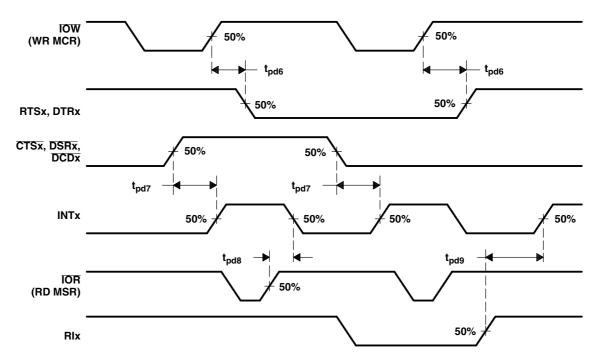

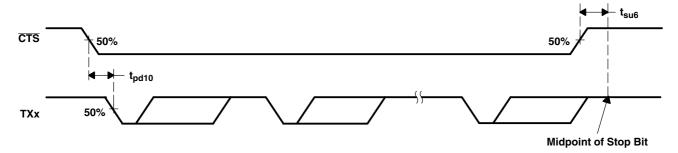

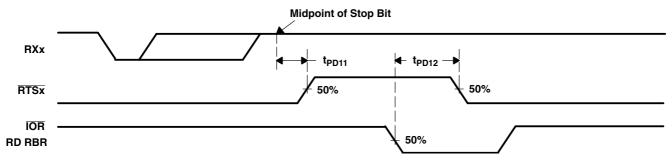

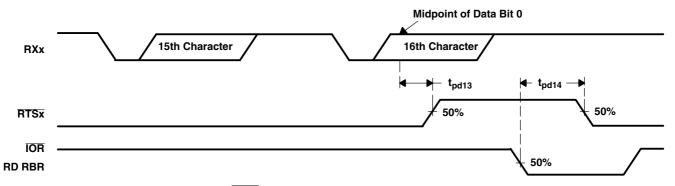

## modem control switching characteristics over recommended ranges of operating free-air temperature and supply voltage, $C_L$ = 100 pF (see Figures 14, 15, 16, and 17)

|                   | PARAMETER                                                                                                                                                                       | MIN | MAX | UNIT              |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------|

| t <sub>pd6</sub>  | Propagation delay time, <del>IOW</del> (WR MCR)↑ to <del>RTSx,</del> <del>DTRx</del> ↑                                                                                          |     | 50  | ns                |

| t <sub>pd7</sub>  | Propagation delay time, modem input $\overline{\text{CTSx}}$ , $\overline{\text{DSRx}}$ , and $\overline{\text{DCDx}} \downarrow \uparrow$ to $\overline{\text{INTx}} \uparrow$ |     | 30  | ns                |

| t <sub>pd8</sub>  | Propagation delay time, <del>IOR</del> (RD MSR)↑ to interrupt↓                                                                                                                  |     | 35  | ns                |

| t <sub>pd9</sub>  | Propagation delay time, RIx↑ to INTx↑                                                                                                                                           |     | 30  | ns                |

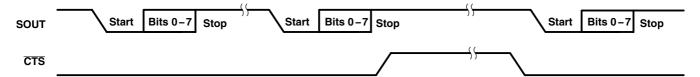

| t <sub>pd10</sub> | Propagation delay time, CTS low to SOUT↓ (See Note 7)                                                                                                                           |     | 24  | baudout<br>cycles |

| t <sub>su6</sub>  | Setup time CTS high to midpoint of Tx stop bit                                                                                                                                  |     | 2   | baudout<br>cycles |

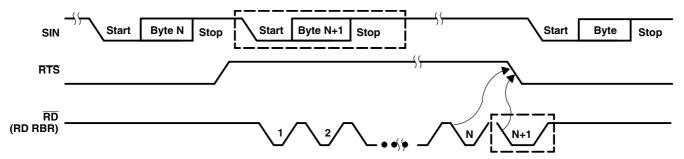

| t <sub>pd11</sub> | Propagation delay time, RCV threshold byte to RTS↑                                                                                                                              |     | 2   | baudout<br>cycles |

| t <sub>pd12</sub> | Propagation delay time, <del>IOR</del> (RD RBR) low (read of last byte in receive FIFO) to <del>RTS</del> ↓                                                                     |     | 2   | baudout<br>cycles |

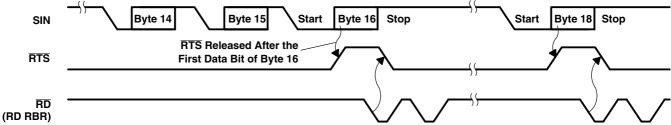

| t <sub>pd13</sub> | Propagation delay time, first data bit of 16 <sup>th</sup> character to RTS↑                                                                                                    |     | 2   | baudout<br>cycles |

| t <sub>pd14</sub> | Propagation delay time, <del>IOR</del> (RD RBR) low to <del>RTS</del> ↓                                                                                                         |     | 2   | baudout<br>cycles |

7. RCLK and baudout are internal signals derived from divisor latches LSB (DLL) and MSB (DLM) and input clock.

Figure 1. Clock Input and RESET Voltage Waveforms

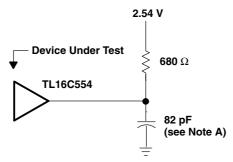

NOTE A: This includes scope and jig capacitance.

Figure 2. Output Load Circuit

**Figure 3. Basic Test Configuration**

Figure 4. Read Cycle Timing Waveforms

**Figure 5. Write Cycle Timing Waveforms**

**Figure 6. Transmitter Timing Waveforms**

Figure 7. Transmitter Ready Mode 0 Timing Waveforms

Figure 8. Transmitter Ready Mode 1 Timing Waveforms

**Figure 9. Receiver Timing Waveforms**

Figure 10. Receiver FIFO First Byte (Sets RDR) Waveforms

NOTE A: This is the reading of the last byte in the FIFO.

Figure 11. Receiver FIFO After First Byte (After RDR Set) Waveforms

NOTES: A. This is the reading of the last byte in the FIFO.

B. If FCR0 = 1, then  $t_{d9}$  = 3 RCLK cycles. For a time-out interrupt,  $t_{d9}$  = 8 RCLK cycles.

Figure 12. Receiver Ready Mode 0 Timing Waveforms

NOTES: A. This is the reading of the last byte in the FIFO.

B. If FCR0 = 1,  $t_{d9}$  = 3 RCLK cycles. For a trigger change level interrupt,  $t_{d9}$  = 8 RCLK.

Figure 13. Receiver Ready Mode 1 Timing Waveforms

**Figure 14. Modem Control Timing Waveforms**

Figure 15. CTS and TX Autoflow Control Timing (Start and Stop) Waveforms

Figure 16. Auto-RTS Timing for RCV Threshold of 1, 4, or 8 Waveforms

Figure 17. Auto-RTS Timing for RCV Threshold of 14 Waveforms

#### PRINCIPLES OF OPERATION

Three types of information are stored in the internal registers used in the ACE: control, status, and data. Mnemonic abbreviations for the registers are shown in Table 1. Table 2 defines the address location of each register and whether it is read only, write only, or read writable.

**Table 1. Internal Register Mnemonic Abbreviations**

| CONTROL                   | MNEMONIC | STATUS                | MNEMONIC | DATA                         | MNEMONIC |

|---------------------------|----------|-----------------------|----------|------------------------------|----------|

| Line-control register     | LCR      | Line-status register  | LSR      | Receiver-buffer register     | RBR      |

| FIFO-control register     | FCR      | Modem-status register | MSR      | Transmitter-holding register | THR      |

| Modem-control register    | MCR      |                       |          |                              |          |

| Divisor-latch LSB         | DLL      |                       |          |                              |          |

| Divisor-latch MSB         | DLM      |                       |          |                              |          |

| Interrupt enable register | IER      |                       |          |                              |          |

Table 2. Register Selection<sup>†</sup>

| DLAB‡ | A2§ | A1§ | A0§ | READ MODE                         | WRITE MODE                   |

|-------|-----|-----|-----|-----------------------------------|------------------------------|

| 0     | 0   | 0   | 0   | Receiver-buffer register          | Transmitter-holding register |

| 0     | 0   | 0   | 1   |                                   | Interrupt-enable register    |

| Х     | 0   | 1   | 0   | Interrupt-identification register | FIFO-control register        |

| Х     | 0   | 1   | 1   |                                   | Line-control register        |

| Х     | 1   | 0   | 0   |                                   | Modem-control register       |

| Х     | 1   | 0   | 1   | Line-status register              |                              |

| Х     | 1   | 1   | 0   | Modem-status register             |                              |

| Х     | 1   | 1   | 1   | Scratchpad register               | Scratchpad register          |

| 1     | 0   | 0   | 0   |                                   | LSB divisor-latch            |

| 1     | 0   | 0   | 1   |                                   | MSB divisor-latch            |

X = irrelevant, 0 = low level, 1 = high level

Individual bits within the registers with the bit number in parenthesis are referred to by the register mnemonic. For example, LCR7 refers to line-control register bit 7. The transmitter-buffer register and the receiver-buffer register are data registers that hold from five to eight bits of data. If less than eight data bits are transmitted, data is right-justified to the LSB. Bit 0 of a data word is always the first serial-data bit received and transmitted. The ACE data registers are double buffered (TL16450 mode) or FIFO buffered (FIFO mode) so that read and write operations can be performed when the ACE is performing the parallel-to-serial or serial-to-parallel conversion.

<sup>†</sup> The serial channel is accessed when either  $\overline{\text{CSA}}$  or  $\overline{\text{CSD}}$  is low.

<sup>&</sup>lt;sup>‡</sup> DLAB is the divisor-latch access bit, located in bit 7 of the LCR.

<sup>§</sup> A2-A0 are device terminals.

## accessible registers

The system programmer, using the CPU, has access to and control over any of the ACE registers that are summarized in Table 1. These registers control ACE operations, receive data, and transmit data. Descriptions of these registers follow Table 3.

**Table 3. Summary of Accessible Registers**

| ADDRES         | REGISTER            |                                           |                                             |                                           | REGISTI                            | ER ADDRESS                                        | 3                                             |                                                             |                                                 |

|----------------|---------------------|-------------------------------------------|---------------------------------------------|-------------------------------------------|------------------------------------|---------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------|-------------------------------------------------|

| S              | MNEMONIC            | BIT 7                                     | BIT 6                                       | BIT 5                                     | BIT 4                              | BIT 3                                             | BIT 2                                         | BIT 1                                                       | BIT 0                                           |

| 0              | RBR<br>(read only)  | Data Bit 7<br>(MSB)                       | Data Bit 6                                  | Data Bit 5                                | Data<br>Bit 4                      | Data Bit 3                                        | Data Bit 2                                    | Data Bit 1                                                  | Data Bit 0<br>(LSB)                             |

| 0              | THR<br>(write only) | Data Blt 7                                | Data Blt 6                                  | Data Blt 5                                | Data<br>Blt 4                      | Data Blt 3                                        | Data Blt 2                                    | Data Blt 1                                                  | Data Blt 0                                      |

| 0†             | DLL                 | Bit 7                                     | Bit 6                                       | Bit 5                                     | Bit 4                              | Bit 3                                             | Bit 2                                         | Bit 1                                                       | Bit 0                                           |

| 1 <sup>†</sup> | DLM                 | Bit 15                                    | Bit 14                                      | Bit 13                                    | Bit 12                             | Bit 11                                            | Bit 10                                        | Bit 9                                                       | Bit 8                                           |

| 1              | IER                 | 0                                         | 0                                           | 0                                         | 0                                  | (EDSSI)<br>Enable<br>modem<br>status<br>interrupt | (ERLSI) Enable receiver line status interrupt | (ETBEI) Enable transmitter holding register empty interrupt | (ERBI) Enable received data available interrupt |

| 2              | FCR<br>(write only) | Receiver<br>Trigger<br>(MSB)              | Receiver<br>Trigger<br>(LSB)                | Reserved                                  | Reserved                           | DMA<br>mode<br>select                             | Transmit<br>FIFO reset                        | Receiver<br>FIFO reset                                      | FIFO Enable                                     |

| 2              | IIR<br>(read only)  | FIFOs<br>Enabled <sup>‡</sup>             | FIFOs<br>Enabled <sup>‡</sup>               | 0                                         | 0                                  | Interrupt<br>ID Bit (3)‡                          | Interrupt ID<br>Bit (2)                       | Interrupt ID<br>Bit (1)                                     | 0 If interrupt pending                          |

| 3              | LCR                 | (DLAB) Divisor latch access bit           | Set break                                   | Stick parity                              | (EPS)<br>Even-<br>parity<br>select | (PEN)<br>Parity<br>enable                         | (STB)<br>Number of<br>stop bits               | (WLSB1)<br>Word-length<br>select bit 1                      | (WLSB0)<br>Word-length<br>select bit 0          |

| 4              | MCR                 | 0                                         | 0                                           | Autoflow<br>control<br>enable<br>(AFE)    | Loop                               | OUT2<br>Enable<br>external<br>interrupt<br>(INT)  | Reserved                                      | (RTS)<br>Request to<br>send                                 | (DTR) Data<br>terminal<br>ready                 |

| 5              | LSR                 | Error in<br>receiver<br>FIFO <sup>‡</sup> | (TEMT)<br>Transmitter<br>registers<br>empty | (THRE) Transmitter holding register empty | (BI)<br>Break<br>interrupt         | (FE)<br>Framing<br>error                          | (PE)<br>Parity error                          | (OE)<br>Overrun error                                       | (DR)<br>Data ready                              |

| 6              | MSR                 | (DCD) Data carrier detect                 | (RI)<br>Ring<br>indicator                   | (DSR)<br>Data set<br>ready                | (CTS)<br>Clear to<br>send          | (ΔDCD) Delta data carrier detect                  | (TERI)<br>Trailing<br>edge ring<br>indicator  | (∆DSR)<br>Delta data<br>set ready                           | (ΔCTS)<br>Delta<br>clear to send                |

| 7              | SCR                 | Bit 7                                     | Bit 6                                       | Bit 5                                     | Bit 4                              | Bit 3                                             | Bit 2                                         | Bit 1                                                       | Bit 0                                           |

<sup>†</sup> DLAB = 1

<sup>&</sup>lt;sup>‡</sup> These bits are always 0 when FIFOs are disabled.

#### PRINCIPLES OF OPERATION

### FIFO-control register (FCR)

The FCR is a write-only register at the same location as the IIR. It enables the FIFOs, sets the trigger level of the receiver FIFO, and selects the type of DMA signalling.

- Bit 0: FCR0 enables the transmit and receive FIFOs. All bytes in both FIFOs can be cleared by clearing FCR0. Data is cleared automatically from the FIFOs when changing from the FIFO mode to the TL16C450 mode (see FCR bit 0) and vice versa. Programming of other FCR bits is enabled by setting FCR0.

- Bit 1: When set, FCR1 clears all bytes in the receiver FIFO and resets its counter. This does not clear the shift register.

- Bit 2: When set, FCR2 clears all bytes in the transmit FIFO and resets the counter. This does not clear the shift register.

- Bit 3: When set, FCR3 changes RXRDY and TXRDY from mode 0 to mode 1 if FCR0 is set.

- Bits 4 and 5: FCR4 and FCR5 are reserved for future use.

- Bits 6 and 7: FCR6 and FCR7 set the trigger level for the receiver FIFO interrupt and the auto-RTS flow control (see Table 4).

BIT **RECEIVER FIFO** TRIGGER LEVEL (BYTES) 7 6 0 0 01 1 04 0 0 1 08 1 14

Table 4. Receiver FIFO Trigger Level

## FIFO interrupt mode operation

The following receiver status occurs when the receiver FIFO and the receiver interrupts are enabled:

- 1. LSR0 is set when a character is transferred from the shift register to the receiver FIFO. When the FIFO is empty, it is reset.

- 2. IIR = 06 receiver line status interrupt has higher priority than the receive data available interrupt IIR = 04.

- 3. Receive data available interrupt is issued to the CPU when the programmed trigger level is reached by the FIFO. As soon as the FIFO drops below its programmed trigger level, it is cleared.

- 4. IIR = 04 (receive data available indicator) also occurs when the FIFO reaches its trigger level. It is cleared when the FIFO drops below the programmed trigger level.

#### PRINCIPLES OF OPERATION

#### FIFO interrupt mode operation (continued)

The following receiver FIFO character time-out status occurs when receiver FIFO and the receiver interrupts are enabled.

- 1. When the following conditions exist, a FIFO character time-out interrupt occurs:

- a. Minimum of one character in FIFO

- b. No new serial characters have been received for at least four character times. At 300 baud and 12-bit characters, the FIFO time-out interrupt causes a latency of 160 ms maximum from received character to interrupt generation.

- c. The receive FIFO has not been read for at least four character times.

- 2. By using the XTAL1 input for a clock signal, the character times can be calculated. The delay is proportional to the baud rate.

- 3. The time-out timer is reset after the CPU reads the receiver FIFO or after a new character is received. This occurs when there has been no time-out interrupt.

- 4. A time-out interrupt is cleared and the timer is reset when the CPU reads a character from the receiver FIFO.

Transmit interrupts occurs as follows when the transmitter and transmit FIFO interrupts are enabled (FCR0 =1, IER1 = 1).

- 1. When the transmitter FIFO is empty, the transmitter holding register interrupt (IIR = 02) occurs. The interrupt is cleared when the transmitter holding register is written to or the IIR is read. One to sixteen characters can be written to the transmit FIFO when servicing this interrupt.

- 2. The transmitter FIFO empty indicators are delayed one character time minus the last stop-bit time whenever the following occurs:

THRE = 1, and there have not been at least two bytes in transmit FIFO since the last THRE = 1. The first transmitter interrupt comes immediately after changing FCRO, assuming the interrupt is enabled.

Receiver FIFO trigger level and character time-out interrupts have the same priority as the receive data available interrupt. The transmitter holding register empty interrupt has the same priority as the transmitter FIFO empty interrupt.

## FIFO polled mode operation

When the FIFOs are enabled and all interrupts are disabled, the device is in the FIFO polled mode.

In the FIFO polled mode, there is no time-out condition indicated or trigger level reached. However, the receive and transmit FIFOs still have the capability of holding characters. The LSR must be read to determine the ACE status.

#### PRINCIPLES OF OPERATION

### interrupt-enable register (IER)

The IER independently enables the four serial channel interrupt sources that activate the interrupt (INTA, B, C, D) output. All interrupts are disabled by clearing IER0 – IER3 of the IER. Interrupts are enabled by setting the appropriate bits of the IER. Disabling the interrupt system inhibits the IIR and the active (high) interrupt output. All other system functions operate in their normal manner, including the setting of the LSR and MSR. The contents of the IER are shown in Table 3 and described in the following bulleted list:

- Bit 0: When IER0 is set, IER0 enables the received data available interrupt and the timeout interrupts in the FIFO mode.

- Bit 1: When IER1 is set, the transmitter holding register empty interrupt is enabled.

- Bit 2: When IER2 is set, the receiver line status interrupt is enabled.

- Bit 3: When IER3 is set, the modem-status interrupt is enabled.

- Bits 4 7: IER4 IER7. These four bits of the IER are cleared.

#### interrupt-identification register (IIR)

In order to minimize software overhead during data character transfers, the serial channel prioritizes interrupts into four levels as follows:

- Priority 1 Receiver line status (highest priority)

- Priority 2 Receiver data ready or receiver character timeout

- Priority 3 Transmitter holding register empty

- Priority 4-Modem status (lowest priority)

The IIR stores information indicating that a prioritized interrupt is pending and the type of interrupt. The IIR indicates the highest priority interrupt pending. The contents of the IIR are indicated in Table 5.

**Table 5. Interrupt Control Functions**

| INTERRUPT IDENTIFICATION REGISTER |       |       | N     | INTERRUPT SET AND RESET FUNCTIONS |                              |                                                                                                                                                                      |                                                          |  |

|-----------------------------------|-------|-------|-------|-----------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

| BIT 3                             | BIT 2 | BIT 1 | BIT 0 | PRIORITY<br>LEVEL                 | INTERRUPT TYPE               | INTERRUPT SOURCE                                                                                                                                                     | INTERRUPT<br>RESET CONTROL                               |  |

| 0                                 | 0     | 0     | 1     | _                                 | None                         | None                                                                                                                                                                 | _                                                        |  |

| 0                                 | 1     | 1     | 0     | First                             | Receiver line status         | OE, PE, FE, or BI                                                                                                                                                    | LSR read                                                 |  |

| 0                                 | 1     | 0     | 0     | Second                            | Received data available      | Receiver data available or trigger level reached                                                                                                                     | RBR read until FIFO drops below the trigger level        |  |

| 1                                 | 1     | 0     | 0     | Second                            | Character time-out indicator | No characters have been removed from or input to the receiver FIFO during the last four character times, and there is at least one character in it during this time. | RBR read                                                 |  |

| 0                                 | 0     | 1     | 0     | Third                             | THRE                         | THRE                                                                                                                                                                 | IIR read (if THRE is the interrupt source), or THR write |  |

| 0                                 | 0     | 0     | 0     | Fourth                            | Modem status                 | CTS, DSR, RI, or DCD                                                                                                                                                 | MSR read                                                 |  |

### interrupt-identification register (IIR) (continued)

- Bit 0: IIR0 indicates whether an interrupt is pending. When IIR0 is cleared, an interrupt is pending.

- Bits 1 and 2: IIR1 and IIR2 identify the highest priority interrupt pending as indicated in Table 5.

- Bit 3: IIR3 is always cleared in the TL16C450 mode. This bit, along with bit 2, is set when in the FIFO mode and a character time-out interrupt is pending.

- Bits 4 and 5: IIR4 and IIR5 are always cleared.

- Bits 6 and 7: IIR6 and IIR7 are set when FCR0 = 1.

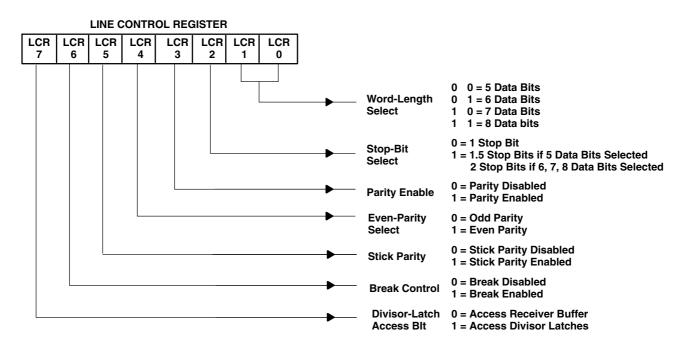

#### line-control register (LCR)

The format of the data character is controlled by LCR. LCR may be read. Its contents are described in the following bulleted list and shown in Figure 18.

- Bits 0 and 1: LCR0 and LCR1 are word-length select bits. These bits program the number of bits in each serial character and are shown in Figure 18.

- Bit 2: LCR2 is the stop-bit select bit. This bit specifies the number of stop bits in each transmitted character. The receiver always checks for one stop bit.

- Bit 3: LCR3 is the parity-enable bit. When LCR3 is set, a parity bit between the last data word bit and the stop bit is generated and checked.

- Bit 4: LCR4 is the even-parity select bit. When this bit is set and parity is enabled (LCR3 is set), even parity is selected. When this bit is cleared and parity is enabled, odd parity is selected.

- Bit 5: LCR5 is the stick-parity bit. When parity is enabled (LCR3 is set) and this bit is set, the transmission and reception of a parity bit is placed in the opposite state from the value of LCR4. This forces parity to a known state and allows the receiver to check the parity bit in a known state.

- Bit 6: LCR6 is a break-control bit. When this bit is set, the serial outputs TXx are forced to the spacing state (low). The break-control bit acts only on the serial output and does not affect the transmitter logic. If the following sequence is used, no invalid characters are transmitted because of the break.

- Step 1. Load a zero byte in response to the transmitter holding register empty (THRE) status indicator.

- Step 2. Set the break in response to the next THRE status indicator.

- Step 3. Wait for the transmitter to be idle when transmitter empty status signal is set (TEMT = 1); then clear the break when the normal transmission has to be restored.

- Bit 7: LCR7 is the divisor-latch access bit (DLAB) bit. This bit must be set to access the divisor latches DLL

and DLM of the baud-rate generator during a read or write operation. LCR7 must be cleared to access the

receiver-buffer register, the transmitter-holding register, or the interrupt-enable register.

#### line-control register (LCR) (continued)

Figure 18. Line-Control Register Contents

#### line-status register (LSR)

The LSR is a single register that provides status indicators. The LSR shown in Table 6 is described in the following bulleted list:

- Bit 0: LSR0 is the data ready (DR) bit. Data ready is set when an incoming character is received and transferred to the receiver-buffer register or to the FIFO. LSR0 is cleared by a CPU read of the data in the receiver-buffer register or in the FIFO.

- Bit 1: LSR1 is the overrun error (OE) bit. An overrun error indicates that data in the receiver-buffer register is not read by the CPU before the next character is transferred to the receiver-buffer register, therefore overwriting the previous character. The OE indicator is cleared whenever the CPU reads the contents of the LSR. An overrun error occurs in the FIFO mode after the FIFO is full and the next character is completely received. The overrun error is detected by the CPU on the first LSR read after it occurs. The character in the shift register is not transferred to the FIFO, but it is overwritten.

- Bit 2: LSR2 is the parity error (PE) bit. A parity error indicates that the received data character does not

have the correct parity as selected by LCR3 and LCR4. The PE bit is set upon detection of a parity error

and is cleared when the CPU reads the contents of the LSR. In the FIFO mode, the parity error is associated

with a particular character in the FIFO. LSR2 reflects the error when the character is at the top of the FIFO.

- Bit 3: LSR3 is the framing error (FE) bit. A framing error indicates that the received character does not have

a valid stop bit. LSR3 is set when the stop bit following the last data bit or parity bit is detected as a zero

bit (spacing level). The FE indicator is cleared when the CPU reads the contents of the LSR. In the FIFO

mode, the framing error is associated with a particular character in the FIFO. LSR3 reflects the error when

the character is at the top of the FIFO.

### line-status register (LSR) (continued)

Bit 4: LSR4 is the break interrupt (BI) bit. Break interrupt is set when the received data input is held in the spacing (low) state for longer than a full word transmission time (start bit + data bits + parity + stop bits). The BI indicator is cleared when the CPU reads the contents of the LSR. In the FIFO mode, this is associated with a particular character in the FIFO. LSR2 reflects the BI when the break character is at the top of the FIFO. The error is detected by the CPU when its associated character is at the top of the FIFO during the first LSR read. Only one zero character is loaded into the FIFO when BI occurs.

LSR1 - LSR4 are the error conditions that produce a receiver line status interrupt (priority 1 interrupt in the interrupt-identification register) when any of the conditions are detected. This interrupt is enabled by setting IER2 in the interrupt-enable register.

- Bit 5: LSR5 is the transmitter holding register empty (THRE) bit. THRE indicates that the ACE is ready to accept a new character for transmission. The THRE bit is set when a character is transferred from the transmitter holding register (THR) to the transmitter shift register (TSR). LSR5 is cleared when the CPU loads THR. LSR5 is not cleared by a CPU read of the LSR. In the FIFO mode, this bit is set when the transmit FIFO is empty, and it is cleared when one byte is written to the transmit FIFO. When the THRE interrupt is enabled by IER1, THRE causes a priority 3 interrupt in the IIR. If THRE is the interrupt source indicated by IIR, INTRPT is cleared by a read of the IIR.

- Bit 6: LSR6 is the transmitter register empty (TEMT) bit. TEMT is set when both THR and TSR are empty. LSR6 is cleared when a character is loaded into THR, and remains low until the character is transferred out of TXx. TEMT is not cleared by a CPU read of the LSR. In the FIFO mode, this bit is set when both the transmitter FIFO and shift register are empty.

- Bit 7: LSR7 is the receiver FIFO error bit. The LSR7 bit is cleared in the TL16C450 mode (see FCR bit 0). In the FIFO mode, it is set when at least one of the following data errors is in the FIFO: parity error, framing error, or break interrupt indicator. It is cleared when the CPU reads the LSR, unless there are subsequent errors in the FIFO.

#### NOTE

The LSR may be written. However, this function is intended only for factory test. It should be considered as read only by applications software.

**Table 6. Line-Status Register Blts**

| LSR BITS                                       | 1             | 0                |

|------------------------------------------------|---------------|------------------|

| LSR0 data ready (DR)                           | Ready         | Not ready        |

| LSR1 overrun error (OE)                        | Error         | No error         |

| LSR2 parity error (PE)                         | Error         | No error         |

| LSR3 framing error (FE)                        | Error         | No error         |

| LSR4 break interrupt (BI)                      | Break         | No break         |

| LSR5 transmitter holding register empty (THRE) | Empty         | Not empty        |

| LSR6 transmitter register empty (TEMT)         | Empty         | Not empty        |

| LSR7 receiver FIFO error                       | Error in FIFO | No error in FIFO |

#### PRINCIPLES OF OPERATION

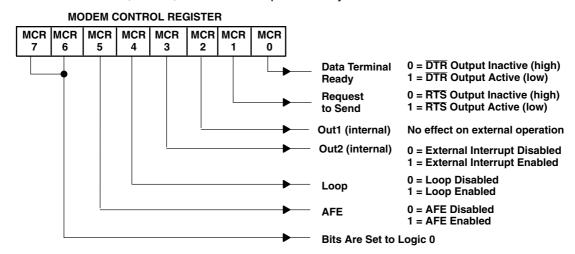

## modem-control register (MCR)

The MCR controls the interface with the modem or data set as described in Figure 19. The MCR can be written and read. Outputs RTS and DTR are directly controlled by their control bits in this register. A high input asserts a low signal (active) at the output terminals. MCR bits 0, 1, 2, 3, and 4 are shown as follows:

- Bit 0: When MCR0 is set, the DTR output is forced low. When MCR0 is cleared, the DTR output is forced high. The DTR output of the serial channel may be input into an inverting line driver in order to obtain the proper polarity input at the modem or data set.

- Bit1: When MCR1 is set, the RTS output is forced low. When MCR1 is cleared, the RTS output is forced high. The RTS output of the serial channel may be input into an inverting line driver to obtain the proper polarity input at the modem or data set.

- Bit 2: MCR2 has no effect on operation.

- Bit 3: When MCR3 is set, the external serial channel interrupt is enabled.