## TCAN1044-Q1, TCAN1044V-Q1

SLLSF17A -AUGUST 2019-REVISED DECEMBER 2019

# TCAN1044-Q1 Automotive Fault-Protected CAN FD Transceiver

#### 1 Features

- AEC-Q100: Qualified for automotive applications

- Temperature grade 1: –40°C to 125°C T<sub>A</sub>

- Meets the requirements of ISO 11898-2:2016 and ISO 11898-5:2007 physical layer standards

- Support of classical CAN and optimized CAN FD performance at 2, 5, and 8 Mbps

- Short and symmetrical propagation delays and fast loop times for enhanced timing margin

- Higher data rates in loaded CAN networks

- IO voltage range supports 1.7 V to 5.5 V

- Support for 1.8-V, 2.5-V, 3.3-V, and 5-V applications

- Receiver common mode input voltage: ±12 V

- Protection features:

- Bus fault protection: ±58 V

- Under-voltage protection

- TXD-dominant time-out (DTO)

- Data rates down to 9.2 kbps

- Thermal-shutdown protection (TSD)

- Operating modes:

- Normal mode

- Low power standby mode supporting remote wake-up request

- Optimized behavior when unpowered

- Bus and logic pins are high impedance (no load to operating bus or application)

- Hot-plug capable: power up/down glitch free operation on bus and RXD output

- Junction temperatures from: –40°C to 150°C

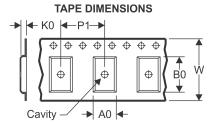

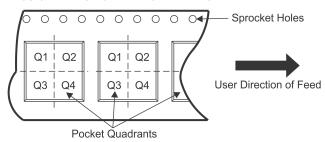

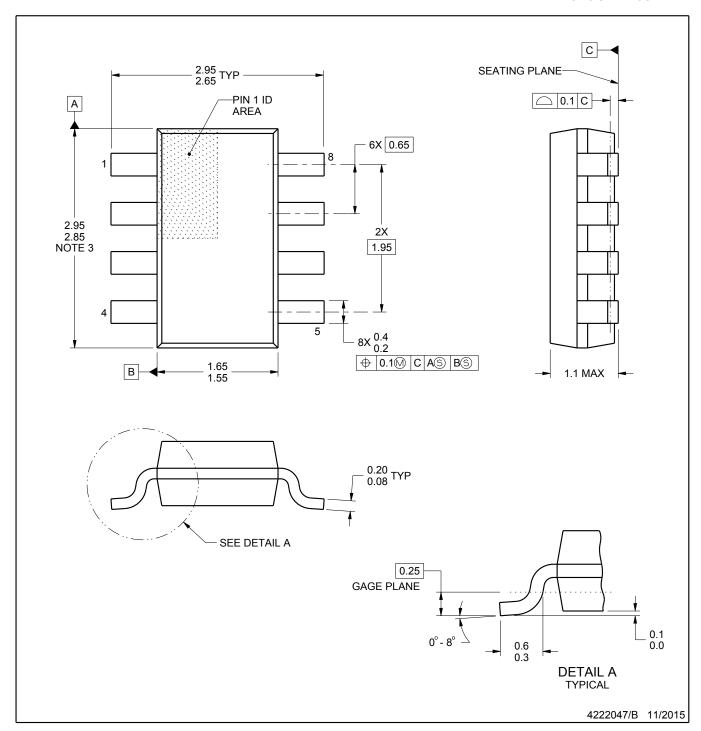

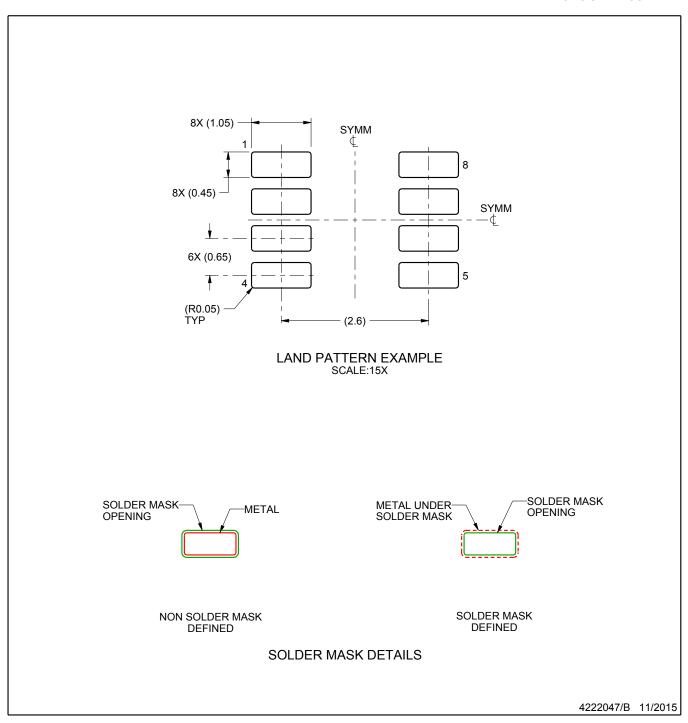

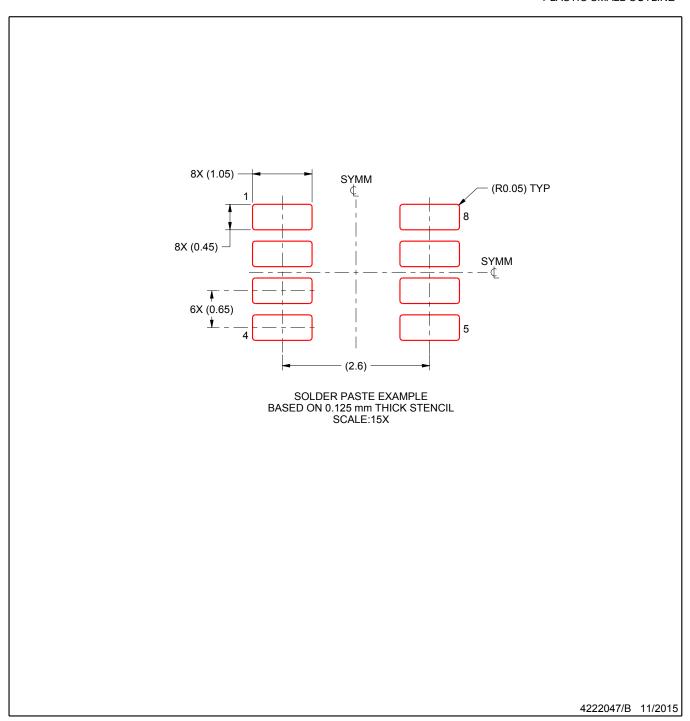

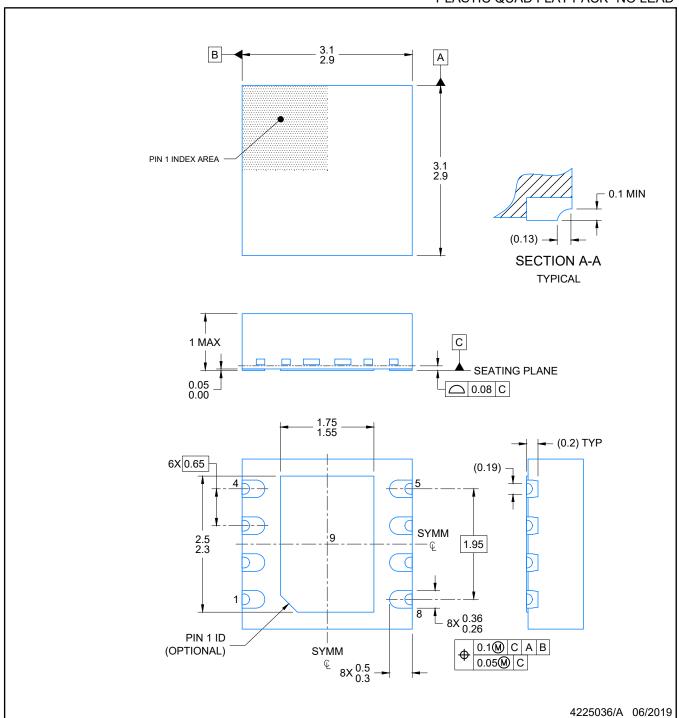

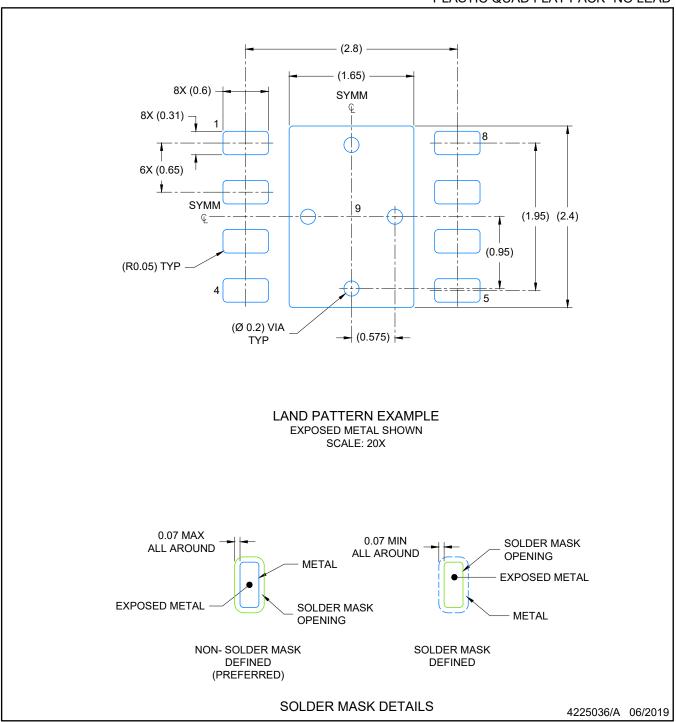

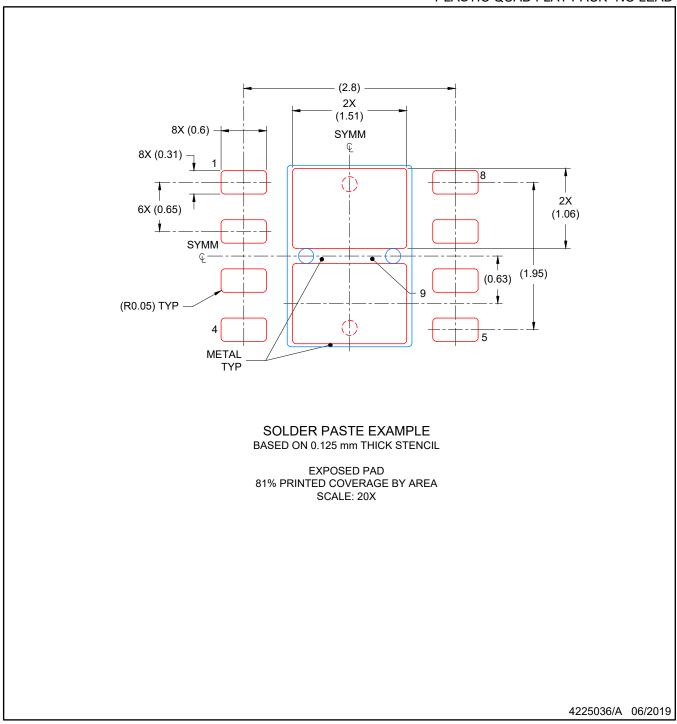

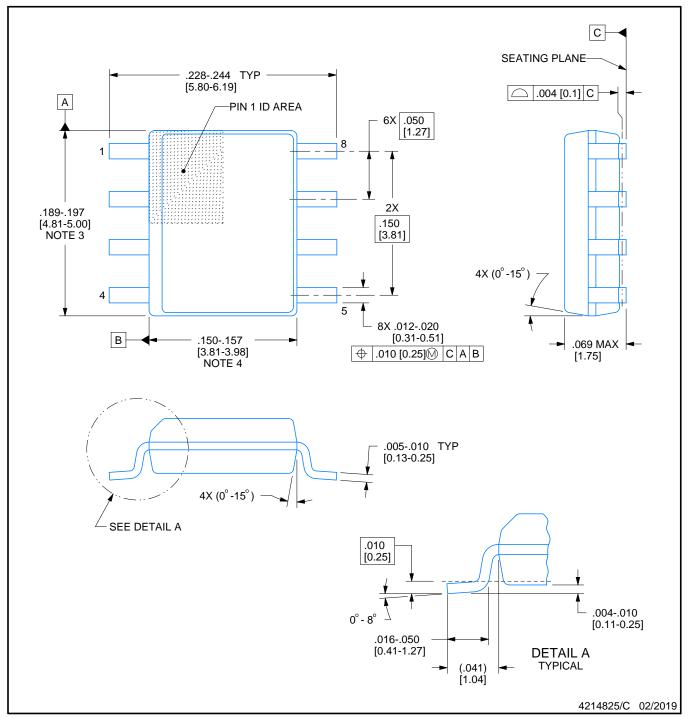

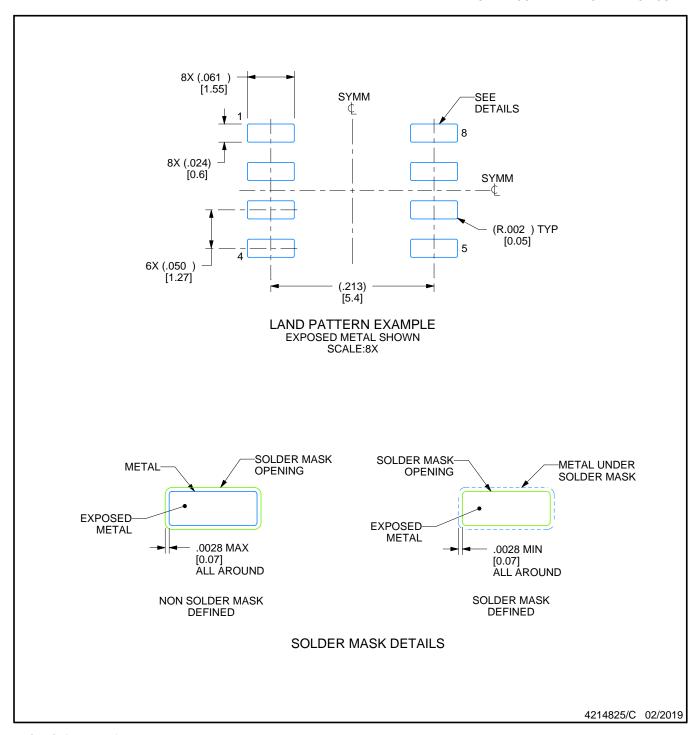

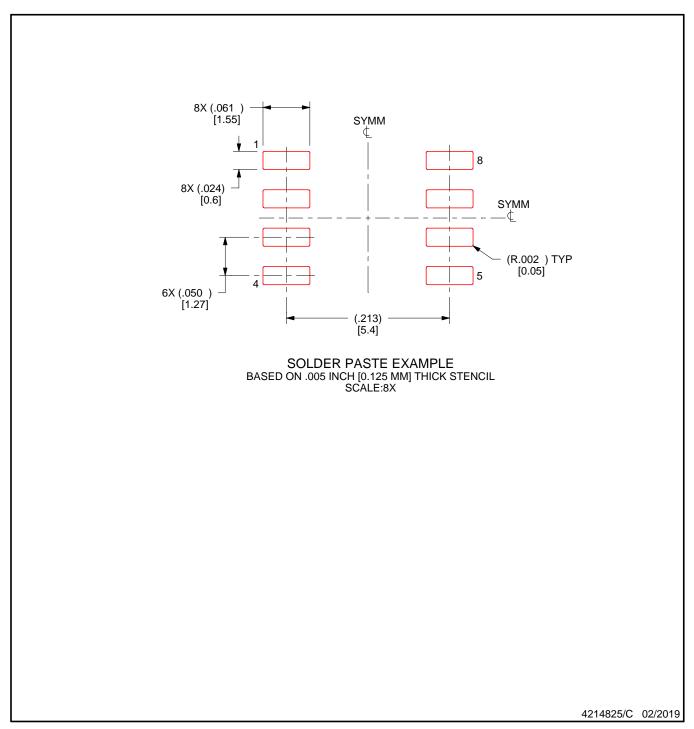

- Available in SOIC (8), SOT23 (8) packages (2.9 mm x 1.60 mm) and leadless VSON (8) packages (3.0 mm x 3.0 mm) with improved automated optical inspection (AOI) capability

# 2 Applications

- Automotive and Transportation

- Body control modules

- Automotive gateway

- Advanced driver assistance system (ADAS)

- Infotainment

# 3 Description

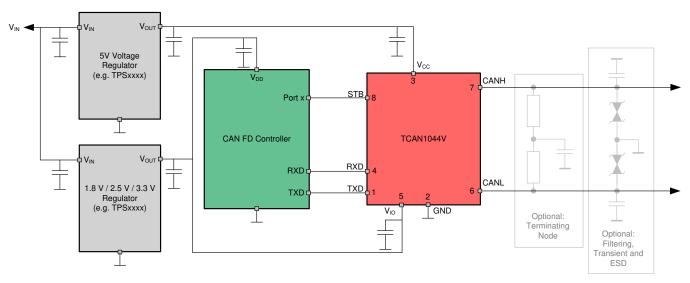

The TCAN1044-Q1 is a high speed controller area network (CAN) transceiver that meets the physical layer requirements of the ISO 11898-2:2016 high-speed CAN specification.

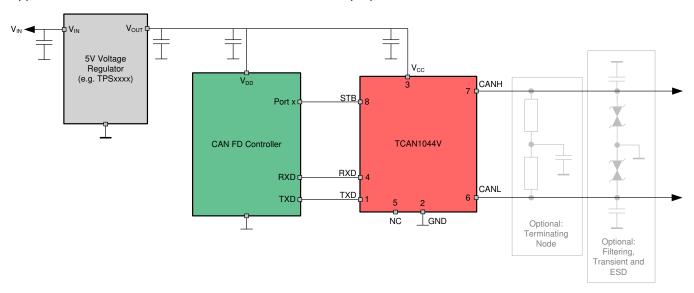

TCAN1044-Q1 transceiver supports classical CAN and CAN FD networks up to 8 megabits per second (Mbps). The TCAN1044-Q1 includes internal logic level translation via the V<sub>IO</sub> terminal to allow for interfacing the transceiver IOs directly to 1.8-V, 2.5-V, 3.3-V, or 5-V logic IOs. The transceiver has a low-power standby mode which supports remote wake-up via the ISO 11898-2:2016 defined wake-up pattern (WUP). The TCAN1044-Q1 transceiver also includes many protection and features including thermal-shutdown diagnostic (TSD), TXD-dominant time-out (DTO), supply undervoltage detection, and bus fault protection up to ±58 V.

#### Device Information<sup>(1)</sup>

| PART NUMBER  | PACKAGE  | BODY SIZE (NOM)   |

|--------------|----------|-------------------|

| TCAN1044x-Q1 | SOT (8)  | 2.90 mm x 1.60 mm |

|              | VSON (8) | 3.00 mm x 3.00 mm |

|              | SOIC (8) | 4.90 mm x 3.91 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

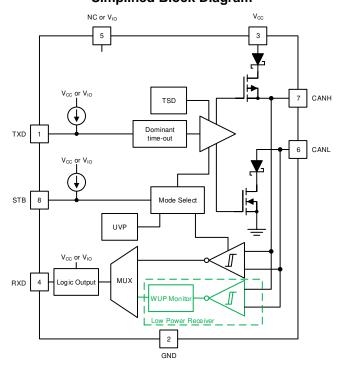

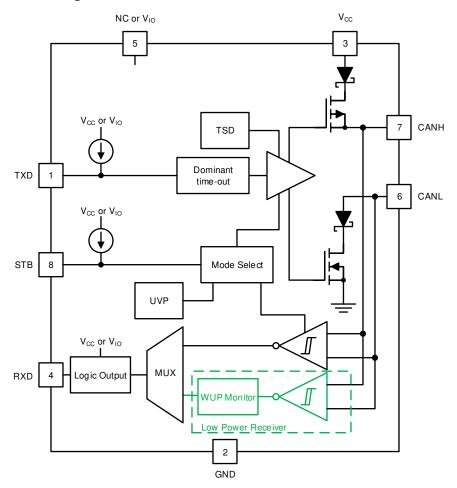

#### **Simplified Block Diagram**

# **Table of Contents**

| 1 | Features 1                           |    | 8.2 Functional Block Diagram                        | 15                |

|---|--------------------------------------|----|-----------------------------------------------------|-------------------|

| 2 |                                      |    | 8.3 Feature Description                             |                   |

|   | Applications                         |    | 8.4 Device Functional Modes                         |                   |

| 3 | Description 1                        | •  |                                                     |                   |

| 4 | Revision History2                    | 9  | Application and Implementation                      |                   |

| 5 | Pin Configuration and Functions 3    |    | 9.1 Application Information                         |                   |

| 6 | Specifications4                      |    | 9.2 Typical Application                             | 23                |

| • | 6.1 Absolute Maximum Ratings         |    | 9.3 System Examples                                 | 26                |

|   | 6.2 ESD Ratings                      | 10 | Power Supply Recommendations                        | 26                |

|   | 6.3 ESD Ratings                      | 11 | Layout                                              | . 27              |

|   | 6.4 Recommended Operating Conditions |    | 11.1 Layout Guidelines                              | 27                |

|   | 6.5 Thermal Characteristics          |    | 11.2 Layout Example                                 | 27                |

|   | 6.6 Supply Characteristics5          | 12 | Device and Documentation Support                    | . 28              |

|   | 6.7 Dissipation Ratings              |    | 12.1 Documentation Support                          | 28                |

|   | 6.8 Electrical Characteristics       |    | 12.2 Receiving Notification of Documentation Update | s <mark>28</mark> |

|   | 6.9 Switching Characteristics        |    | 12.3 Support Resources                              | 28                |

|   | 6.10 Typical Characteristics9        |    | 12.4 Trademarks                                     | 28                |

| 7 | Parameter Measurement Information 10 |    | 12.5 Electrostatic Discharge Caution                | 28                |

| 8 | Detailed Description                 |    | 12.6 Glossary                                       | 28                |

| U | 8.1 Overview                         | 13 | Mechanical, Packaging, and Orderable Information    | 28                |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | changes from Original (August 2019) to Revision A                                                                                                | Page |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | First public release of the data sheet                                                                                                           | 1    |

| • | Added SAE j2962-2 ESD                                                                                                                            | 4    |

| • | Changed foortnote to Tested according to IEC 62228-3:2019 CAN Transceivers, Section 6.3; standard pulses parameters defined in ISO 7637-2 (2011) | 4    |

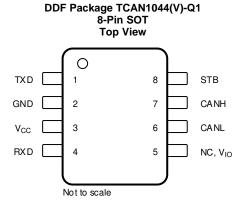

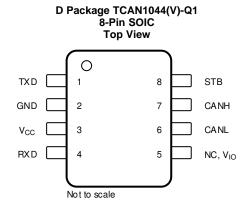

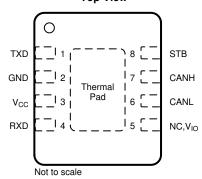

# 5 Pin Configuration and Functions

#### DRB Package TCAN1044(V)-Q1 8-Pin VSON Top View

#### **Pin Functions**

|                 | Pins        | Tyma           | Description                                                                                                               |

|-----------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------|

| Name            | No.         | Type           | Description                                                                                                               |

| TXD             | 1           | Digital Input  | CAN transmit data input                                                                                                   |

| GND             | 2           | GND            | Ground connection                                                                                                         |

| V <sub>CC</sub> | 3           | Supply         | 5-V supply voltage                                                                                                        |

| RXD             | 4           | Digital Output | CAN receive data output, tri-state when powered off                                                                       |

| NC              | - 5         | _              | No Connect (not internally connected); Devices without V <sub>IO</sub>                                                    |

| V <sub>IO</sub> | 5           | Supply         | IO supply voltage                                                                                                         |

| CANL            | 6           | Bus IO         | Low-level CAN bus input/output line                                                                                       |

| CANH            | 7           | Bus IO         | High-level CAN bus input/output line                                                                                      |

| STB             | 8           | Digital Input  | Standby input for mode control, integrated pull up                                                                        |

| Thermal Pad     | (VSON only) | _              | Electrically connected to GND, connect the thermal pad to the printed circuit board (PCB) ground plane for thermal relief |

Product Folder Links: TCAN1044-Q1 TCAN1044V-Q1

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)

|                          |                                                | MIN  | MAX | UNIT |

|--------------------------|------------------------------------------------|------|-----|------|

| V <sub>CC</sub>          | Supply voltage                                 | -0.3 | 6   | V    |

| V <sub>IO</sub>          | Supply voltage IO level shifter                | -0.3 | 6   | V    |

| V <sub>BUS</sub>         | CAN Bus IO voltage CANH and CANL               | -58  | 58  | V    |

| $V_{DIFF}$               | Max differential voltage between CANH and CANL | -45  | 45  | V    |

| V <sub>Logic_Input</sub> | Logic input terminal voltage                   | -0.3 | 6   | V    |

| V <sub>RXD</sub>         | RXD output terminal voltage range              | -0.3 | 6   | V    |

| I <sub>O(RXD)</sub>      | RXD output current                             | -8   | 8   | mA   |

| T <sub>J</sub>           | Operating virtual junction temperature range   | -40  | 150 | °C   |

| T <sub>STG</sub>         | Storage temperature                            | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

| V <sub>ESD</sub> |                            | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup>                                  | HBM classification level 3A for all pins                | ±3000  | V |

|------------------|----------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------|--------|---|

|                  | Electrostatic<br>discharge | , , , , , , , , , , , , , , , , , , , ,                                                  | HBM classififation level 3B for global pins CANH & CANL | ±10000 | ٧ |

|                  |                            | Charged-device model (CDM), per AEC Q100-011<br>CDM classification level C5 for all pins |                                                         | ±750   | V |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 ESD Ratings

|                  |                                               |                                        |                                                        | VALUE  | UNIT |

|------------------|-----------------------------------------------|----------------------------------------|--------------------------------------------------------|--------|------|

| V                | System Level Electro-Static Discharge         | CAN bus terminals (CANH, CANL) to GND  | SAE J2962-2 per ISO 10650<br>Powered Contact Discharge | ±8000  | V    |

| V <sub>ESD</sub> | (ESD) <sup>(1)</sup>                          | CAN bus terminals (CANTI, CANE) to GND | SAE J2962-2 per ISO 10650<br>Powered Air Discharge     | ±15000 | V    |

|                  | ISO 7637 ISO Pulse Transients (2)             | CANILLY ASSESSED (CANILL CANILL)       | Pulse 1                                                | -100   | V    |

|                  |                                               |                                        | Pulse 2a                                               | 75     | V    |

| $V_{Tran}$       | 150 7637 ISO Pulse Transients                 | CAN bus terminals (CANH, CANL)         | Pulse 3a                                               | -150   | V    |

|                  |                                               |                                        | Pulse 3b                                               | 100    | V    |

|                  | ISO 7637 Slow transients pulse <sup>(3)</sup> | CAN bus terminals (CANH, CANL) to GND  | DCC slow transient pulse                               | ±85    | V    |

Results given here are specific to the SAE J2962-2 Communication Transceivers Qualification Requirements - CAN. Testing performed by OEM approved independent 3<sup>rd</sup> party, EMC report available upon request.

# 6.4 Recommended Operating Conditions

|                      |                                        | MIN | NOM | MAX | UNIT |

|----------------------|----------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>      | Supply voltage                         | 4.5 | 5   | 5.5 | V    |

| $V_{IO}$             | Supply voltage for IO level shifter    | 1.7 |     | 5.5 | V    |

| I <sub>OH(RXD)</sub> | RXD terminal high level output current | -2  |     |     | mA   |

| I <sub>OL(RXD)</sub> | RXD terminal low level output current  |     |     | 2   | mA   |

| T <sub>A</sub>       | Operating ambient temperature          | -40 |     | 125 | °C   |

Product Folder Links: TCAN1044-Q1 TCAN1044V-Q1

<sup>(2)</sup> All voltage values, except differential IO bus voltages, are with respect to ground terminal.

<sup>(2)</sup> Tested according to IEC 62228-3:2019 CAN Transcievers, Section 6.3; standard pulses parameters defined in ISO 7637-2 (2011)

<sup>(3)</sup> Tested according to ISO 7637-3 (2017); Electrical transient transmission by capacitive and inductive coupling via lines other than supply lines

#### 6.5 Thermal Characteristics

|                       | THERMAL METRIC <sup>(1)</sup>                |          | UNIT      |            |      |

|-----------------------|----------------------------------------------|----------|-----------|------------|------|

| I DERMAL METRIC       |                                              | D (SOIC) | DDF (SOT) | DRB (VSON) | UNIT |

| $R_{\Theta JA}$       | Junction-to-ambient thermal resistance       | 128.1    | 119.9     | 49.9       | °C/W |

| $R_{\Theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 68.3     | 61.8      | 58.2       | °C/W |

| $R_{\Theta JB}$       | Junction-to-board thermal resistance         | 71.6     | 39.7      | 23.9       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 19.7     | 2.1       | 1.7        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 70.8     | 39.5      | 23.8       | °C/W |

| R <sub>OJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | -        | -         | 6.4        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

# 6.6 Supply Characteristics

Over recommended operating conditions with  $T_A$  = -40°C to 125°C (unless otherwise noted)

|                   | PARAMETER                                                                         |                                 | TEST CONDITIONS                                                                                             | MIN | TYP  | MAX  | UNIT |

|-------------------|-----------------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|-----|------|------|------|

|                   |                                                                                   | Dominant                        | See Figure 5,TXD = 0 V, STB = 0 V, $R_L = 60 \Omega$ , $C_L = open$                                         |     | 45   | 70   | mA   |

|                   | Supply current normal                                                             | Dominant                        | See Figure 5, TXD = 0 V, STB = 0 V, R <sub>L</sub> = 50 $\Omega$ , C <sub>L</sub> = open                    |     | 49   | 80   | mA   |

| I <sub>cc</sub>   | mode                                                                              | Recessive                       | See Figure 5, TXD = $V_{CC}$ , STB = 0 V, $R_L$<br>= 50 $\Omega$ , $C_L$ = open, RCM = open                 |     | 4.5  | 7.5  | mA   |

|                   |                                                                                   | Dominant with bus fault         | See Figure 5, TXD = 0 V, STB = 0 V, CANH = CANL = $\pm 25$ V, R <sub>L</sub> = open, C <sub>L</sub> = open  |     |      | 130  | mA   |

| I <sub>cc</sub>   | Supply current standby mode Devices with V <sub>IO</sub>                          |                                 | $\begin{aligned} TXD &= STB = V_{IO} \\ R_L &= 50 \ \Omega, \ C_L = open \\ See \ Figure \ 5 \end{aligned}$ |     | 0.2  | 1    | μΑ   |

| I <sub>cc</sub>   | Supply current standby mode Devices without V <sub>IO</sub>                       |                                 | $\begin{aligned} TXD &= STB = V_{CC} \\ R_L &= 50 \ \Omega, \ C_L = open \\ See \ Figure \ 5 \end{aligned}$ |     |      | 14.5 | μΑ   |

| I <sub>IO</sub>   | IO supply current normal mode                                                     | Dominant                        | TXD = 0 V, STB= 0 V<br>RXD floating                                                                         |     | 125  | 300  | μΑ   |

| I <sub>IO</sub>   | IO supply current normal mode                                                     | Recessive                       | TXD = 0 V, STB = 0 V<br>RXD floating                                                                        |     | 25   | 48   | μA   |

| I <sub>IO</sub>   | IO supply current standby r                                                       | node                            | TXD = 0 V, STB = V <sub>IO</sub><br>RXD floating                                                            |     | 8.5  | 13.5 | μA   |

| UV <sub>VCC</sub> | Rising under voltage detection on V <sub>CC</sub> for protected mode              |                                 |                                                                                                             | 4.2 | 4.4  | V    |      |

| UV <sub>VCC</sub> | Falling under voltage detection on V <sub>CC</sub> for protected mode             |                                 | tected mode                                                                                                 | 3.5 | 4    | 4.25 | V    |

| UV <sub>VIO</sub> | Rising under voltage detection on V <sub>IO</sub> (Devices with V <sub>IO</sub> ) |                                 |                                                                                                             |     | 1.56 | 1.65 | V    |

| $UV_{VIO}$        | Falling under voltage detec                                                       | tion on V <sub>IO</sub> (Device | s with V <sub>IO</sub> )                                                                                    | 1.4 | 1.51 | 1.59 | V    |

6.7 Dissipation Ratings

|                | PARAMETER                                | TEST CONDITIONS                                                                                                                                                                                                                                                                                | MIN | TYP | MAX | UNIT |

|----------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                |                                          | $\begin{array}{l} V_{CC} = 5 \text{ V, } V_{IO} = 1.8 \text{ V, } T_{J} = 27^{\circ}\text{C, } R_{L} = 60\Omega, \\ \text{TXD input} = 250 \text{ kHz } 50\% \text{ duty cycle} \\ \text{squarewave, } C_{L\_RXD} = 15 \text{ pF} \end{array}$                                                 |     | 110 |     | mW   |

|                |                                          | $\begin{aligned} & V_{CC} = 5 \; V, V_{IO} = 3.3 \; V, T_{I} = 27^{\circ} C, \; R_{L} = 60\Omega, \\ & TXD \; input = 250 \; kHz \; 50\% \; duty \; cycle \\ & squarewave, \; C_{L_{RXD}} = 15 \; pF \end{aligned}$                                                                            |     | 110 |     | mW   |

| P <sub>D</sub> | Average power dissipation<br>Normal mode | $ \begin{vmatrix} V_{\text{CC}} = 5 \text{ V, } V_{\text{IO}} = 5 \text{ V, } T_{\text{J}} = 27^{\circ}\text{C, } R_{\text{L}} = 60\Omega, \text{ TXD} \\ \text{input} = 250 \text{ kHz } 50\% \text{ duty cycle squarewave,} \\ C_{\text{L}_{-\text{RXD}}} = 15 \text{ pF} \\ \end{vmatrix} $ |     | 110 |     | mW   |

|                |                                          | $V_{CC}$ = 5.5 V, $V_{IO}$ = 1.8 V, $T_A$ = 125°C, $R_L$ = 60 $\Omega$ , TXD input = 2.5 MHz 50% duty cycle squarewave, $C_{L_RXD}$ = 15 pF                                                                                                                                                    |     | 120 |     | mW   |

|                |                                          | $\begin{array}{l} V_{CC} = 5.5 \text{ V}, V_{IO} = 3.3 \text{ V}, T_A = 125^{\circ}\text{C}, R_L = \\ 60\Omega, \text{TXD input} = 2.5 \text{ MHz} 50\% \text{ duty cycle} \\ \text{squarewave}, C_{L\_RXD} = 15 \text{ pF} \end{array}$                                                       |     | 120 |     | mW   |

| P <sub>D</sub> | Average power dissipation<br>Normal mode | $\begin{array}{l} V_{CC}=5.5~V,~V_{IO}=5~V,~T_{A}=125^{\circ}C,~R_{L}=60\Omega,\\ TXD~input=2.5~MHz~50\%~duty~cycle\\ squarewave,~C_{L\_RXD}=15~pF \end{array}$                                                                                                                                |     | 120 |     | mW   |

Copyright © 2019, Texas Instruments Incorporated Product Folder Links: TCAN1044-Q1 TCAN1044V-Q1

# **Dissipation Ratings (continued)**

|                      | PARAMETER                    | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------|-----------------|-----|-----|-----|------|

| T <sub>TSD</sub>     | Thermal shutdown temperature |                 |     | 192 |     | 5    |

| T <sub>TSD_HYS</sub> | Thermal shutdown hysteresis  |                 |     | 10  |     | C    |

# 6.8 Electrical Characteristics

|                                        |                                                                                     |                                                                                                     | -40°C to 125°C (unless otherwise note                                                                                                                                          |             | TVD                 | MAY  | LINUT |

|----------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|------|-------|

|                                        | PARAMETER                                                                           |                                                                                                     | TEST CONDITIONS                                                                                                                                                                | MIN         | TYP                 | MAX  | UNIT  |

| Driver Elect                           | rical Characteristics                                                               |                                                                                                     |                                                                                                                                                                                |             |                     |      |       |

| V <sub>O(DOM)</sub>                    | Dominant output voltage                                                             | CANH                                                                                                | See Figure 6 and Figure 14, TXD = 0 V,<br>STB = 0 V, 50 $\Omega \le R_L \le 65 \Omega$ , $C_L = open$ ,                                                                        | 2.75        |                     | 4.5  | V     |

| VO(DOM)                                | normal mode                                                                         | CANL                                                                                                | R <sub>CM</sub> = open                                                                                                                                                         | 0.5         |                     | 2.25 | V     |

| V <sub>O(REC)</sub>                    | Recessive output voltage normal mode                                                | CANH and CANL                                                                                       | See Figure 6 and Figure 14, TXD = $V_{IO}$ , STB = 0 V, $R_L$ = open (no load), $R_{CM}$ = open                                                                                | 2           | 0.5 V <sub>CC</sub> | 3    | V     |

| V <sub>SYM</sub>                       | Driver symmetry (V <sub>O(CANL)</sub> )/V <sub>CC</sub>                             |                                                                                                     | See Figure 6 and Figure 18, STB = 0 V, $R_L$ = 60 $\Omega$ , $C_{SPLIT}$ = 4.7 nF, $C_L$ = open, $R_{CM}$ = open, TXD = 250 kHz, 1 MHz, 2.5 MHz                                | 0.9         |                     | 1.1  | V/V   |

| V <sub>SYM_DC</sub>                    | DC output symmetry (V <sub>CC</sub> - V <sub>O(CANH)</sub> - V <sub>O(CANL)</sub> ) |                                                                                                     | See Figure 6 and Figure 14, STB = 0 V, $R_L$ = 60 $\Omega$ , $C_L$ = open                                                                                                      | -400        |                     | 400  | mV    |

|                                        | Differential output valtees                                                         |                                                                                                     | See Figure 6 and Figure 14, TXD = 0 V, STB = 0 V, 50 $\Omega$ ≤ R <sub>L</sub> ≤ 65 $\Omega$ , C <sub>L</sub> = open                                                           | 1.5         |                     | 3    | V     |

| $V_{OD(DOM)}$                          | Differential output voltage normal mode  Dominant                                   | CANH - CANL                                                                                         | See Figure 6 and Figure 14, TXD = 0 V, STB = 0 V, 45 $\Omega$ ≤ R <sub>L</sub> ≤ 70 $\Omega$ , C <sub>L</sub> = open                                                           | 1.4         |                     | 3.3  | ٧     |

|                                        |                                                                                     |                                                                                                     | See Figure 6 and Figure 14, TXD = 0 V,<br>STB = 0 V, $R_L$ = 2240 $\Omega$ , $C_L$ = open                                                                                      | 1.5         |                     | 5    | V     |

| V <sub>OD(REC)</sub>                   | Differential output voltage normal mode CANH - CAN                                  | CANH - CANL                                                                                         | See Figure 6 and Figure 14, TXD = $V_{IO}$ , STB = 0 V, $R_L$ = 60 $\Omega$ , $C_L$ = open                                                                                     | -120        |                     | 12   | mV    |

| *OD(REC)                               | Recessive                                                                           | 0/4417 0/442                                                                                        | See Figure 6 and Figure 14, TXD = $V_{IO}$ , STB = 0 V, $R_L$ = open, $C_L$ = open                                                                                             | <b>–</b> 50 |                     | 50   | mV    |

| V <sub>O(STB)</sub> Bus output voltage | CANH                                                                                | 0 5 0 15 11 075 11 5                                                                                | -0.1                                                                                                                                                                           |             | 0.1                 | V    |       |

|                                        | standby mode                                                                        | CANL                                                                                                | See Figure 6 and Figure 14, STB = $V_{IO}$ , $R_L$ = open (no load), $R_{CM}$ = open                                                                                           | -0.1        |                     | 0.1  | V     |

|                                        | Starraby mode                                                                       | CANH - CANL                                                                                         | apan (na nada), nagar                                                                                                                                                          | -0.2        |                     | 0.2  | V     |

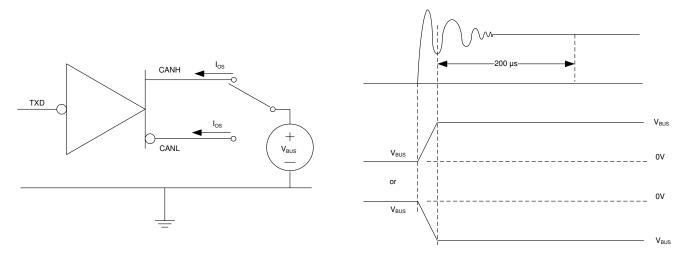

| , Short-circuit steady-state           | $V_{(C)}$ Short-circuit steady-state output current, $V_{(C)}$                      | See Figure 11 and Figure 14, STB = 0 V, V <sub>(CANH)</sub> = -15 V to 40 V, CANL = open, TXD = 0 V | -115                                                                                                                                                                           |             |                     | mA   |       |

| los(ss_DOM) dominant, normal mode      |                                                                                     |                                                                                                     | See Figure 11 and Figure 14, STB = 0 V, $V_{(CAN\_L)}$ = -15 V to 40 V, CANH = open, TXD = 0 V                                                                                 |             |                     | 115  | mA    |

| I <sub>OS(SS_REC)</sub>                | Short-circuit steady-state output current, recessive, normal mode                   |                                                                                                     | See Figure 11 and Figure 14, STB = 0 V,<br>$-27 \text{ V} \le \text{V}_{BUS} \le 32 \text{ V}$ ,<br>Where $\text{V}_{BUS} = \text{CANH} = \text{CANL}$ , TXD = $\text{V}_{IO}$ | <b>-</b> 5  |                     | 5    | mA    |

| Receiver Ele                           | ectrical Characteristics                                                            |                                                                                                     | 12                                                                                                                                                                             |             |                     |      |       |

| V <sub>IT</sub>                        | Input threshold voltage norr                                                        | mal mode                                                                                            | See Figure 7, Table 1, and Table 7<br>STB = 0 V, -12 V ≤ V <sub>CM</sub> ≤ 12 V                                                                                                | 500         |                     | 900  | mV    |

| V <sub>IT(STB)</sub>                   | Input threshold standby mo                                                          | de                                                                                                  | See Figure 7, Table 1, and Table 7<br>STB = $V_{IO}$ , -12 V $\leq V_{CM} \leq$ 12 V                                                                                           | 400         |                     | 1150 | mV    |

| $V_{DOM}$                              | Normal mode dominant stat voltage range                                             | te differential input                                                                               | See Figure 7, Table 1, and Table 7<br>STB = 0 V, -12 V ≤ V <sub>CM</sub> ≤ 12 V                                                                                                | 0.9         |                     | 9    | V     |

| $V_{REC}$                              | Normal mode recessive sta voltage range                                             | te differential input                                                                               | See Figure 7, Table 1, and Table 7<br>STB = 0 V, -12 V ≤ V <sub>CM</sub> ≤ 12 V                                                                                                | -4          |                     | 0.5  | ٧     |

| V <sub>DOM(STB)</sub>                  | Standby mode dominant state differential input voltage range                        |                                                                                                     | See Figure 7, Table 1, and Table 7<br>STB = $V_{IO}$ , -12 V $\leq V_{CM} \leq$ 12 V                                                                                           | 1.15        |                     | 9    | ٧     |

| V <sub>REC(STB)</sub>                  | Standby mode recessive stavoltage range                                             | ate differential input                                                                              | See Figure 7, Table 1, and Table 7<br>STB = $V_{IO}$ , -12 V $\leq V_{CM} \leq$ 12 V                                                                                           | -4          |                     | 0.4  | ٧     |

| V <sub>HYS</sub>                       | Hysteresis voltage for input mode                                                   | threshold normal                                                                                    | See Figure 7, Table 1, and Table 7<br>STB = 0 V, -12 V ≤ V <sub>CM</sub> ≤ 12 V                                                                                                |             | 100                 |      | mV    |

| V <sub>CM</sub>                        | Common mode range norm modes                                                        | al and standby                                                                                      | See Figure 7 and Table 7                                                                                                                                                       | -12         |                     | 12   | V     |

| I <sub>LKG(IOFF)</sub>                 | Unpowered bus input leaka                                                           | ge current                                                                                          | CANH = CANL = 5 V, V <sub>CC</sub> = V <sub>IO</sub> = GND                                                                                                                     |             |                     | 5    | μΑ    |

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

Over recomended operating conditions with  $T_A = -40$ °C to 125°C (unless otherwise noted)

| PARAMETER                                                 |                                                                                          | TEST CONDITIONS                                                                                                                                                 | MIN                 | TYP  | MAX                 | UNIT |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|---------------------|------|

| C <sub>I</sub> Input capacitance to ground (CANH or CANL) |                                                                                          | TVD (1)                                                                                                                                                         |                     |      | 20                  | pF   |

| C <sub>ID</sub>                                           | Differential input capacitance                                                           | $-TXD = V_{IO}^{(1)}$                                                                                                                                           |                     |      | 10                  | pF   |

| R <sub>ID</sub>                                           | Differential input resistance                                                            | TVP (1)                                                                                                                                                         | 40                  |      | 90                  | kΩ   |

| R <sub>IN</sub>                                           | Single ended input resistance (CANH or CANL)                                             | $\begin{array}{l} - \text{TXD} = \text{V}_{\text{IO}}^{(1)} \\ \text{STB} = 0 \text{ V}, -12 \text{ V} \leq \text{V}_{\text{CM}} \leq 12 \text{ V} \end{array}$ | 20                  |      | 45                  | kΩ   |

| R <sub>IN(M)</sub>                                        | Input resistance matching [1 – (R <sub>IN(CANH)</sub> / R <sub>IN(CANL)</sub> )] × 100 % | $V_{(CAN\_H)} = V_{(CAN\_L)} = 5 \text{ V}$                                                                                                                     | -1                  |      | 1                   | %    |

| TXD Termi                                                 | inal (CAN Transmit Data Input)                                                           |                                                                                                                                                                 | •                   |      |                     |      |

| V <sub>IH</sub>                                           | High-level input voltage                                                                 | Devices without V <sub>IO</sub>                                                                                                                                 | 0.7 V <sub>CC</sub> |      |                     | V    |

| $V_{IH}$                                                  | High-level input voltage                                                                 | Devices with V <sub>IO</sub>                                                                                                                                    | 0.7 V <sub>IO</sub> |      |                     | V    |

| V <sub>IL</sub>                                           | Low-level input voltage                                                                  | Devices without V <sub>IO</sub>                                                                                                                                 |                     |      | 0.3 V <sub>CC</sub> | V    |

| V <sub>IL</sub>                                           | Low-level input voltage                                                                  | Devices with V <sub>IO</sub>                                                                                                                                    |                     |      | 0.3 V <sub>IO</sub> | V    |

| I <sub>IH</sub>                                           | High-level input leakage current                                                         | $TXD = V_{CC} = V_{IO} = 5.5 \text{ V}$                                                                                                                         | -2.5                | 0    | 1                   | μA   |

| I <sub>IL</sub>                                           | Low-level input leakage current                                                          | TXD = 0 V, V <sub>CC</sub> = V <sub>IO</sub> = 5.5 V                                                                                                            | -200                | -100 | -20                 | μA   |

| I <sub>LKG(OFF)</sub>                                     | Unpowered leakage current                                                                | $TXD = 5.5 \text{ V}, V_{CC} = V_{IO} = 0 \text{ V}$                                                                                                            | -1                  | 0    | 1                   | μA   |

| Cı                                                        | Input Capacitance                                                                        | $V_{IN} = 0.4 \times \sin(2 \times \pi \times 2 \times 10^6 \times t) + 2.5 \text{ V}$                                                                          |                     | 5    |                     | pF   |

| RXD Term                                                  | inal (CAN Receive Data Output)                                                           |                                                                                                                                                                 |                     |      |                     | I    |

| V <sub>OH</sub>                                           | High-level input voltage                                                                 | Devices without V <sub>IO</sub><br>See Figure 7, I <sub>O</sub> = -2 mA                                                                                         | 0.8 V <sub>CC</sub> |      |                     | V    |

| V <sub>OH</sub>                                           | High-level input voltage                                                                 | Devices with $V_{IO}$<br>See Figure 7, $I_{O} = -2$ mA                                                                                                          | 0.8 V <sub>IO</sub> |      |                     | V    |

| V <sub>OL</sub>                                           | Low-level input voltage                                                                  | Devices without V <sub>IO</sub><br>See Figure 7, I <sub>O</sub> = 2 mA                                                                                          |                     |      | 0.2 V <sub>CC</sub> | V    |

| V <sub>OL</sub>                                           | Low-level input voltage                                                                  | Devices with V <sub>IO</sub><br>See Figure 7, I <sub>O</sub> = 2 mA                                                                                             |                     |      | 0.2 V <sub>IO</sub> | V    |

| I <sub>LKG(OFF)</sub>                                     | Unpowered leakage current                                                                | RXD = 5.5 V, V <sub>CC</sub> = V <sub>IO</sub> = 0 V                                                                                                            | -1                  | 0    | 1                   | μΑ   |

| STB Termi                                                 | inal (Standby Mode Input)                                                                |                                                                                                                                                                 |                     |      |                     |      |

| V <sub>IH</sub>                                           | High-level input voltage                                                                 | Devices without V <sub>IO</sub>                                                                                                                                 | 0.7 V <sub>CC</sub> |      |                     | V    |

| $V_{IH}$                                                  | High-level input voltage                                                                 | Devices with V <sub>IO</sub>                                                                                                                                    | 0.7 V <sub>IO</sub> |      |                     | V    |

| V <sub>IL</sub>                                           | Low-level input voltage                                                                  | Devices without V <sub>IO</sub>                                                                                                                                 |                     |      | 0.3 V <sub>CC</sub> | V    |

| V <sub>IL</sub>                                           | Low-level input voltage                                                                  | Devices with V <sub>IO</sub>                                                                                                                                    |                     |      | 0.3 V <sub>IO</sub> | V    |

| I <sub>IH</sub>                                           | High-level input leakage current STB                                                     | $V_{CC} = V_{IO} = STB = 5.5 \text{ V}$                                                                                                                         | -2                  |      | 2                   | μA   |

| I <sub>IL</sub>                                           | Low-level input leakage current STB                                                      | V <sub>CC</sub> = V <sub>IO</sub> = 5.5 V, STB = 0 V                                                                                                            | -20                 |      | -2                  | μA   |

| I <sub>LKG(OFF)</sub>                                     | Unpowered leakage current                                                                | STB = 5.5V, V <sub>CC</sub> = V <sub>IO</sub> = 0 V                                                                                                             | -1                  | 0    | 1                   | μΑ   |

<sup>(1)</sup>  $V_{IO} = V_{CC}$  in non-V variants of device

# 6.9 Switching Characteristics

Over recomended operating conditions with  $T_A = -40$ °C to 125°C (unless otherwise noted)

|                                  | PARAMETER                                                                            | TEST CONDITIONS                                                                                                  | MIN | TYP | MAX | UNIT |  |

|----------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| Device Switching Characteristics |                                                                                      |                                                                                                                  |     |     |     |      |  |

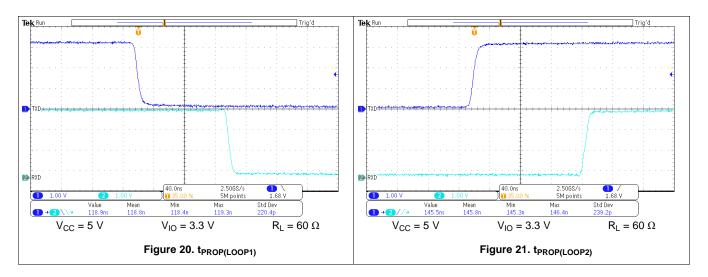

| t <sub>PROP(LOOP1)</sub>         | Total loop delay, driver input (TXD) to receiver                                     | See Figure 8, normal mode, $V_{IO}$ = 2.8 V to 5.5 V, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF |     | 125 | 210 | ns   |  |

|                                  | output (RXD), recessive to dominant                                                  | See Figure 8, normal mode, $V_{IO}$ = 1.7 V, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF          |     | 165 | 255 | ns   |  |

| t <sub>PROP(LOOP2)</sub>         | Total loop delay, driver input (TXD) to receiver output (RXD), dominant to recessive | See Figure 8, normal mode, $V_{IO}$ = 2.8 V to 5.5 V, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF |     | 150 | 210 | ns   |  |

|                                  |                                                                                      | See Figure 8, normal mode, $V_{IO}$ = 1.7 V, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF          |     | 180 | 255 | ns   |  |

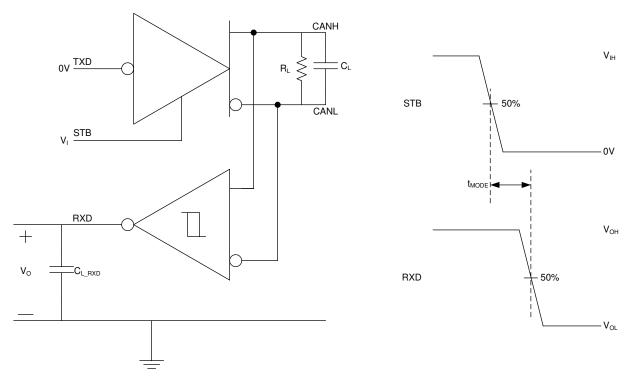

| t <sub>MODE</sub>                | Mode change time, from normal to standby or from standby to normal                   | See Figure 9                                                                                                     |     |     | 20  | μs   |  |

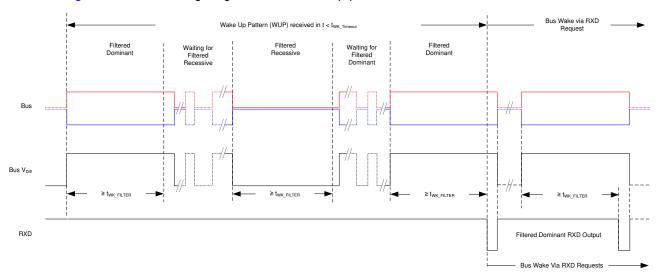

| t <sub>WK_FILTER</sub>           | Filter time for a valid wake-up pattern                                              | See Figure 16                                                                                                    | 0.5 |     | 1.8 | μs   |  |

Product Folder Links: TCAN1044-Q1 TCAN1044V-Q1

# **Switching Characteristics (continued)**

Over recomended operating conditions with  $T_A$  = -40°C to 125°C (unless otherwise noted)

| PARAMETER               |                                                                                    | TEST CONDITIONS                                                                     | MIN | TYP | MAX | UNIT |

|-------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>WK_TIMEOUT</sub> | Bus wake-up timeout value                                                          | See Figure 16                                                                       | 0.8 |     | 6   | ms   |

| Driver Switchin         | ng Characteristics                                                                 |                                                                                     |     |     |     |      |

| t <sub>pHR</sub>        | Propagation delay time, high TXD to driver recessive (dominant to recessive)       |                                                                                     |     | 80  |     | ns   |

| t <sub>pLD</sub>        | Propagation delay time, low TXD to driver dominant (recessive to dominant)         | See Figure 6, STB = 0 V, $R_L$ = 60 $\Omega$ , $C_L$                                |     | 70  |     | ns   |

| t <sub>sk(p)</sub>      | Pulse skew ( tpHR - tpLD )                                                         | = 100 pF, R <sub>CM</sub> = open                                                    |     | 20  |     | ns   |

| t <sub>R</sub>          | Differential output signal rise time                                               |                                                                                     |     | 30  |     | ns   |

| t <sub>F</sub>          | Differential output signal fall time                                               |                                                                                     |     | 50  |     | ns   |

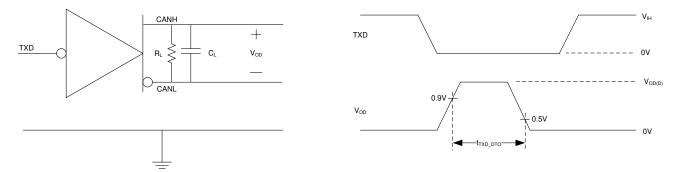

| t <sub>TXD_DTO</sub>    | Dominant timeout                                                                   | See Figure 10, $R_L = 60 \Omega$ , $C_L = 100 pF$ , $STB = 0 V$                     | 1.2 |     | 4.0 | ms   |

| Receiver Switch         | hing Characteristics                                                               |                                                                                     |     |     |     |      |

| t <sub>pRH</sub>        | Propagation delay time, bus recessive input to high output (dominant to recessive) |                                                                                     |     | 90  |     | ns   |

| t <sub>pDL</sub>        | Propagation delay time, bus dominant input to low output (recessive to dominant)   | See Figure 7<br>STB = 0 V,                                                          |     | 65  |     | ns   |

| t <sub>R</sub>          | RXD output signal rise time                                                        | $C_{L(RXD)} = 15 \text{ pF}$                                                        |     | 10  |     | ns   |

| t <sub>F</sub>          | RXD output signal fall time                                                        |                                                                                     |     | 10  |     | ns   |

| FD Timing Cha           | racteristics                                                                       |                                                                                     |     |     |     |      |

| t <sub>BIT(BUS)</sub>   | Bit time on CAN bus output pins with $t_{BIT(TXD)}$ = 500 ns                       |                                                                                     | 450 |     | 530 | ns   |

| t <sub>BIT(BUS)</sub>   | Bit time on CAN bus output pins with $t_{BIT(TXD)}$ = 200 ns                       | See Figure 8, STB = 0 V, $R_L$ = 60 $\Omega$ , $C_L$ = 100 pF, $C_{L(RXD)}$ = 15 pF | 155 |     | 210 | ns   |

| t <sub>BIT(RXD)</sub>   | Bit time on RXD output pins with $t_{BIT(TXD)} = 500 \text{ ns}$                   | STB = 0 V                                                                           | 400 |     | 550 | ns   |

| t <sub>BIT(RXD)</sub>   | Bit time on RXD output pins with $t_{BIT(TXD)} = 200 \text{ ns}$                   |                                                                                     | 120 |     | 220 | ns   |

| t <sub>REC</sub>        | Receiver timing symmetry with t <sub>BIT(TXD)</sub> = 500 ns                       | $R_L = 60 \Omega$ , $C_L = 100 pF$ , $C_{L(RXD)} = 15 pF$ -50                       |     | 20  | ns  |      |

| t <sub>REC</sub>        | Receiver timing symmetry with t <sub>BIT(TXD)</sub> = 200 ns                       | $\Delta t_{REC} = t_{BIT(RXD)} - t_{BIT(BUS)}$                                      | -45 |     | 15  | ns   |

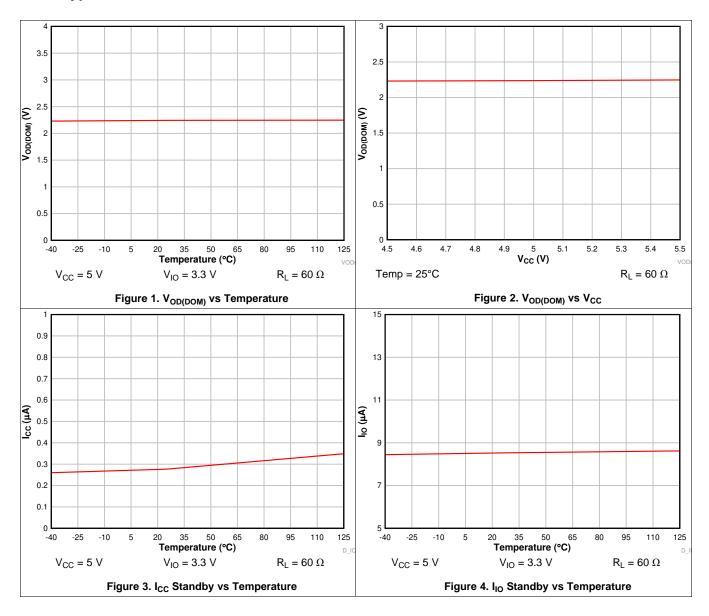

# 6.10 Typical Characteristics

# 7 Parameter Measurement Information

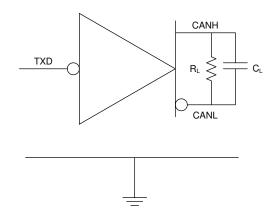

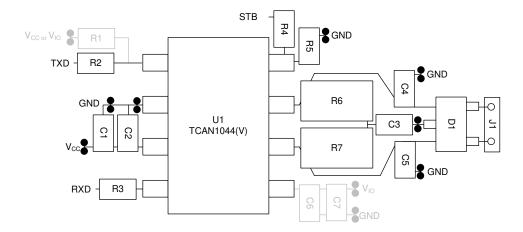

Figure 5. I<sub>CC</sub> Test Circuit

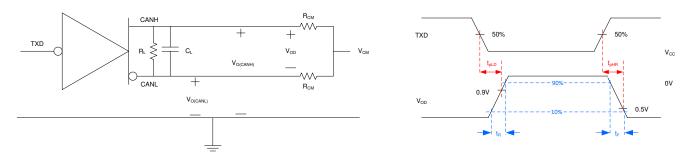

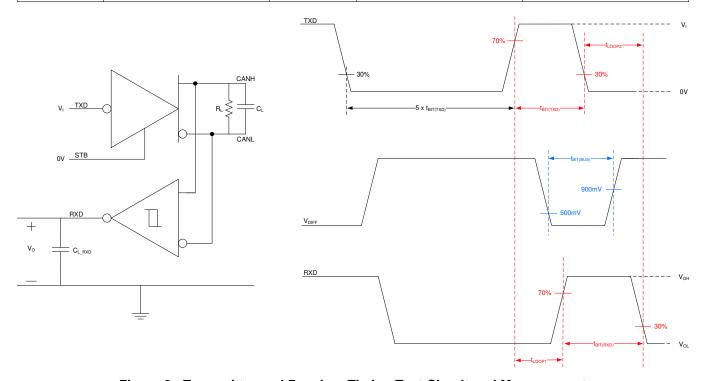

Figure 6. Driver Test Circuit and Measurement

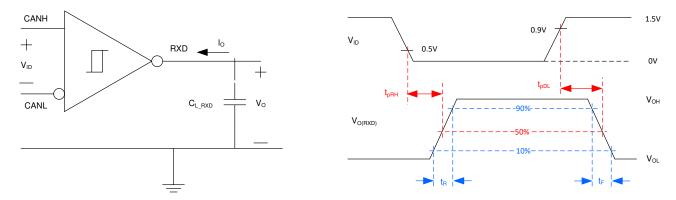

Figure 7. Receiver Test Circuit and Measurement

# Parameter Measurement Information (continued) Table 1. Receiver Differential Input Voltage Threshold Test (See Figure 7)

| Input      |                   |                 | Out | tput            |  |

|------------|-------------------|-----------------|-----|-----------------|--|

| $V_{CANH}$ | V <sub>CANL</sub> | V <sub>ID</sub> | RXD |                 |  |

| -11.5 V    | -12.5 V           | 1000 mV         | L   |                 |  |

| 12.5 V     | 11.5 V            | 1000 mV         |     | V               |  |

| -8.55 V    | -9.45 V           | 900 mV          |     | V <sub>OL</sub> |  |

| 9.45 V     | 8.55 V            | 900 mV          |     |                 |  |

| -8.25 V    | -9.25 V           | 500 mV          |     |                 |  |

| 9.25 V     | 8.25 V            | 500 mV          |     |                 |  |

| -11.8 V    | -12.2 V           | 400 mV          | н   | V <sub>OH</sub> |  |

| 12.2 V     | 11.8 V            | 400 mV          |     |                 |  |

| Open       | Open              | Х               |     |                 |  |

Figure 8. Transmitter and Receiver Timing Test Circuit and Measurement

Figure 9.  $t_{\text{MODE}}$  Test Circuit and Measurement

Figure 10. TXD Dominant Timeout Test Circuit and Measurement

Figure 11. Driver Short-Circuit Current Test and Measurement

# 8 Detailed Description

#### 8.1 Overview

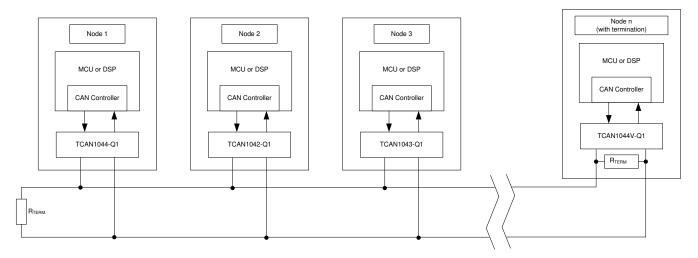

The TCAN1044-Q1 meets or exceeds the specifications of the ISO 11898-2:2016 high speed CAN (Controller Area Network) physical layer standard. The device has been certified to the requirements of ISO 11898-2:2016 and ISO 11898-5:2007 physical layer requirements according to the GIFT/ICT high speed CAN test specification. The transceiver provides a number of different protection features making it ideal for the stringent automotive system requirements while also supporting CAN FD data rates up to 8 Mbps.

The TCAN1044-Q1 conforms to the following CAN standards:

- CAN Transceiver Physical Layer Standards

- ISO 11898-2:2016 High speed medium access unit

- ISO 11898-5:2007 High speed medium access unit with low-power mode

- SAE J2284-1: High Speed CAN (HSC) for Vehicle Applications at 125 kbps

- SAE J2284-2: High Speed CAN (HSC) for Vehicle Applications at 250 kbps

- SAE J2284-3: High Speed CAN (HSC) for Vehicle Applications at 500 kbps

- SAE J2284-4: High-Speed CAN (HSC) for Vehicle Applications at 500 kbps with CAN FD Data at 2 Mbps

- SAE J2284-5: High-Speed CAN (HSC) for Vehicle Applications at 500 kbps with CAN FD Data at 5 Mbps

- ARINC 825-4 General Standardization of CAN (Controller Area Network) Bus Protocol For Airborne Use

- VeLIO (Vehicle LAN Interoperability and Optimization) CAN and CAN-FD Transceiver Requirements

- EMC requirements:

- SAE J2962-2 Communication Transceivers Qualification Requirements CAN

- Conformance Test requirements:

- ISO 16845-2 Road vehicles Controller area network (CAN) conformance test plan Part 2: High-speed medium access unit conformance test plan

# 8.2 Functional Block Diagram

Figure 12. Block Diagram

## 8.3 Feature Description

#### 8.3.1 Pin Description

#### 8.3.1.1 TXD

TXD is the logic-level signal, referenced to either  $V_{CC}$  or  $V_{IO}$  from a CAN controller to the device.

#### 8.3.1.2 GND

GND is the ground pin of the transceiver, it must be connected to the PCB ground.

#### 8.3.1.3 V<sub>CC</sub>

V<sub>CC</sub> provides the 5-V nominal power supply to the CAN transceiver.

#### 8.3.1.4 RXD

RXD is the logic-level signal, referenced to either  $V_{CC}$  or  $V_{IO}$ , from the TCAN1044-Q1 to a CAN controller. This pin is only driven once  $V_{IO}$  is present.

When a wake event takes place RXD is driven low.

#### 8.3.1.5 V<sub>10</sub>

The  $V_{IO}$  pin provides the digital IO voltage to match the CAN controller voltage thus avoiding the requirement for a level shifter. It supports voltages from 1.7 V to 5.5 V providing the widest range of controller support.

#### 8.3.1.6 CANH and CANL

These are the CAN high and CAN low differential bus pins. These pins are connected to the CAN transceiver and the low-voltage WUP CAN receiver.

#### 8.3.1.7 STB (Standby)

The STB pin is an input pin used for mode control of the transceiver. The STB pin can be supplied from either the system processor or from a static system voltage source. If normal mode is the only intended mode of operation than the STB pin can be tied directly to GND.

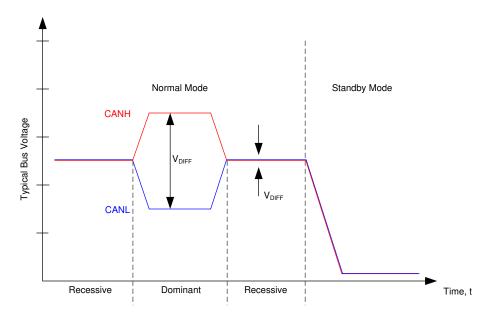

#### 8.3.2 CAN Bus States

The CAN bus has two logical states during operation: recessive and dominant. See Figure 13 and Figure 14.

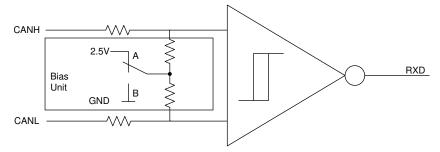

A dominant bus state occurs when the bus is driven differentially and corresponds to a logic low on the TXD and RXD pins. A recessive bus state occurs when the bus is biased to  $V_{CC}/2$  via the high-resistance internal input resistors ( $R_{IN}$ ) of the receiver and corresponds to a logic high on the TXD and RXD pins.

A dominant state overwrites the recessive state during arbitration. Multiple CAN nodes may be transmitting a dominant bit at the same time during arbitration, and in this case the differential voltage of the bus is greater than the differential voltage of a single driver.

The TCAN1044-Q1 transceiver implements a low-power standby (STB) mode which enables a third bus state where the bus pins are weakly biased to ground via the high resistance internal resistors of the receiver. See Figure 13 and Figure 14.

## **Feature Description (continued)**

Figure 13. Bus States

- A. Normal Mode

- B. Standby Mode

Figure 14. Simplified Recessive Common Mode Bias Unit and Receiver

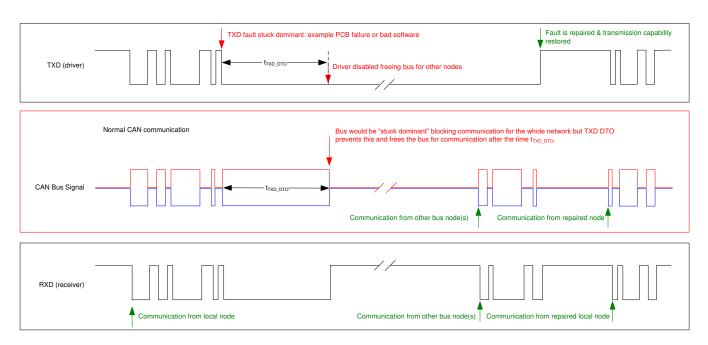

#### 8.3.3 TXD Dominant Timeout (DTO)

During normal mode, the only mode where the CAN driver is active, the TXD DTO circuit prevents the local node from blocking network communication in the event of a hardware or software failure where TXD is held dominant longer than the timeout period  $t_{TXD\_DTO}$ . The TXD DTO circuit is triggered by a falling edge on TXD. If no rising edge is seen before the timeout period of the circuit,  $t_{TXD\_DTO}$ , the CAN driver is disabled. This frees the bus for communication between other nodes on the network. The CAN driver is reactivated when a recessive signal is seen on the TXD pin, thus clearing the dominant time out. The receiver remains active and biased to  $V_{CC}/2$  and the RXD output reflects the activity on the CAN bus during the TXD DTO fault.

The minimum dominant TXD time allowed by the TXD DTO circuit limits the minimum possible transmitted data rate of the device. The CAN protocol allows a maximum of eleven successive dominant bits (on TXD) for the worst case, where five successive dominant bits are followed immediately by an error frame. The minimum transmitted data rate may be calculated using Equation 1.

Minimum Data Rate = 11 bits /

$$t_{TXD DTO}$$

= 11 bits / 1.2 ms = 9.2 kbps (1)

#### **Feature Description (continued)**

Figure 15. Example Timing Diagram for TXD Dominant Timeout

#### 8.3.4 CAN Bus Short Circuit Current Limiting

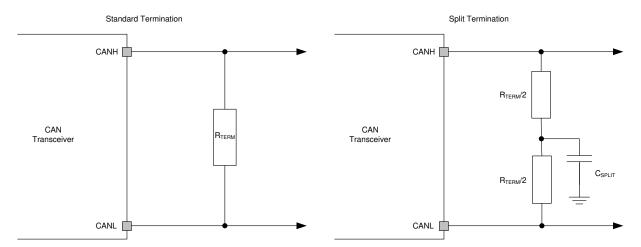

The TCAN1044-Q1 has several protection features that limit the short circuit current when a CAN bus line is shorted. These include CAN driver current limiting in the dominant and recessive states and TXD dominant state timeout which prevents permanently having the higher short circuit current of a dominant state in case of a system fault. During CAN communication the bus switches between the dominant and recessive states, thus the short circuit current may be viewed as either the current during each bus state or as a DC average current. When selecting termination resistors or a common mode choke for the CAN design the average power rating,  $I_{OS(AVG)}$ , should be used. The percentage dominant is limited by the TXD DTO and the CAN protocol which has forced state changes and recessive bits due to bit stuffing, control fields, and interframe space. These ensure there is a minimum amount of recessive time on the bus even if the data field contains a high percentage of dominant bits.

The average short circuit current of the bus depends on the ratio of recessive to dominant bits and their respective short circuit currents. The average short circuit current may be calculated using Equation 2.

$$I_{OS(AVG)} = \% \text{ Transmit x } [(\% \text{ REC\_Bits x } I_{OS(SS)\_REC}) + (\% \text{ DOM\_Bits x } I_{OS(SS)\_DOM})] + [\% \text{ Receive x } I_{OS(SS)\_REC}]$$

(2)

#### Where:

- I<sub>OS(AVG)</sub> is the average short circuit current

- % Transmit is the percentage the node is transmitting CAN messages

- % Receive is the percentage the node is receiving CAN messages

- % REC\_Bits is the percentage of recessive bits in the transmitted CAN messages

- % DOM Bits is the percentage of dominant bits in the transmitted CAN messages

- I<sub>OS(SS)\_REC</sub> is the recessive steady state short circuit current

- I<sub>OS(SS)</sub> DOM is the dominant steady state short circuit current

This short circuit current and the possible fault cases of the network should be taken into consideration when sizing the power supply used to generate the transceivers  $V_{CC}$  supply.

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

## Feature Description (continued)

#### 8.3.5 Thermal Shutdown (TSD)

If the junction temperature of the TCAN1044-Q1 exceeds the thermal shutdown threshold,  $T_{TSD}$ , the device turns off the CAN driver circuitry and blocks the TXD to bus transmission path. The shutdown condition is cleared when the junction temperature of the device drops below  $T_{TSD}$ . The CAN bus pins are biased to  $V_{CC}/2$  during a TSD fault and the receiver to RXD path remains operational. If the fault condition that caused the TSD fault is still present, the junction temperature may rise again and the device enters a TSD fault again. The TCAN1044-Q1 TSD circuit includes hysteresis which prevents the CAN driver output from oscillating during a TSD fault. If there is prolonged exposure to a TSD fault condition the device reliability could be affected.

#### 8.3.6 Undervoltage Lockout

The supply pins,  $V_{CC}$  and  $V_{IO}$ , have undervoltage detection that places the device into a protected state. This protects the bus during an undervoltage event on either supply pin.

Table 2. Undervoltage Lockout - TCAN1044-Q1

| V <sub>cc</sub>     | Device State | Bus            | RXD Pin        |

|---------------------|--------------|----------------|----------------|

| > UV <sub>VCC</sub> | Normal       | Per TXD        | Mirrors Bus    |

| < UV <sub>VCC</sub> | Protected    | High Impedance | High Impedance |

Table 3. Undervoltage Lockout - TCAN1044-Q1V

| V <sub>CC</sub>     | V <sub>IO</sub>     | Device State                         | Bus            | RXD Pin                                              |

|---------------------|---------------------|--------------------------------------|----------------|------------------------------------------------------|

| > UV <sub>VCC</sub> | > UV <sub>VIO</sub> | Normal                               | Per TXD        | Mirrors bus                                          |

| . 111/              | > UV <sub>VIO</sub> | STB = V <sub>IO</sub> : Standby mode | Biased to GND  | V <sub>IO</sub> : Remote wake request <sup>(1)</sup> |

| < UV <sub>VCC</sub> |                     | STB = GND: Protected mode            | High impedance | Recessive                                            |

| > UV <sub>VCC</sub> | < UV <sub>VIO</sub> | Protected                            | High impedance | High impedance                                       |

| < UV <sub>VCC</sub> | < UV <sub>VIO</sub> | Protected                            | High impedance | High impedance                                       |

<sup>(1)</sup> See Remote Wake Request via Wake-Up Pattern (WUP) in Standby Mode

Once an undervoltage condition is cleared and the supply has returned to a valid level the TCAN1044-Q1 transitions to normal mode after the  $t_{MODE}$  time has expired. The host controller should not attempt to send or receive messages until the  $t_{MODE}$  time has expired.

#### 8.3.7 Unpowered Device

The TCAN1044-Q1 is designed to be an ideal passive or no load to the CAN bus if the device is unpowered. The bus pins were designed to have low leakage currents when the device is unpowered, so they do not load the bus. This is critical if some nodes of the network are unpowered while the rest of the of network remains operational.

The logic pins also have low leakage currents when the device is unpowered, so they do not load other circuits which may remain powered.

Product Folder Links: TCAN1044-Q1 TCAN1044V-Q1

#### 8.3.8 Floating pins

The TCAN1044-Q1 has internal pull-ups on critical pins which place the device into known states if the pin floats. This internal bias should not be relied upon by design though, especially in noisy environments, but instead should be considered a failsafe protection feature.

When a CAN controller supporting open drain outputs are used an adequate external pull-up resistor must be used to ensure that the TXD output of the CAN controller maintains adequate bit timing to the input of the CAN transceiver. See Table 4 for details on pin bias conditions.

Table 4. Pin Bias

| Pin | Pull-up or Pull-down | Comment                                                                            |

|-----|----------------------|------------------------------------------------------------------------------------|

| TXD | Pull-up              | Weakly biases TXD towards recessive to prevent bus blockage or TXD DTO triggering  |

| STB | Pull-up              | Weakly biases STB towards low-power standby mode to prevent excessive system power |

#### 8.4 Device Functional Modes

#### 8.4.1 Operating Modes

The TCAN1044-Q1 has two main operating modes; normal mode and standby mode. Operating mode selection is made by applying a high or low level to the STB pin on the TCAN1044 device.

**Table 5. Operating Modes**

| STB  | Device Mode                               | Driver   | Receiver                                  | RXD Pin                                                          |

|------|-------------------------------------------|----------|-------------------------------------------|------------------------------------------------------------------|

| High | Low current standby mode with bus wake-up | Disabled | Low-power receiver and bus monitor enable | High (recessive) until valid WUP is received See section 8.3.3.1 |

| Low  | Normal Mode                               | Enabled  | Enabled                                   | Mirrors bus state                                                |

#### 8.4.2 Normal Mode

This is the normal operating mode of the TCAN1044-Q1. The CAN driver and receiver are fully operational and CAN communication is bi-directional. The driver is translating a digital input on the TXD input to a differential output on the CANH and CANL bus pins. The receiver is translating the differential signal from CANH and CANL to a digital output on the RXD output.

#### 8.4.3 Standby Mode

This is the low-power mode of the TCAN1044-Q1. The CAN driver and main receiver are switched off and bidirectional CAN communication is not possible. The low-power receiver and bus monitor circuits are enabled to allow for RXD wake-up requests via the CAN bus. A wake-up request is output to RXD as shown in Figure 16. The local CAN protocol controller should monitor RXD for transitions (high-to-low) and reactivate the device to normal mode by pulling the STB pin low. The CAN bus pins are weakly pulled to GND in this mode; see Figure 13 and Figure 14.

In standby mode, only the  $V_{IO}$  supply is required therefore the  $V_{CC}$  may be switched off for additional system level current savings.

#### 8.4.3.1 Remote Wake Request via Wake-Up Pattern (WUP) in Standby Mode

The TCAN1044-Q1 supports a remote wake-up request that is used to indicate to the host controller that the bus is active and the node should return to normal operation.

The device uses the multiple filtered dominant wake-up pattern (WUP) from the ISO 11898-2:2016 standard to qualify bus activity. Once a valid WUP has been received, the wake request is indicated to the controller by a falling edge and low period corresponding to a filtered dominant on the RXD output of the TCAN1044-Q1.

Product Folder Links: TCAN1044-Q1 TCAN1044V-Q1

The WUP consists of a filtered dominant pulse, followed by a filtered recessive pulse, and finally by a second filtered dominant pulse. The first filtered dominant initiates the WUP, and the bus monitor then waits on a filtered recessive; other bus traffic does not reset the bus monitor. Once a filtered recessive is received the bus monitor is waiting for a filtered dominant and again, other bus traffic does not reset the bus monitor. Immediately upon reception of the second filtered dominant the bus monitor recognizes the WUP and drives the RXD output low every time an additional filtered dominant signal is received from the bus.

For a dominant or recessive to be considered filtered, the bus must be in that state for more than the  $t_{WK\_FILTER}$  time. Due to variability in  $t_{WK\_FILTER}$  the following scenarios are applicable. Bus state times less than  $t_{WK\_FILTER(MIN)}$  are never detected as part of a WUP and thus no wake request is generated. Bus state times between  $t_{WK\_FILTER(MIN)}$  and  $t_{WK\_FILTER(MAX)}$  may be detected as part of a WUP and a wake-up request may be generated. Bus state times greater than  $t_{WK\_FILTER(MAX)}$  are always detected as part of a WUP, and thus a wake request is always generated. See Figure 16 for the timing diagram of the wake-up pattern.

The pattern and t<sub>WK\_FILTER</sub> time used for the WUP prevents noise and bus stuck dominant faults from causing false wake-up requests while allowing any valid message to initiate a wake-up request.

The ISO 11898-2:2016 standard has defined times for a short and long wake up filter time. The  $t_{WK\_FILTER}$  timing for the device has been picked to be within the minimum and maximum values of both filter ranges. This timing has been chosen such that a single bit time at 500 kbps, or two back to back bit times at 1 Mbps triggers the filter in either bus state. Any CAN frame at 500 kbps or less would contain a valid WUP.

For an additional layer of robustness and to prevent false wake-ups, the device implement a wake-up timeout feature. For a remote wake-up event to successfully occur, the entire WUP must be received within the timeout value  $t \le t_{WK\_TIMEOUT}$ . If not, the internal logic is reset and the transceiver remains in its current state without waking up. The full pattern must then be transmitted again, conforming to the constraints mentioned in this section. See Figure 16 for the timing diagram of the wake up pattern with wake timeout feature.

Figure 16. Wake-Up Pattern (WUP) with twk TIMEOUT

#### 8.4.4 Driver and Receiver Function

The digital logic input and output levels for the TCAN1044-Q1 are CMOS levels with respect to either  $V_{CC}$  for 5 V systems or  $V_{IO}$  for compatibility with MCUs having 1.8 V, 2.5 V, 3.3 V, or 5 V systems.

**Table 6. Driver Function Table**

| Davisa Mada | TXD Input <sup>(1)</sup> | Bus  | Driven Bus State <sup>(2)</sup> |                          |

|-------------|--------------------------|------|---------------------------------|--------------------------|

| Device Mode | TAD input\               | CANH | CANL                            | Driven bus State         |

| Normal      | Low                      | High | Low                             | Dominant                 |

| Normal      | High or open             | Hi-Z | Hi-Z                            | Biased recessive         |

| Standby     | X                        | Hi-Z | Hi-Z                            | Weak pull-down to ground |

<sup>(1)</sup> X = irrelevant

Table 7. Receiver Function Table Normal and Standby Mode

| Device Mode | CAN Differential Inputs V <sub>ID</sub> = V <sub>CANH</sub> - V <sub>CANL</sub> | Bus State | RXD Pin                             |

|-------------|---------------------------------------------------------------------------------|-----------|-------------------------------------|

|             | V <sub>ID</sub> ≥ 0.9 V                                                         | Dominant  | Low                                 |

| Normal      | $0.5 \text{ V} < \text{V}_{\text{ID}} < 0.9 \text{ V}$                          | Undefined | Undefined                           |

|             | V <sub>ID</sub> ≤ 0.5 V                                                         | Recessive | High                                |

|             | V <sub>ID</sub> ≥ 1.15 V                                                        | Dominant  | High                                |