Order

Now

## **TAS5760M**

SLOS772F - JULY 2013-REVISED FEBRUARY 2020

# **TAS5760M General-Purpose I2S Input Class-D Amplifier**

Technical

Documents

# Features

- Audio Performance (PVDD = 19 V,  $R_{SPK} = 8 \Omega$ ,  $SPK_GAIN[1:0] Pins = 01)$

- Idle Channel Noise = 100 µVrms (A-Wtd)

- THD+N = 0.03% (at 1 W, 1 kHz)

- SNR = 105 dB A-Wtd (Ref. to THD+N = 1%)

- Audio I/O Configuration:

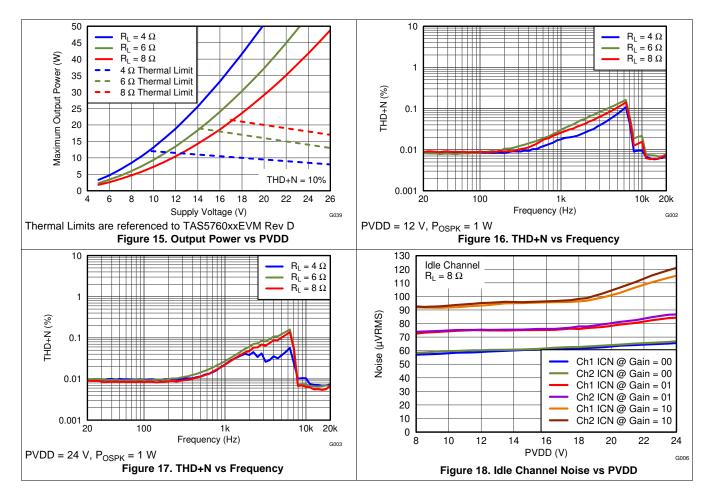

- Single Stereo I<sup>2</sup>S Input

- Stereo Bridge Tied Load (BTL) or Mono Parallel Bridge Tied Load (PBTL) Operation

- 32, 44.1, 48, 88.2, 96 kHz Sample Rates

- General Operational Features:

- Selectable Hardware or Software Control

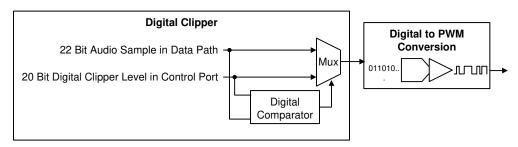

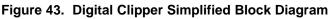

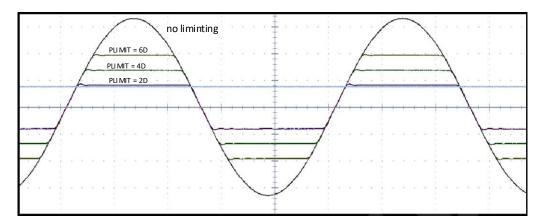

- Integrated Digital Output Clipper

- Programmable I<sup>2</sup>C Address (1101100<sup>[R/</sup><sub>W</sub>] or  $1101101[^{R/}w]$

- Closed-Loop Amplifier Architecture

- Adjustable Switching Frequency for Speaker Amplifier

- **Robustness Features:**

- Clock Error, DC, and Short-Circuit Protection

- Overtemperature and Programmable **Overcurrent Protection**

# 2 Applications

- LCD/LED TV and Multipurpose Monitors

- Sound Bars, Docking Stations, PC Audio

- General-Purpose Audio Equipment

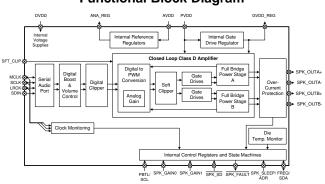

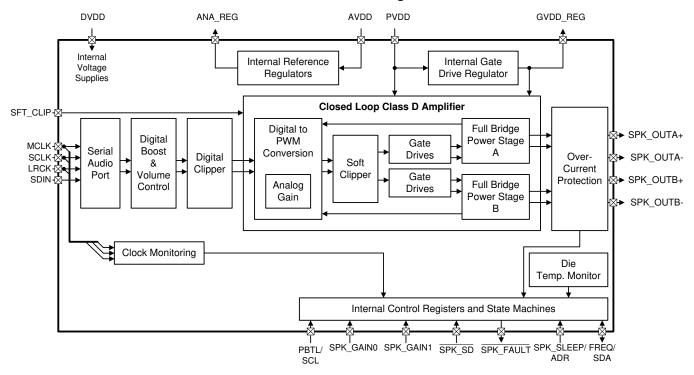

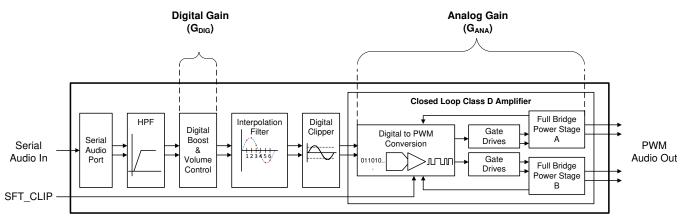

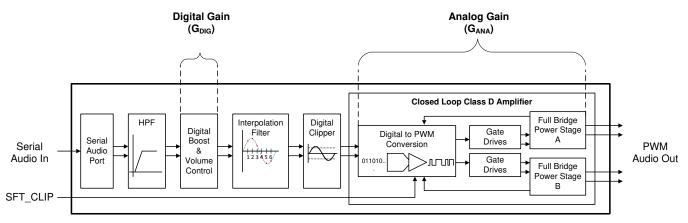

#### **Functional Block Diagram**

#### Description 3

Tools &

Software

The TAS5760M is a stereo I2S input device which includes hardware and software (I2C) control modes, integrated digital clipper, several gain options, and a wide power supply operating range to enable use in a multitude of applications. The TAS5760M operates with a nominal supply voltage from 4.5 to 24 VDC.

Support &

Community

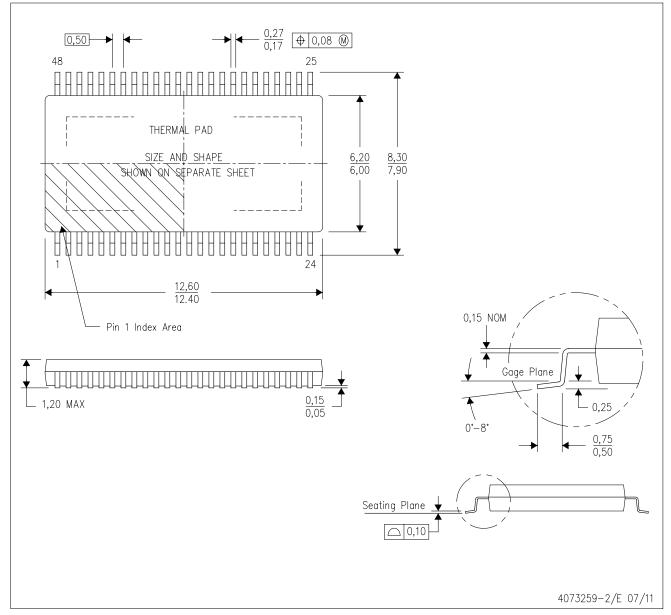

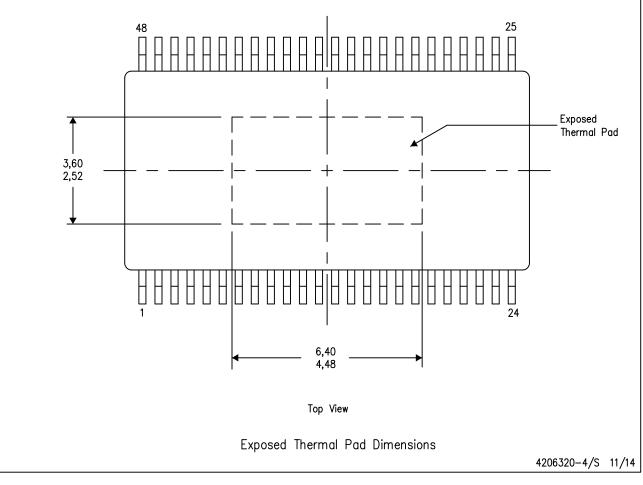

20

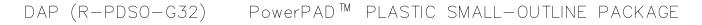

An optimal mix of thermal performance and device cost is provided in the 120-m $\Omega$  R<sub>DS(ON)</sub> of the output MOSFETs. Additionally, a thermally enhanced 48-Pin TSSOP provides excellent operation in the elevated ambient temperatures found in modern consumer electronic devices.

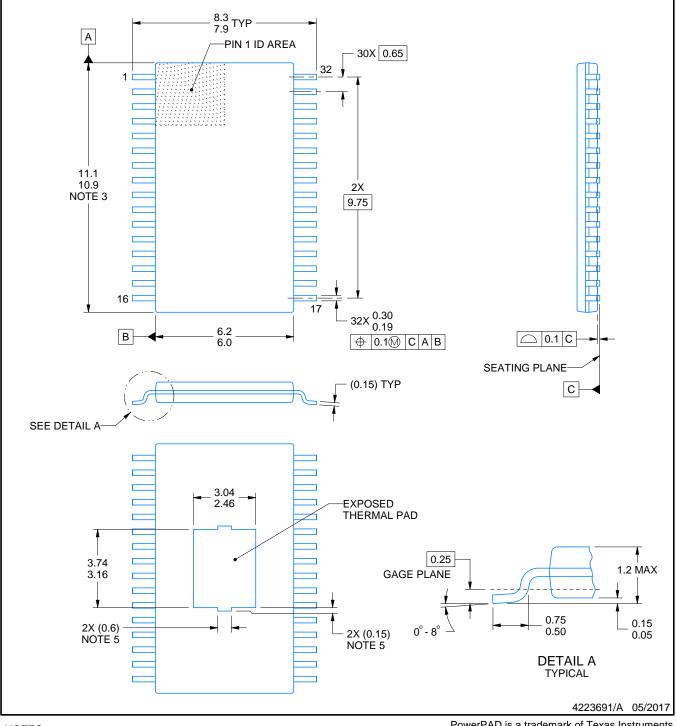

The entire TAS5760xx family is pin-to-pin compatible in the 48-Pin TSSOP package. Alternatively, to achieve the smallest possible solutions size for applications where pin-to-pin compatibility and a headphone or line driver are not required, a 32-Pin TSSOP package is offered for the TAS5760M and TAS5760L devices. The I<sup>2</sup>C register map in all of the TAS5760xx devices are identical, to ensure low development overhead when choosing between devices based upon system-level requirements.

Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)    |  |

|-------------|-------------|--------------------|--|

| TASEZCOM    | HTSSOP (48) | 12.50 mm × 6.10 mm |  |

| TAS5760M    | HTSSOP (32) | 11 mm × 6.2 mm     |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

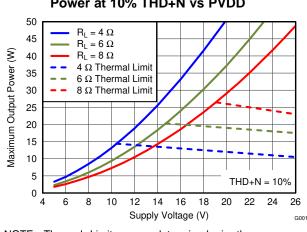

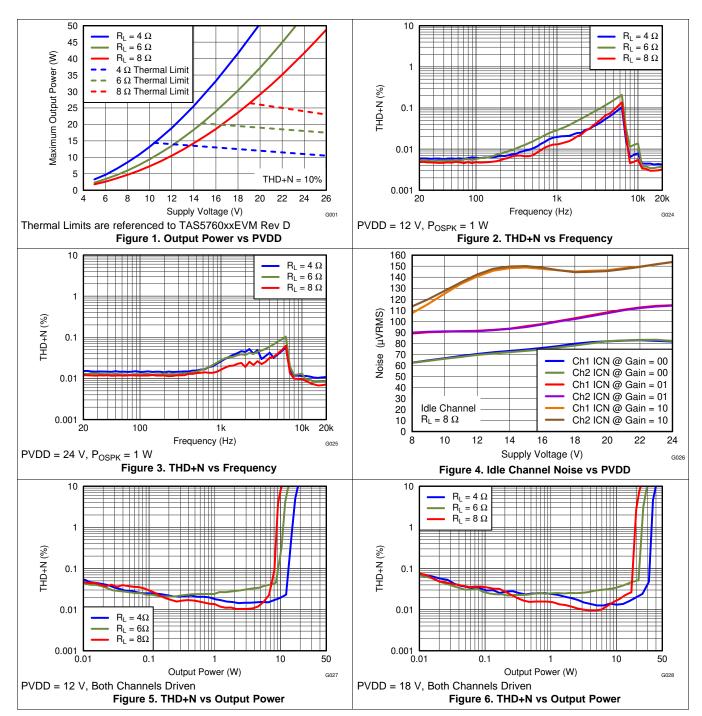

NOTE: Thermal Limits were determined via the TAS5760xxEVM

#### Power at 10% THD+N vs PVDD

Copyright © 2013–2020, Texas Instruments Incorporated

# Table of Contents

| 1 | Feat | tures 1                                                                                                |

|---|------|--------------------------------------------------------------------------------------------------------|

| 2 | Арр  | lications 1                                                                                            |

| 3 | Des  | cription1                                                                                              |

| 4 | Rev  | ision History2                                                                                         |

| 5 | Pin  | Configuration and Functions 4                                                                          |

| 6 |      | cifications7                                                                                           |

|   | 6.1  | Absolute Maximum Ratings7                                                                              |

|   | 6.2  | ESD Ratings7                                                                                           |

|   | 6.3  | Recommended Operating Conditions 8                                                                     |

|   | 6.4  | Digital I/O Pins 8                                                                                     |

|   | 6.5  | Master Clock 8                                                                                         |

|   | 6.6  | Serial Audio Port 9                                                                                    |

|   | 6.7  | Protection Circuitry                                                                                   |

|   | 6.8  | Speaker Amplifier in All Modes 10                                                                      |

|   | 6.9  | Speaker Amplifier in Stereo Bridge Tied Load (BTL)<br>Mode                                             |

|   | 6.10 |                                                                                                        |

|   | 6.11 | I <sup>2</sup> C Control Port 15                                                                       |

|   | 6.12 | Typical Idle, Mute, Shutdown, Operational Power<br>Consumption                                         |

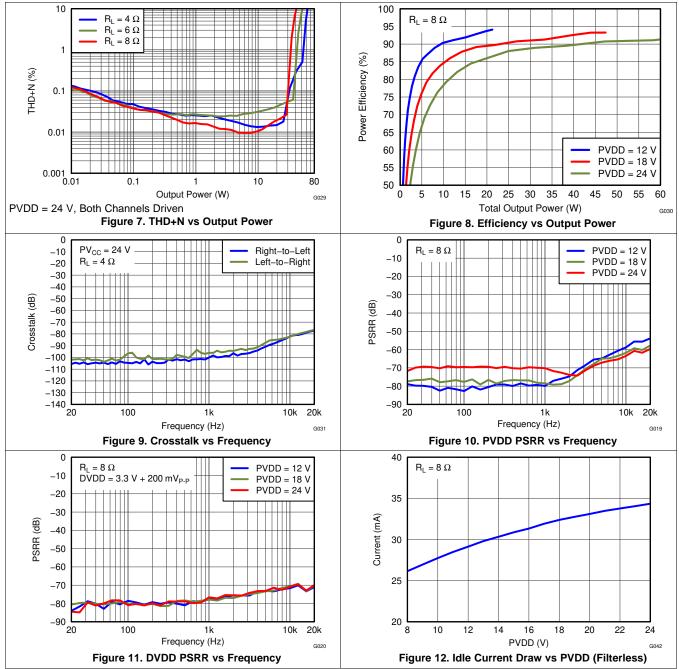

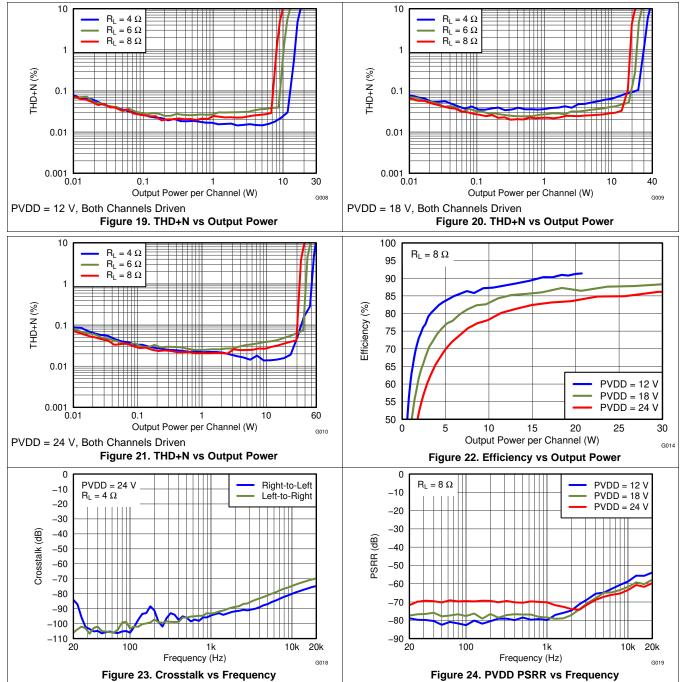

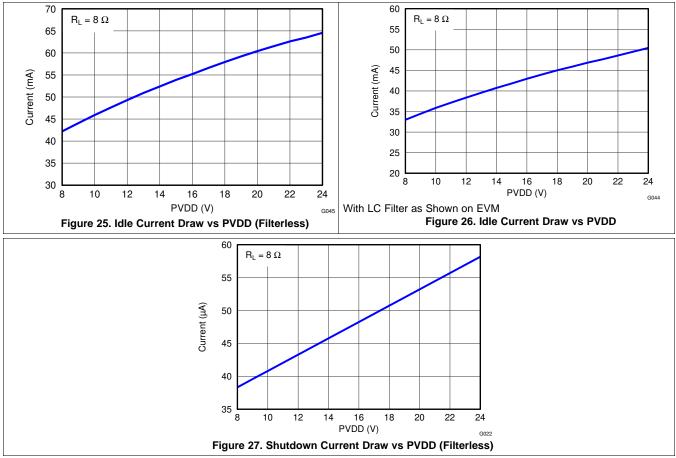

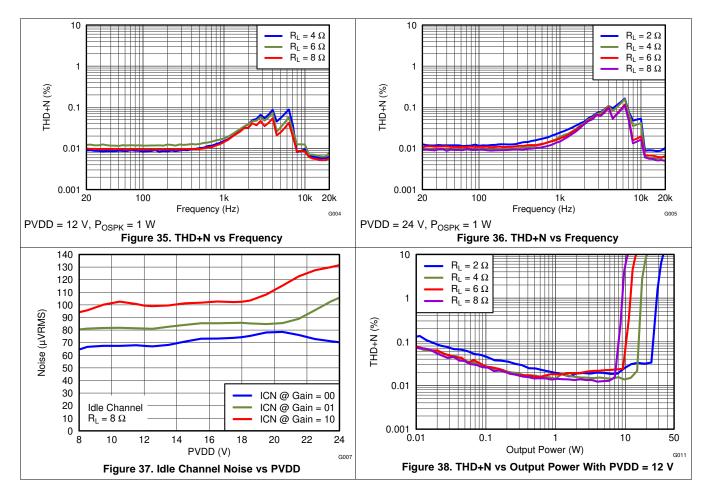

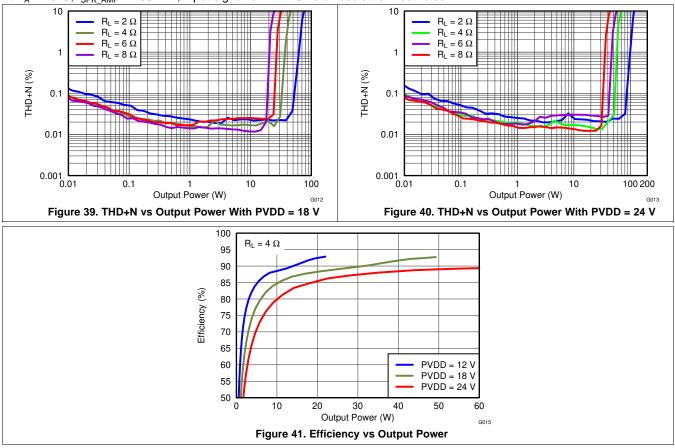

|   | 6.13 | Typical Characteristics (Stereo BTL Mode):<br>f <sub>SPK_AMP</sub> = 384 kHz                           |

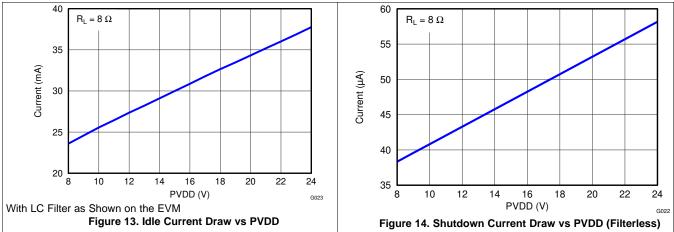

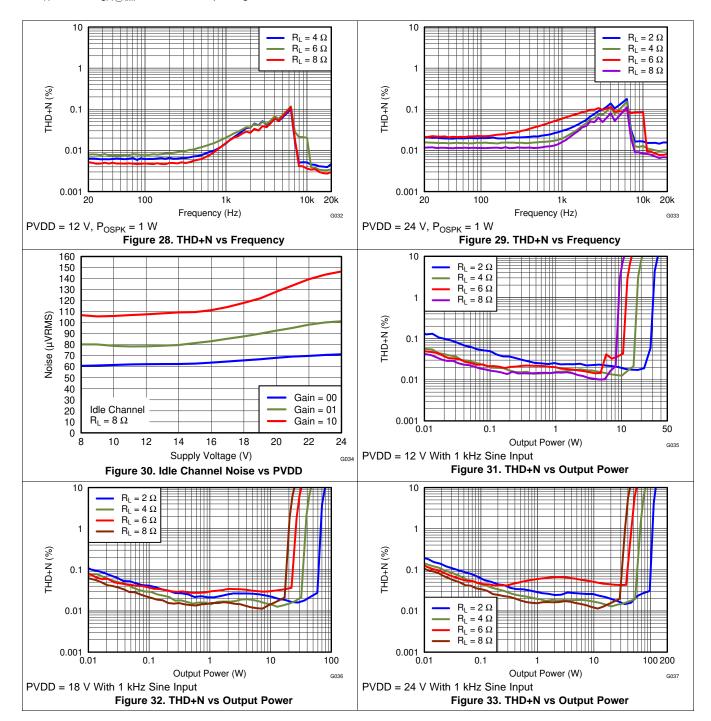

|   | 6.14 | Typical Characteristics (Stereo BTL Mode):<br>f <sub>SPK_AMP</sub> = 768 kHz                           |

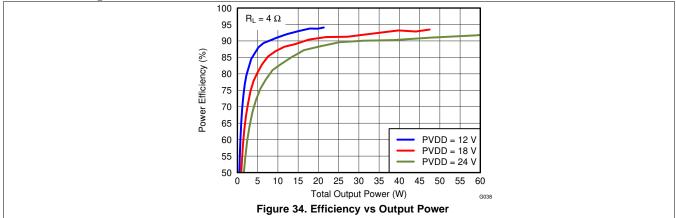

|   | 6.15 | <ul> <li>Typical Characteristics (Mono PBTL Mode):</li> <li>f<sub>SPK_AMP</sub> = 384 kHz25</li> </ul> |

|    | 6.16  | Typical Characteristics (Mono PBTL Mode): |    |

|----|-------|-------------------------------------------|----|

|    |       | f <sub>SPK_AMP</sub> = 768 kHz            |    |

| 7  |       | meter Measurement Information             |    |

| 8  | Deta  | iled Description                          | 28 |

|    | 8.1   | Overview                                  | 28 |

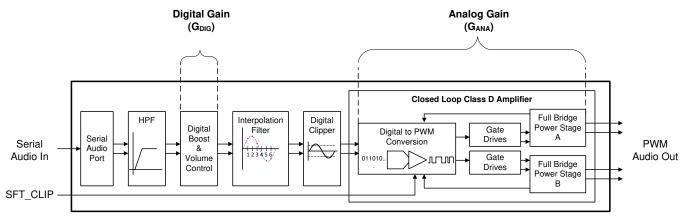

|    | 8.2   | Functional Block Diagram                  | 28 |

|    | 8.3   | Feature Description                       | 29 |

|    | 8.4   | Device Functional Modes                   | 33 |

|    | 8.5   | Register Maps                             | 42 |

| 9  | Appl  | ication and Implementation                | 50 |

|    | 9.1   | Application Information                   | 50 |

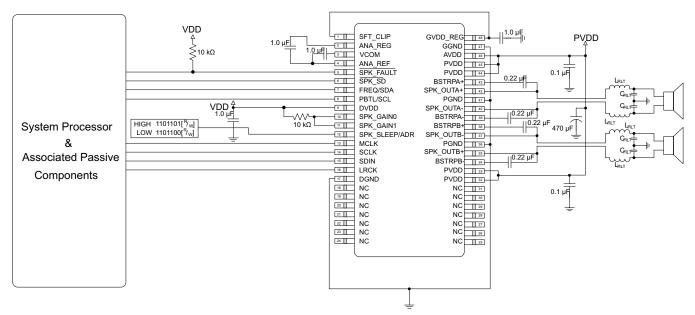

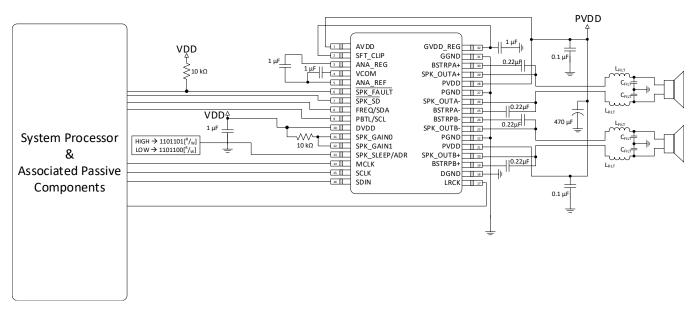

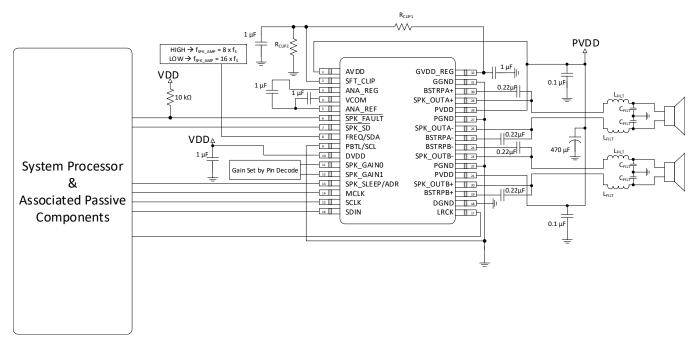

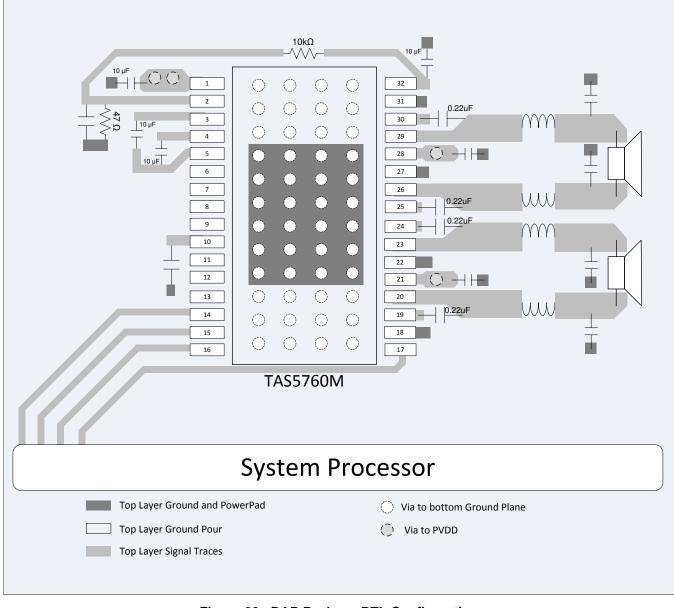

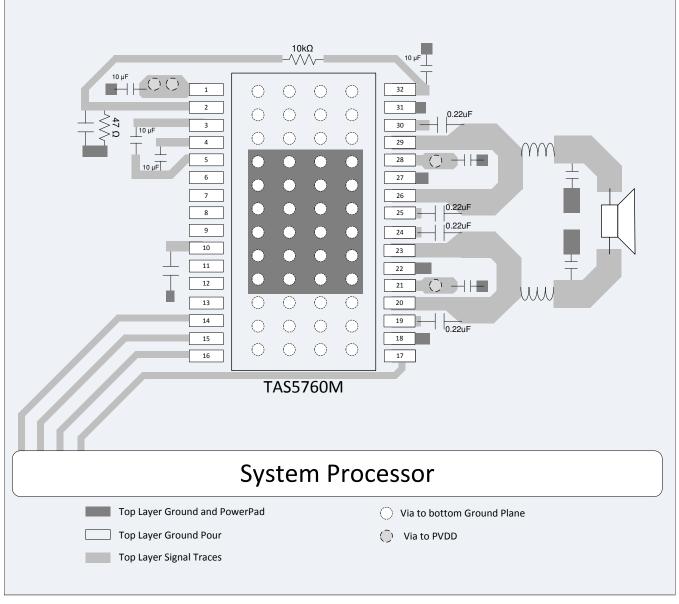

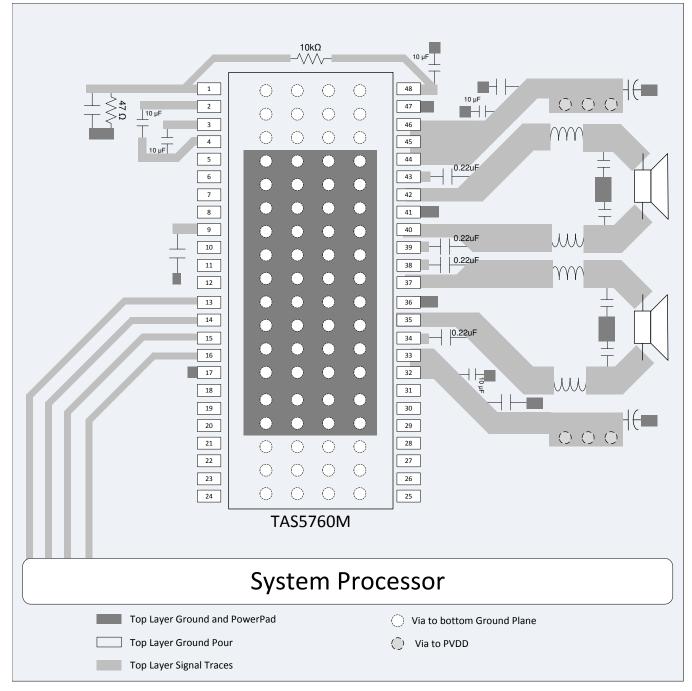

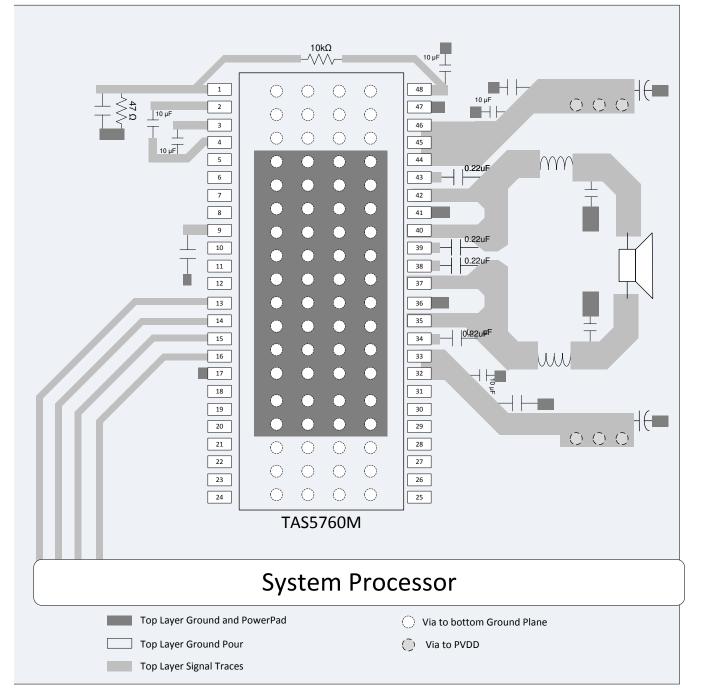

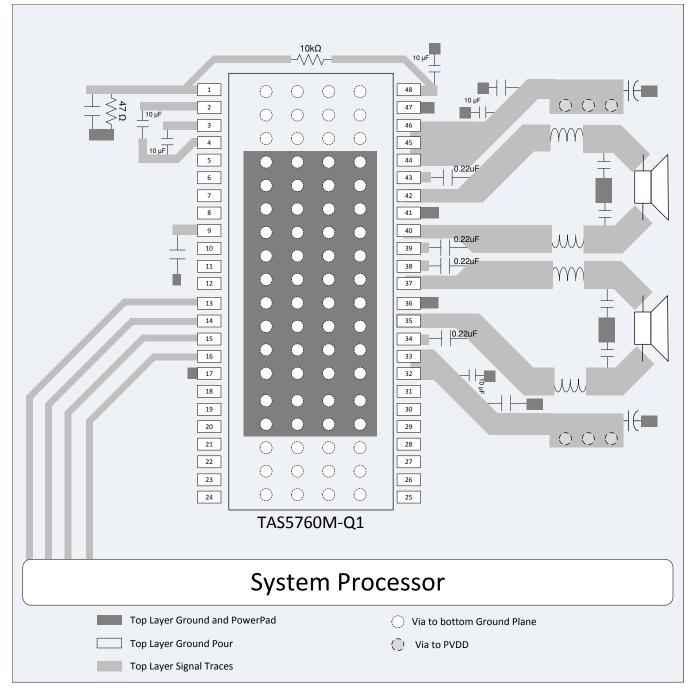

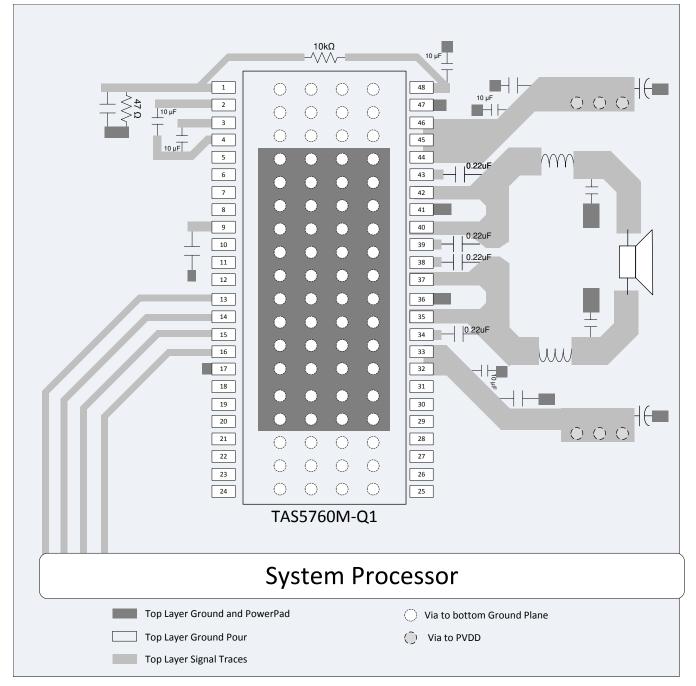

|    | 9.2   | Typical Applications                      | 50 |

| 10 | Pow   | er Supply Recommendations                 | 64 |

|    | 10.1  |                                           |    |

|    | 10.2  | PVDD Supply                               | 64 |

| 11 | Layo  | out                                       | 64 |

|    | 11.1  |                                           |    |

|    | 11.2  | Layout Example                            | 67 |

| 12 | Devi  | ice and Documentation Support             | 73 |

|    | 12.1  |                                           |    |

|    | 12.2  | Support Resources                         |    |

|    | 12.3  | Trademarks                                | 73 |

|    | 12.4  | Electrostatic Discharge Caution           | 73 |

|    | 12.5  |                                           |    |

| 13 |       | hanical, Packaging, and Orderable         |    |

|    | Infor | mation                                    | 73 |

|    |       |                                           |    |

# **4** Revision History

2

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision E (May 2017) to Revision F                | Page |

|---|----------------------------------------------------------------|------|

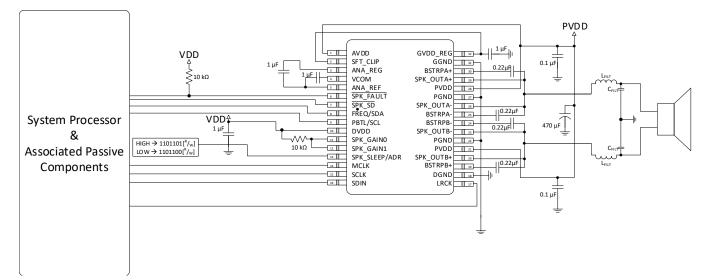

| • | Changed the pin numbers in Figure 62 From: 19 - 48 To: 17 - 32 | 54   |

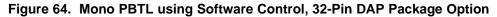

| • | Changed the pin numbers in Figure 63 From: 19 - 48 To: 17 - 32 | 57   |

| • | Changed the pin numbers in Figure 64 From: 19 - 48 To: 17 - 32 | 59   |

| • | Changed the pin numbers in Figure 65 From: 19 - 48 To: 17 - 32 | 62   |

| C | Changes from Revision D (July 2015) to Revision E     Page     Updated the Register Map section to the new format. No new data added |    |  |  |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| • | Updated the Register Map section to the new format. No new data added                                                                | 43 |  |  |  |

| • | Deleted statement of 64-kHz sample rate                                                                                              | 44 |  |  |  |

# Changes from Revision C (October 2013) to Revision D

Submit Documentation Feedback

Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

www.ti.com

Page

# Changes from Revision B (July 2013) to Revision C Page • Changed Figure 64 59 • Changed Figure 65 62

#### Changes from Revision A (July 2013) to Revision B

## Page

Page

| • | Changed Features list item, Audio Performance From: $R_{LOAD} = 8\Omega$ To: $R_{SPK} = 8\Omega$ | 1  |

|---|--------------------------------------------------------------------------------------------------|----|

| • | Changed the Stereo BTL Using Software Control to remove the 48-Pin information                   | 54 |

| • | Changed the Stereo BTL Using Hardware Control to remove the 48-Pin information                   | 57 |

| • | Changed the Mono PBTL Using Software Control to remove the 48-Pin information                    | 59 |

| • | Changed the Figure 65 to remove the 48-Pin information                                           | 62 |

|   |                                                                                                  |    |

# Changes from Original (May 2013) to Revision A

Texas Instruments

www.ti.com

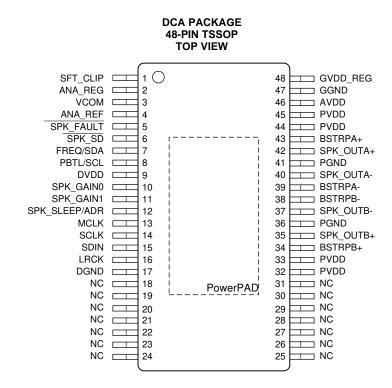

# 5 Pin Configuration and Functions

#### **Pin Functions**

|          |     | TYPE <sup>(1)</sup> |                      | DECODIDITION                                                                                                                                                                                     |  |  |

|----------|-----|---------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO. | ITPE()              | INTERNAL TERMINATION | DESCRIPTION                                                                                                                                                                                      |  |  |

| AVDD     | 46  | Р                   | -                    | Power supply for internal analog circuitry                                                                                                                                                       |  |  |

| ANA_REF  | 4   | Р                   | -                    | Connection point for internal reference used by ANA_REG and VCOM filter capacitors                                                                                                               |  |  |

| ANA_REG  | 2   | Р                   | -                    | Voltage regulator derived from AVDD supply (NOTE: This terminal is provided as a connection point for filtering capacitors for this supply and must not be used to power any external circuitry) |  |  |

| BSTRPA-  | 39  | Р                   | -                    | Connection point for the SPK_OUTA- bootstrap capacitor, which is used to create a power supply for the high-side gate drive for SPK_OUTA-                                                        |  |  |

| BSTRPA+  | 43  | Р                   | -                    | Connection point for the SPK_OUTA+ bootstrap capacitor, which is used to create a power supply for the high-side gate drive for SPK_OUTA                                                         |  |  |

| BSTRPB-  | 38  | Р                   | -                    | Connection point for the SPK_OUTB- bootstrap capacitor, which is used to create a power supply for the high-side gate drive for SPK_OUTB-                                                        |  |  |

| BSTRPB+  | 34  | Р                   | -                    | Connection point for the SPK_OUTB+ bootstrap capacitor, which is used to create a power supply for the high-side gate drive for SPK_OUTB+                                                        |  |  |

| DGND     | 17  | G                   | -                    | Ground for digital circuitry (NOTE: This pin should be connected to the system ground)                                                                                                           |  |  |

| DVDD     | 9   | Р                   | -                    | Power supply for the internal digital circuitry                                                                                                                                                  |  |  |

| FREQ/SDA | 7   | DI                  | Weak Pull-Down       | Dual function pin that functions as an I <sup>2</sup> C data input pin in I <sup>2</sup> C Control Mode or as a Frequency Select terminal when in Hardware Control Mode.                         |  |  |

| GGND     | 47  | G                   | -                    | Ground for gate drive circuitry (this terminal should be connected to the system ground)                                                                                                         |  |  |

| GVDD_REG | 48  | Р                   | -                    | Voltage regulator derived from PVDD supply (NOTE: This pin is provided as a connection point for filtering capacitors for this supply and must not be used to power any external circuitry)      |  |  |

| LRCK     | 16  | DI                  | Weak Pull-Down       | Word select clock for the digital signal that is active on the serial port's input data line                                                                                                     |  |  |

(1) AI = Analog input, AO = Analog output, DI = Digital Input, DO = Digital Output, P = Power, G = Ground (0 V)

# Pin Functions (continued)

| PIN               |                         |        | TYPE <sup>(1)</sup> INTERNAL TERMINATION |                                                                                                                                                                                                                                                                     | DESCRIPTION |  |  |

|-------------------|-------------------------|--------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| NAME              | NO.                     | ITPE'' | INTERNAL TERMINATION                     | DESCRIPTION                                                                                                                                                                                                                                                         |             |  |  |

| MCLK              | 13                      | DI     | Weak Pull-Down                           | Master Clock used for internal clock tree, sub-circuit/state machine, and Serial Audio Port clocking                                                                                                                                                                |             |  |  |

| NC                | 18-<br>31               | -      | -                                        | Not connected inside the device (all "no connect" pins should be connected<br>o ground for best thermal performance, however they can be used as<br>outing channels if required.)                                                                                   |             |  |  |

| PBTL/SCL          | 8                       | DI     | Weak Pull-Down                           | Dual function pin that functions as an I <sup>2</sup> C clock input terminal in I <sup>2</sup> C Control<br>Mode or configures the device to operate in pre-filter Parallel Bridge Tied<br>Load (PBTL) mode when in Hardware Control Mode                           |             |  |  |

| PGND              | 36,<br>41               | G      | -                                        | Ground for power device circuitry (NOTE: This terminal should be connected to the system ground)                                                                                                                                                                    |             |  |  |

| PVDD              | 32,<br>33,<br>44,<br>45 | Ρ      | -                                        | Power Supply for internal power circuitry                                                                                                                                                                                                                           |             |  |  |

| SCLK              | 14                      | DI     | Weak Pull-Down                           | Bit clock for the digital signal that is active on the serial data port's input data line                                                                                                                                                                           |             |  |  |

| SDIN              | 15                      | DI     | Weak Pull-Down                           | Data line to the serial data port                                                                                                                                                                                                                                   |             |  |  |

| SFT_CLIP          | 1                       | AI     | -                                        | sets the maximum output voltage before clipping                                                                                                                                                                                                                     |             |  |  |

| SPK_FAULT         | 5                       | DO     | -                                        | Speaker amplifier fault terminal, which is pulled LOW when an internal fault occurs                                                                                                                                                                                 |             |  |  |

| SPK_GAIN0         | 10                      | DI     | Weak Pull-Down                           | Adjusts the LSB of the multi-bit gain of the speaker amplifier                                                                                                                                                                                                      |             |  |  |

| SPK_GAIN1         | 11                      | DI     | Weak Pull-Down                           | Adjusts the MSB of the multi-bit gain of the speaker amplifier                                                                                                                                                                                                      |             |  |  |

| SPK_SLEEP/<br>ADR | 12                      | DI     | Weak Pull-Up                             | In Hardware Control Mode, places the speaker amplifier in sleep mode. In Software Control Mode, is used to determine the I <sup>2</sup> C Address of the device                                                                                                     |             |  |  |

| SPK_OUTA-         | 40                      | AO     | -                                        | Negative pin for differential speaker amplifier output A                                                                                                                                                                                                            |             |  |  |

| SPK_OUTA+         | 42                      | AO     | -                                        | Positive pin for differential speaker amplifier output A                                                                                                                                                                                                            |             |  |  |

| SPK_OUTB-         | 37                      | AO     | -                                        | Negative pin for differential speaker amplifier output B                                                                                                                                                                                                            |             |  |  |

| SPK_OUTB+         | 35                      | AO     | -                                        | Positive pin for differential speaker amplifier output B                                                                                                                                                                                                            |             |  |  |

| SPK_SD            | 6                       | AO     | -                                        | Places the speaker amplifier in shutdown                                                                                                                                                                                                                            |             |  |  |

| VCOM              | 3                       | Р      | -                                        | Bias voltage for internal PWM conversion block                                                                                                                                                                                                                      |             |  |  |

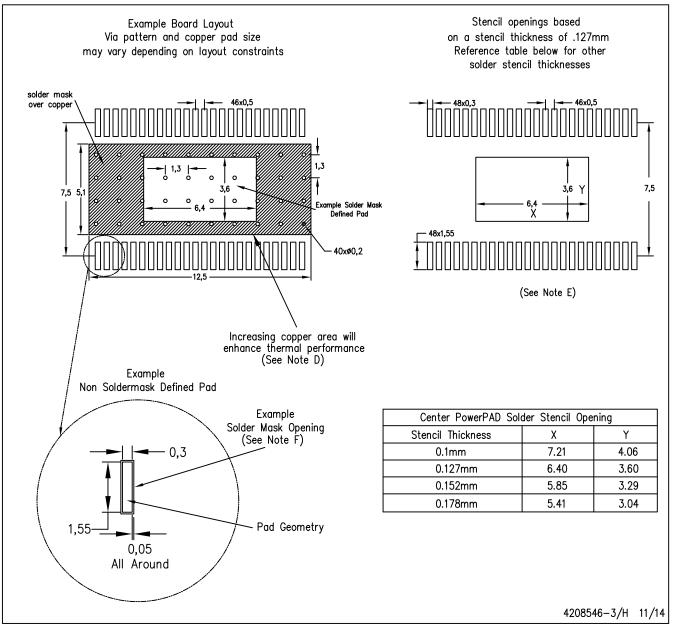

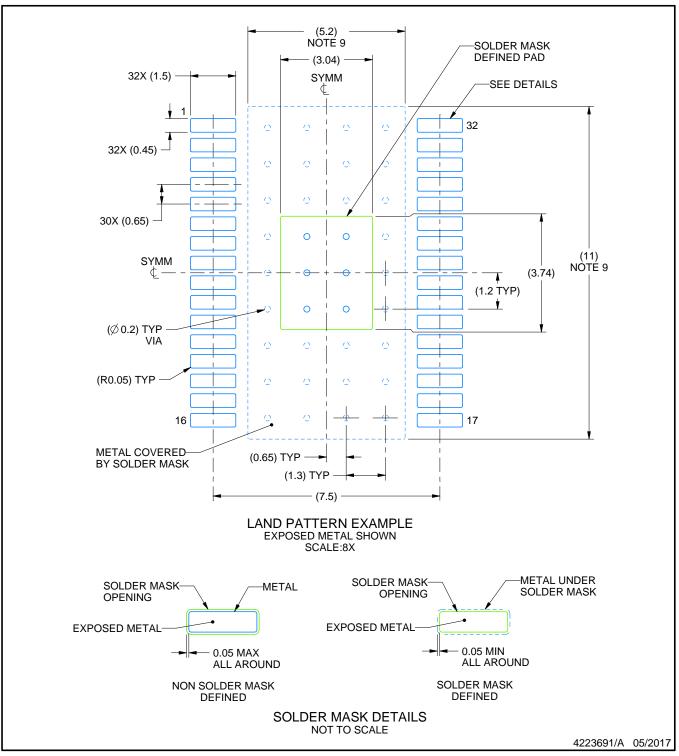

| PowerPAD™         | -                       | G      | -                                        | Provides both electrical and thermal connection from the device to the board. A matching ground pad must be provided on the PCB and the device connected to it via solder. For proper electrical operation, this ground pad must be connected to the system ground. |             |  |  |

Texas Instruments

www.ti.com

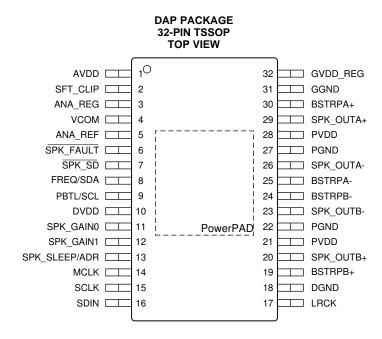

#### **Pin Functions**

| PIN      |     | TYP INTERNAL     |                | DESCRIPTION                                                                                                                                                                                                                              |  |

|----------|-----|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO. | E <sup>(1)</sup> | TERMINATION    | DESCRIPTION                                                                                                                                                                                                                              |  |

| AVDD     | 1   | Р                | -              | Power supply for internal analog circuitry                                                                                                                                                                                               |  |

| ANA_REF  | 5   | Ρ                | -              | Connection point for internal reference used by ANA_REG and VCOM filter capacitors                                                                                                                                                       |  |

| ANA_REG  | 3   | Ρ                | -              | Voltage regulator derived from AVDD supply (NOTE: This terminal is provided<br>as a connection point for filtering capacitors for this supply and must not be<br>used to power any external circuitry)                                   |  |

| BSTRPA-  | 25  | Ρ                | -              | Connection point for the SPK_OUTA– bootstrap capacitor, which is used to create a power supply for the high-side gate drive for SPK_OUTA–                                                                                                |  |

| BSTRPA+  | 30  | Ρ                | -              | Connection point for the SPK_OUTA+ bootstrap capacitor, which is used to create a power supply for the high-side gate drive for SPK_OUTA                                                                                                 |  |

| BSTRPB-  | 24  | Ρ                | -              | Connection point for the SPK_OUTB- bootstrap capacitor, which is used to create a power supply for the high-side gate drive for SPK_OUTB-                                                                                                |  |

| BSTRPB+  | 19  | Ρ                | -              | Connection point for the SPK_OUTB+ bootstrap capacitor, which is used to create a power supply for the high-side gate drive for SPK_OUTB+                                                                                                |  |

| DGND     | 18  | G                | -              | Ground for digital circuitry (NOTE: This terminal should be connected to the system ground)                                                                                                                                              |  |

| DVDD     | 10  | Р                | -              | Power supply for the internal digital circuitry                                                                                                                                                                                          |  |

| FREQ/SDA | 8   | DI               | Weak Pull-Down | Dual function terminal that functions as an I <sup>2</sup> C data input terminal in I <sup>2</sup> C Control<br>Mode or as a Frequency Select terminal when in Hardware Control Mode.                                                    |  |

| GGND     | 31  | G                | -              | Ground for gate drive circuitry (this terminal should be connected to the system ground)                                                                                                                                                 |  |

| GVDD_REG | 32  | Ρ                | -              | Voltage regulator derived from PVDD supply (NOTE: This terminal is provided<br>as a connection point for filtering capacitors for this supply and must not be<br>used to power any external circuitry)                                   |  |

| LRCK     | 17  | DI               | Weak Pull-Down | Word select clock for the digital signal that is active on the serial port's input data line                                                                                                                                             |  |

| MCLK     | 14  | DI               | Weak Pull-Down | Master Clock used for internal clock tree, sub-circuit/state machine, and Serial Audio Port clocking                                                                                                                                     |  |

| PBTL/SCL | 9   | DI               | Weak Pull-Down | Dual function terminal that functions as an I <sup>2</sup> C clock input terminal in I <sup>2</sup> C Control Mode or configures the device to operate in pre-filter Parallel Bridge Tied Load (PBTL) mode when in Hardware Control Mode |  |

(1) AI = Analog input, AO = Analog output, DI = Digital Input, DO = Digital Output, P = Power, G = Ground (0 V)

Copyright © 2013-2020, Texas Instruments Incorporated

# **Pin Functions (continued)**

| PIN               |        | TYP INTERNAL     |                | DESCRIPTION                                                                                                                                                                |  |

|-------------------|--------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME              | NO.    | E <sup>(1)</sup> | TERMINATION    | DESCRIPTION                                                                                                                                                                |  |

| PGND              | 22, 27 | G                | -              | Ground for power device circuitry (NOTE: This terminal should be connected to the system ground)                                                                           |  |

| PVDD              | 21, 28 | Ρ                | -              | Power Supply for internal power circuitry                                                                                                                                  |  |

| SCLK              | 15     | DI               | Weak Pull-Down | Bit clock for the digital signal that is active on the serial data port's input data line                                                                                  |  |

| SDIN              | 16     | DI               | Weak Pull-Down | Data line to the serial data port                                                                                                                                          |  |

| SFT_CLIP          | 2      | AI               | -              | Sets the maximum output voltage before clipping                                                                                                                            |  |

| SPK_FAULT         | 6      | DO               | Open Drain     | Fault terminal, which is pulled LOW when an internal fault occurs                                                                                                          |  |

| SPK_GAIN0         | 11     | DI               | Weak Pull-Down | Adjusts the LSB of the multi-bit gain of the speaker amplifier                                                                                                             |  |

| SPK_GAIN1         | 12     | DI               | Weak Pull-Down | Adjusts the MSB of the multi-bit gain of the speaker amplifier                                                                                                             |  |

| SPK_SLEEP/<br>ADR | 13     | DI               | Weak Pull-Up   | Places the speaker amplifier in mute                                                                                                                                       |  |

| SPK_OUTA-         | 26     | AO               | -              | Negative terminal for differential speaker amplifier output                                                                                                                |  |

| SPK_OUTA+         | 29     | AO               | -              | Positive terminal for differential speaker amplifier output                                                                                                                |  |

| SPK_OUTB-         | 23     | AO               | -              | Negative terminal for differential speaker amplifier output B                                                                                                              |  |

| SPK_OUTB+         | 20     | AO               | -              | Positive terminal for differential speaker amplifier output B                                                                                                              |  |

| SPK_SD            | 7      | DI               | -              | Places the device in shutdown when pulled LOW                                                                                                                              |  |

| VCOM              | 4      | Р                | -              | Bias voltage for internal PWM conversion block                                                                                                                             |  |

| PowerPAD™         | -      | G                | -              | Provides both electrical and thermal connection from the device to the board. A matching ground pad must be provided on the PCB and the device connected to it via solder. |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                           |                                                     | MIN  | MAX        | UNIT |

|-------------------------------------------|-----------------------------------------------------|------|------------|------|

|                                           | Ambient Operating Temperature, T <sub>A</sub>       | -25  | 85         | °C   |

| Temperature                               | Ambient Storage Temperature, T <sub>S</sub>         | -40  | 125        | °C   |

|                                           | Junction Temperature, T <sub>J</sub>                | -40  | 150        | °C   |

|                                           | AVDD Supply                                         | -0.3 | 30         | V    |

| Supply Voltage                            | PVDD Supply                                         | -0.3 | 30         | V    |

|                                           | DVDD Supply                                         | -0.3 | 4          | V    |

| DVDD Referenced Digital<br>Input Voltages | Digital Inputs referenced to DVDD supply            | -0.5 | DVDD + 0.5 | V    |

| Speaker Amplifier Output<br>Voltage       | V <sub>SPK_OUTxx</sub> , measured at the output pin | -0.3 | 32         | V    |

| Storage temperature range,                | T <sub>stg</sub>                                    | -40  | 125        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

SLOS772F - JULY 2013-REVISED FEBRUARY 2020

www.ti.com

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         |                                                     | MIN | NOM  | MAX  | UNIT |

|-------------------------|-----------------------------------------------------|-----|------|------|------|

| T <sub>A</sub>          | Ambient Operating Temperature                       | -25 |      | 85   | °C   |

| AVDD                    | AVDD Supply                                         | 4.5 |      | 26.4 | V    |

| PVDD                    | PVDD Supply                                         | 4.5 |      | 26.4 | V    |

| DVDD                    | DVDD Supply                                         | 2.8 |      | 3.63 | V    |

| VIH <sub>(DR)</sub>     | Input Logic HIGH for DVDD Referenced Digital Inputs |     | DVDD |      | V    |

| VIL <sub>(DR)</sub>     | Input Logic LOW for DVDD Referenced Digital Inputs  |     | 0    |      | V    |

| R <sub>SPK (BTL)</sub>  | Minimum Speaker Load in BTL Mode                    | 4   |      |      | Ω    |

| R <sub>SPK (PBTL)</sub> | Minimum Speaker Load in PBTL Mode                   | 2   |      |      | Ω    |

# 6.4 Digital I/O Pins

Test conditions (unless otherwise noted):  $T_C = 25^{\circ}C$

|                  | PARAMETER                                                        | TEST CONDITIONS         | MIN | TYP | MAX | UNIT  |

|------------------|------------------------------------------------------------------|-------------------------|-----|-----|-----|-------|

| V <sub>IH1</sub> | Input Logic HIGH threshold for DVDD<br>Referenced Digital Inputs | All digital pins        | 70  |     |     | %DVDD |

| V <sub>IL1</sub> | Input Logic LOW threshold for DVDD<br>Referenced Digital Inputs  | All digital pins        |     |     | 30  | %DVDD |

| I <sub>IH1</sub> | Input Logic HIGH Current Level                                   | All digital pins        |     |     | 15  | μA    |

| I <sub>IL1</sub> | Input Logic LOW Current Level                                    | All digital pins        |     |     | -15 | μA    |

| V <sub>OH</sub>  | Output Logic HIGH Voltage Level                                  | I <sub>OH</sub> = 2 mA  | 90  |     |     | %DVDD |

| V <sub>OL</sub>  | Output Logic LOW Voltage Level                                   | I <sub>OH</sub> = -2 mA |     |     | 10  | %DVDD |

# 6.5 Master Clock

Test conditions (unless otherwise noted):  $T_C = 25^{\circ}C$

|                   | PARAMETER                  | TEST CONDITIONS                             | MIN | TYP | MAX | UNIT           |

|-------------------|----------------------------|---------------------------------------------|-----|-----|-----|----------------|

| D <sub>MCLK</sub> | Allowable MCLK Duty Cycle  |                                             | 45% | 50% | 55% |                |

| f <sub>MCLK</sub> | Supported MCLK Frequencies | Values include: 128, 192, 256,<br>384, 512. | 128 |     | 512 | f <sub>S</sub> |

# 6.6 Serial Audio Port

Test conditions (unless otherwise noted):  $T_C = 25^{\circ}C$

|                   | PARAMETER                                         | TEST CONDITIONS                                                                                                                  | MIN | TYP | MAX | UNIT           |

|-------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----------------|

| D <sub>SCLK</sub> | Allowable SCLK Duty Cycle                         |                                                                                                                                  | 45% | 50% | 55% |                |

|                   | Required LRCK to SCLK Rising Edge                 |                                                                                                                                  | 15  |     |     | ns             |

| t <sub>HLD</sub>  | Required SDIN Hold Time after SCLK<br>Rising Edge |                                                                                                                                  | 15  |     |     | ns             |

| t <sub>su</sub>   | Required SDIN Setup Time before SCLK Rising Edge  |                                                                                                                                  | 15  |     |     | ns             |

| f <sub>S</sub>    | Supported Input Sample Rates                      | Sample rates above 48kHz<br>supported by "double speed<br>mode," which is activated<br>through the I <sup>2</sup> C control port | 32  |     | 96  | kHz            |

| f <sub>SCLK</sub> | Supported SCLK Frequencies                        | Values include: 32, 48, 64                                                                                                       | 32  |     | 64  | f <sub>S</sub> |

# 6.7 Protection Circuitry

# Test conditions (unless otherwise noted): $T_C = 25^{\circ}C$

|                             | PARAMETER                                             | TEST CONDITIONS                   | MIN TYP | MAX | UNIT |

|-----------------------------|-------------------------------------------------------|-----------------------------------|---------|-----|------|

| OVE <sub>RTHRES(PVDD)</sub> | PVDD Overvoltage Error Threshold                      | PVDD Rising                       | 28      |     | V    |

| OVE <sub>FTHRES(PVDD)</sub> | PVDD Overvoltage Error Threshold                      | PVDD Falling                      | 27.3    |     | V    |

| UVE <sub>FTHRES(PVDD)</sub> | PVDD Undervoltage Error (UVE)<br>Threshold            | PVDD Falling                      | 3.95    |     | V    |

| UVE <sub>RTHRES(PVDD)</sub> | PVDD UVE Threshold (PVDD Rising)                      | PVDD Rising                       | 4.15    |     | V    |

| OTE <sub>THRES</sub>        | Overtemperature Error (OTE)<br>Threshold              |                                   | 150     |     | °C   |

| OTE <sub>HYST</sub>         | Overtemperature Error (OTE)<br>Hysteresis             |                                   | 15      |     | °C   |

| OCE <sub>THRES</sub>        | Overcurrent Error (OCE) Threshold for each BTL Output | PVDD= 15V, T <sub>A</sub> = 25 °C | 7       |     | А    |

| DCE <sub>THRES</sub>        | DC Error (DCE) Threshold                              | PVDD= 12V, T <sub>A</sub> = 25 °C | 2.6     |     | V    |

| <b></b>                     | Speaker Amplifier Fault Time Out                      | DC Detect Error                   | 650     |     | ms   |

| SPK_FAULT                   | period                                                | OTE or OCP Fault                  | 1.3     |     | S    |

STRUMENTS

EXAS

# 6.8 Speaker Amplifier in All Modes

Test conditions (unless otherwise noted):  $T_{C}$  = 25°C

|                         | PARAMETER                                                      | TEST CONDITIONS                                                                                             | MIN TYP                    | MAX | UNIT           |

|-------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------|-----|----------------|

| AV <sub>00</sub>        | Speaker Amplifier Gain with<br>SPK_GAIN[1:0] Pins = 00         | Hardware Control Mode<br>(Additional gain settings<br>available in Software Control<br>Mode) <sup>(1)</sup> | 25.2                       |     | dBV            |

| AV <sub>01</sub>        | Speaker Amplifier Gain with<br>SPK_GAIN[1:0] Pins = 01         | Hardware Control Mode<br>(Additional gain settings<br>available in Software Control<br>Mode) <sup>(1)</sup> | 28.6                       |     | dBV            |

| AV <sub>10</sub>        | Speaker Amplifier Gain with<br>SPK_GAIN[1:0] Pins = 10         | Hardware Control Mode<br>(Additional gain settings<br>available in Software Control<br>Mode) <sup>(1)</sup> | 31                         |     | dBV            |

| AV <sub>11</sub>        | Speaker Amplifier Gain with<br>SPK_GAIN[1:0] Pins = 11         | (This setting places the device in Software Control Mode)                                                   | (Set via I <sup>2</sup> C) |     |                |

| VOS  <sub>(SPK_</sub>   | Speaker Amplifier DC Offset                                    | BTL, Worst case over voltage, gain settings                                                                 |                            | 10  | mV             |

| AMP)                    |                                                                | PBTL, Worst case over voltage, gain settings                                                                |                            | 15  | mV             |

| f <sub>SPK_AMP(0)</sub> | Speaker Amplifier Switching Frequency when PWM_FREQ Pin = 0    | (Hardware Control Mode.<br>Additional switching rates<br>available in Software Control<br>Mode.)            | 16                         |     | f <sub>S</sub> |

| f <sub>SPK_AMP(1)</sub> | Speaker Amplifier Switching Frequency<br>when PWM_FREQ Pin = 1 | (Hardware Control Mode.<br>Additional switching rates<br>available in Software Control<br>Mode.)            | 8                          |     | f <sub>S</sub> |

|                         |                                                                | PVDD = 15 V, TA = 25 °C, Die<br>Only                                                                        | 120                        |     | mΩ             |

| R <sub>DS(ON)</sub>     | On Resistance of Output MOSFET (both high-side and low-side)   | PVDD= 15V, TA = 25 °C,<br>Includes: Die, Bond Wires,<br>Leadframe                                           | 150                        |     | mΩ             |

| ,                       |                                                                | f <sub>S</sub> = 44.1 kHz                                                                                   | 3.7                        |     |                |

|                         | –3-dB Corner Frequency of High-Pass                            | f <sub>S</sub> = 48 kHz                                                                                     | 4                          |     | <b>Ц</b> -7    |

| f <sub>C</sub>          | Filter                                                         | f <sub>S</sub> = 88.2 kHz                                                                                   | 7.4                        |     | Hz             |

|                         |                                                                | f <sub>S</sub> = 96 kHz                                                                                     | 8                          |     |                |

(1) The digital boost block contributes +6dB of gain to this value. The audio signal must be kept below -6dB to avoid clipping the digital audio path.

# 6.9 Speaker Amplifier in Stereo Bridge Tied Load (BTL) Mode

Test conditions (unless otherwise noted):  $T_c = 25^{\circ}C$ , input signal is 1 kHz Sine

|                      | PARAMETER                            | TEST CONDITIONS                                                                                                                                                                                                | MIN TYP | MAX | UNIT   |

|----------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------|

|                      |                                      | $\label{eq:pvdd} \begin{array}{l} PVDD = 12 \; V, \; SPK\_GAIN[1:0] \; Pins = 00, \\ R_{SPK} = 8 \; \Omega, \; A\text{-Weighted} \end{array}$                                                                  | 66      |     |        |

| ICN <sub>(SPK)</sub> |                                      | $\begin{array}{l} PVDD = 15 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8 \ \Omega, \ A\text{-Weighted} \end{array}$                                                                                       | 75      |     | u)/rmc |

|                      | Idle Channel Noise                   | $\begin{array}{l} \mbox{PVDD} = \mbox{19 V, SPK\_GAIN[1:0] Pins} = \mbox{01,} \\ \mbox{R}_{SPK} = \mbox{8}\ \Omega, \mbox{ A-Weighted} \end{array}$                                                            | 79      |     | µVrms  |

|                      |                                      | PVDD = 24 V, SPK_GAIN[1:0] Pins =10,<br>$R_{SPK}$ = 8 $\Omega$ , A-Weighted                                                                                                                                    | 120     |     |        |

|                      |                                      | $\label{eq:pvdd} \begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 4 \ \Omega, \ THD+N = 0.1\%, \end{array}$                                                                          | 14.2    |     |        |

|                      |                                      | $\begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 8 \ \Omega, \ THD+N = 0.1\% \end{array}$                                                                                           | 8       |     |        |

|                      |                                      | $\begin{array}{l} PVDD = 15 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 4 \ \Omega, \ THD+N = 0.1\%, \end{array}$                                                                                          | 21.9    |     |        |

| Pour                 | Maximum Instantaneous                | $\begin{array}{l} PVDD = 15 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8 \ \Omega, \ THD+N = 0.1\% \end{array}$                                                                                           | 12.5    |     | ۱۸/    |

| Po <sub>(SPK)</sub>  | Output Power Per. Ch.                | $\begin{array}{l} \mbox{PVDD} = \mbox{19 V}, \mbox{SPK}\_GAIN[1:0] \mbox{Pins} = \mbox{01}, \\ \mbox{R}_{\mbox{SPK}} = \mbox{4} \ \Omega, \ \mbox{THD} \mbox{+} \mbox{N} = \mbox{0.1\%}, \end{array}$          | 33.5    |     | W      |

|                      |                                      | $\begin{array}{l} PVDD = 19 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8 \ \Omega, \ THD{+}N = 0.1\% \end{array}$                                                                                         | 20      |     |        |

|                      |                                      | $\begin{array}{l} PVDD = 24 \; V, \; SPK\_GAIN[1:0] \; Pins = 10, \\ R_{SPK} = 4 \; \Omega, \; THD+N = 0.1\%, \end{array}$                                                                                     | 55.2    |     |        |

|                      |                                      | PVDD = 24 V, SPK_GAIN[1:0] Pins = 10,<br>R <sub>SPK</sub> = 8 $\Omega$ , THD+N = 0.1%                                                                                                                          | 31.8    |     |        |

|                      |                                      | $\begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 4 \ \Omega, \ THD+N = 0.1\%, \end{array}$                                                                                          | 14      |     |        |

|                      |                                      | $\begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 8 \ \Omega, \ THD{+}N = 0.1\% \end{array}$                                                                                         | 8       |     |        |

|                      |                                      | $\begin{array}{l} PVDD \texttt{=} \ \texttt{15} \ V, \ SPK\_GAIN[1:0] \ Pins \texttt{=} \ \texttt{01}, \\ R_{SPK} \texttt{=} \ \texttt{4} \ \Omega, \ THD\texttt{+}N \texttt{=} \ \texttt{0.1\%}, \end{array}$ | 13.25   |     |        |

| Do                   | Maximum Continuous                   | PVDD = 15 V, SPK_GAIN[1:0] Pins = 01,<br>R_{SPK} = 8 $\Omega$ , THD+N = 0.1%                                                                                                                                   | 12.5    |     | w      |

| Po <sub>(SPK)</sub>  | Output Power Per. Ch. <sup>(1)</sup> | $\begin{array}{l} \mbox{PVDD} = \mbox{19 V}, \mbox{SPK}\_GAIN[1:0] \mbox{Pins} = \mbox{01}, \\ \mbox{R}_{\mbox{SPK}} = \mbox{4} \ \Omega, \ \mbox{THD} + \mbox{N} = \mbox{0.1\%}, \end{array}$                 | 12.25   |     | ٧V     |

|                      |                                      | $\begin{array}{l} \mbox{PVDD} = \mbox{19 V}, \mbox{SPK}\_GAIN[1:0] \mbox{Pins} = \mbox{01}, \\ \mbox{R}_{\mbox{SPK}} = \mbox{8} \ \Omega, \ \mbox{THD} + \mbox{N} = \mbox{0.1\%} \end{array}$                  | 20      |     |        |

|                      |                                      | $\begin{array}{l} PVDD = 24 \ V, \ SPK\_GAIN[1:0] \ Pins = 10, \\ R_{SPK} = 4 \ \Omega, \ THD+N = 0.1\%, \end{array}$                                                                                          | 11      |     |        |

|                      |                                      | PVDD = 24 V, SPK_GAIN[1:0] Pins = 10,<br>$R_{SPK} = 8 \Omega$ , THD+N = 0.1%                                                                                                                                   | 24      |     |        |

| SNR <sub>(SPK)</sub> |                                      | $\begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 8 \ \Omega, \ A\text{-Weighted}, \ -60dBFS \ Input \end{array}$                                                                    | 99.7    |     |        |

|                      | Signal to Noise Ratio                | $\begin{array}{l} PVDD = 15 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8 \ \Omega, \ A\text{-Weighted}, \ -60dBFS \ Input \end{array}$                                                                    | 98.2    |     | dB     |

|                      | (Referenced to THD+N =<br>1%)        | $\begin{array}{l} PVDD = 19 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8 \ \Omega, \ A\text{-Weighted}, \ -60dBFS \ Input \end{array}$                                                                    | 100.4   |     | UD     |

|                      |                                      | PVDD = 24 V, SPK_GAIN[1:0] Pins = 10,<br>R <sub>SPK</sub> = 8 $\Omega$ , A-Weighted, -60dBFS Input                                                                                                             | 98.8    |     |        |

(1) The continuous power output of any amplifier is determined by the thermal performance of the amplifier as well as limitations placed on it by the system around it, such as the PCB configuration and the ambient operating temperature. The performance characteristics listed in this section are achievable on the TAS5760M's EVM, which is representative of the popular "2 Layers / 1oz Copper" PCB configuration in a size that is representative of the amount of area often provided to the amplifier section of popular consumer audio electronics. As can be seen in the instantaneous power portion of this table, more power can be delivered from the TAS5760M if steps are taken to pull more heat out of the device. For instance, using a board with more layers or adding a small heatsink will result in an increase of continuous power, up to and including the instantaneous power level. This behavior can also been seen in the POUT vs. PVDD plots shown in the *Typical Characteristics (Stereo BTL Mode): f<sub>SPK\_AMP</sub> = 384 kHz* section of this data sheet.

ISTRUMENTS

**EXAS**

# Speaker Amplifier in Stereo Bridge Tied Load (BTL) Mode (continued)

Test conditions (unless otherwise noted):  $T_c = 25^{\circ}C$ , input signal is 1 kHz Sine

|                         | PARAMETER                                                    | TEST CONDITIONS                                                                                                   | MIN TYP MA | X UNIT |

|-------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------|--------|

|                         |                                                              | $\begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 4 \ \Omega, \ Po = 1 \ W \end{array}$ | 0.02%      |        |

|                         |                                                              | $\begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 8 \ \Omega, \ Po = 1 \ W \end{array}$ | 0.03%      |        |

|                         |                                                              | $\begin{array}{l} PVDD = 15 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 4 \ \Omega, \ Po = 1 \ W \end{array}$ | 0.03%      |        |

|                         | Total Harmonic Distortion                                    | $\begin{array}{l} PVDD = 15 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8 \ \Omega, \ Po = 1 \ W \end{array}$ | 0.03%      |        |

| THD+N <sub>(SPK)</sub>  | and Noise                                                    | $\begin{array}{l} PVDD = 19 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 4 \ \Omega, \ Po = 1 \ W \end{array}$ | 0.03%      |        |

|                         |                                                              | $\begin{array}{l} PVDD = 19 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8 \ \Omega, \ Po = 1 \ W \end{array}$ | 0.04%      |        |

|                         |                                                              | $\begin{array}{l} PVDD = 24 \ V, \ SPK\_GAIN[1:0] \ Pins = 10, \\ R_{SPK} = 4 \ \Omega, \ Po = 1 \ W \end{array}$ | 0.03%      |        |

|                         |                                                              | $\begin{array}{l} PVDD = 24 \ V, \ SPK\_GAIN[1:0] \ Pins = 10, \\ R_{SPK} = 8 \ \Omega, \ Po = 1 \ W \end{array}$ | 0.04%      |        |

|                         | Cross-talk (worst case<br>between LtoR and RtoL<br>coupling) | PVDD = 12 V, SPK_GAIN[1:0] Pins = 00,<br>R <sub>SPK</sub> = 8 $\Omega$ , Input Signal 250 mVrms, 1kHz Sine        | -92        |        |

| Y Tolk                  |                                                              | PVDD = 15 V, SPK_GAIN[1:0] Pins = 01,<br>R_{SPK} = 8 $\Omega$ , Input Signal 250 mVrms, 1kHz Sine                 | -93        | dD     |

| X-Talk <sub>(SPK)</sub> |                                                              | PVDD = 19 V, SPK_GAIN[1:0] Pins = 01,<br>R_{SPK} = 8 $\Omega$ , Input Signal 250 mVrms, 1kHz Sine                 | -94        | — dB   |

|                         |                                                              | $PVDD$ = 24 V, $SPK\_GAIN[1:0]$ Pins = 10, $R_{SPK}$ = 8 $\Omega,$ Input Signal 250 mVrms, 1kHz Sine              | -93        |        |

# 6.10 Speaker Amplifier in Mono Parallel Bridge Tied Load (PBTL) Mode

Test conditions (unless otherwise noted):  $T_c = 25^{\circ}C$ , input signal is 1 kHz Sine

|                     | PARAMETER                    | TEST CONDITIONS                                                                                                                                               | MIN TYP | MAX | UNIT  |

|---------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-------|

|                     |                              | $\label{eq:pvdd} \begin{array}{l} PVDD = 12 \; V, \; SPK\_GAIN[1:0] \; Pins = 00, \\ R_{SPK} = 8\Omega, \; A\text{-Weighted} \end{array}$                     | 69      |     |       |

| ICN                 | Idle Channel Noise           | $\begin{array}{l} PVDD = 15 \; V, \; SPK\_GAIN[1:0] \; Pins = 01, \\ R_{SPK} = 8\Omega, \; A\text{-Weighted} \end{array}$                                     | 85      |     | µVrms |

|                     |                              | $\begin{array}{l} PVDD = 19 \; V, \; SPK\_GAIN[1:0] \; Pins = 01, \\ R_{SPK} = 8\Omega, \; A\text{-Weighted} \end{array}$                                     | 85      |     | μνιπο |

|                     |                              | $\begin{array}{l} PVDD = 24 \ V, \ SPK\_GAIN[1:0] \ Pins = \! 10, \\ R_{SPK} = 8\Omega, \ A\text{-Weighted} \end{array}$                                      | 131     |     |       |

|                     |                              | $\begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 2\Omega, \ THD{+}N = 0.1\%, \end{array}$                                          | 28.6    |     |       |

|                     |                              | $\begin{array}{l} \mbox{PVDD} = 12 \mbox{ V, SPK}\_GAIN[1:0] \mbox{ Pins} = 00, \\ \mbox{R}_{\mbox{SPK}} = 4\Omega, \mbox{ THD+N} = 0.1\%, \end{array}$       | 15.9    |     |       |

|                     |                              | $\begin{array}{l} PVDD=12\;V,\;SPK\_GAIN[1:0]\;Pins=00,\\ R_{SPK}=8\Omega,\;THD{+}N=0.1\% \end{array}$                                                        | 8.4     |     |       |

|                     |                              | $\begin{array}{l} \mbox{PVDD} = 15 \mbox{ V, SPK}\mbox{GAIN}[1:0] \mbox{Pins} = 01, \\ \mbox{R}_{\mbox{SPK}} = 2\Omega, \mbox{THD+N} = 0.1\%, \end{array}$    | 43.2    |     |       |

|                     |                              | $\begin{array}{l} PVDD=15\ V,\ SPK\_GAIN[1:0]\ Pins=01,\\ R_{SPK}=4\Omega,\ THD{+}N=0.1\%, \end{array}$                                                       | 25      |     |       |

| P                   | Maximum Instantaneous Output | $\begin{array}{l} PVDD=15\ V,\ SPK\_GAIN[1:0]\ Pins=01,\\ R_{SPK}=8\Omega,\ THD{+}N=0.1\% \end{array}$                                                        | 13.3    |     | W     |

| P <sub>O(SPK)</sub> | Power                        | $\begin{array}{l} \mbox{PVDD} = 19 \mbox{ V, SPK}\mbox{-}GAIN[1:0] \mbox{ Pins} = 01, \\ \mbox{R}_{\mbox{SPK}} = 2\Omega, \mbox{ THD+N} = 0.1\%, \end{array}$ | 68.3    |     | vv    |

|                     |                              | $\begin{array}{l} PVDD=19\;V,\;SPK\_GAIN[1:0]\;Pins=01,\\ R_{SPK}=4\Omega,\;THD{+}N=0.1\%, \end{array}$                                                       | 40      |     |       |

|                     |                              | $\begin{array}{l} PVDD=19 \; V, \; SPK\_GAIN[1:0] \; Pins=01, \\ R_{SPK}=8\Omega, \; THD+N=0.1\% \end{array}$                                                 | 21.3    |     |       |

|                     |                              | $\label{eq:pvdd} \begin{array}{l} PVDD = 24 \ V, \ SPK\_GAIN[1:0] \ Pins = 10, \\ R_{SPK} = 2\Omega, \ THD{+}N = 0.1\%, \end{array}$                          | 114.7   |     |       |

|                     |                              | $\label{eq:pvdd} \begin{array}{l} PVDD = 24 \ V, \ SPK\_GAIN[1:0] \ Pins = 10, \\ R_{SPK} = 4\Omega, \ THD+N = 0.1\%, \end{array}$                            | 63.5    |     |       |

|                     |                              | $\begin{array}{l} PVDD = 24 \; V, \; SPK\_GAIN[1:0] \; Pins = 10, \\ R_{SPK} = 8\Omega, \; THD{+}N = 0.1\% \end{array}$                                       | 34.1    |     |       |

STRUMENTS

EXAS

# Speaker Amplifier in Mono Parallel Bridge Tied Load (PBTL) Mode (continued)

Test conditions (unless otherwise noted):  $T_c = 25^{\circ}C$ , input signal is 1 kHz Sine

|                     | PARAMETER                         | TEST CONDITIONS                                                                                                                                                          | MIN TYP | MAX | UNIT |

|---------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

|                     |                                   | $\begin{array}{l} \mbox{PVDD} = 12 \mbox{ V, SPK}\_GAIN[1:0] \mbox{ Pins} = 00, \\ \mbox{R}_{SPK} = 2\Omega, \mbox{ THD+N} = 0.1\%, \end{array}$                         | 30      |     |      |

|                     |                                   | $\begin{array}{l} PVDD = 12 \; V, \; SPK\_GAIN[1:0] \; Pins = 00, \\ R_{SPK} = 4\Omega, \; THD{+}N = 0.1\%, \end{array}$                                                 | 15.9    |     |      |

|                     |                                   | PVDD = 12 V, SPK_GAIN[1:0] Pins = 00,<br>R_{SPK} = 8\Omega, THD+N = 0.1%                                                                                                 | 8.4     |     |      |

|                     |                                   | $\begin{array}{l} PVDD=\text{15 V, SPK\_GAIN[1:0] Pins=01,} \\ R_{SPK}=2\Omega, \ THD+N=0.1\%, \end{array}$                                                              | 28.5    |     |      |

|                     |                                   | $\begin{array}{l} \mbox{PVDD} = 15 \mbox{ V, SPK}\_GAIN[1:0] \mbox{ Pins} = 01, \\ \mbox{R}_{SPK} = 4\Omega, \mbox{ THD+N} = 0.1\%, \end{array}$                         | 25      |     |      |

| Р                   | Maximum Continuous Output         | $\begin{array}{l} \mbox{PVDD} = 15 \mbox{ V, SPK}\mbox{GAIN}[1:0] \mbox{ Pins} = 01, \\ \mbox{R}_{\mbox{SPK}} = 8\Omega, \mbox{THD}\mbox{+}\mbox{N} = 0.1\% \end{array}$ | 13.3    |     | W    |

| P <sub>O(SPK)</sub> | Power <sup>(1)</sup>              | $\begin{array}{l} PVDD = 19 \; V, \; SPK\_GAIN[1:0] \; Pins = 01, \\ R_{SPK} = 2\Omega, \; THD{+}N = 0.1\%, \end{array}$                                                 | 26.5    |     | vv   |

|                     |                                   | $\begin{array}{l} PVDD = 19 \; V, \; SPK\_GAIN[1:0] \; Pins = 01, \\ R_{SPK} = 4\Omega, \; THD{+}N = 0.1\%, \end{array}$                                                 | 40      |     |      |

|                     |                                   | $\begin{array}{l} PVDD=19 \; V, \; SPK\_GAIN[1:0] \; Pins=01, \\ R_{SPK}=8\Omega, \; THD+N=0.1\% \end{array}$                                                            | 21.3    |     |      |

|                     |                                   | $\begin{array}{l} PVDD=24\;V,\;SPK\_GAIN[1:0]\;Pins=10,\\ R_{SPK}=2\Omega,\;THD{+}N=0.1\%, \end{array}$                                                                  | 24      |     |      |

|                     |                                   | $\begin{array}{l} \mbox{PVDD} = 24 \mbox{ V, SPK}\_GAIN[1:0] \mbox{ Pins} = 10, \\ \mbox{R}_{SPK} = 4\Omega, \mbox{ THD+N} = 0.1\%, \end{array}$                         | 40      |     |      |

|                     |                                   | $\begin{array}{l} PVDD=24\;V,\;SPK\_GAIN[1:0]\;Pins=10,\\ R_{SPK}=8\Omega,\;THD{+}N=0.1\% \end{array}$                                                                   | 34.1    |     |      |

|                     |                                   | $\begin{array}{l} PVDD = 12 \; V, \; SPK\_GAIN[1:0] \; Pins = 00, \\ R_{SPK} = 8\Omega, \; A\text{-Weighted}, \; \text{-60dBFS Input} \end{array}$                       | 100.4   |     |      |

| SNR                 | Signal to Noise Ratio (Referenced | $\begin{array}{l} PVDD = 15 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8\Omega, \ A\text{-Weighted}, \ -60dBFS \ Input \end{array}$                                 | 99.5    |     | dD   |

| אמוכ                | to THD+N = 1%)                    | $\begin{array}{l} PVDD = 19 \ V, \ SPK\_GAIN[1:0] \ Pins = 01, \\ R_{SPK} = 8\Omega, \ A\text{-Weighted}, \ -60dBFS \ Input \end{array}$                                 | 100.1   |     | dB   |

|                     |                                   | $\begin{array}{l} PVDD = 24 \; V, \; SPK\_GAIN[1:0] \; Pins = 10, \\ R_{SPK} = 8\Omega, \; A\text{-Weighted}, \; \text{-60dBFS Input} \end{array}$                       | 99.5    |     |      |

(1) The continuous power output of any amplifier is determined by the thermal performance of the amplifier as well as limitations placed on it by the system around it, such as the PCB configuration and the ambient operating temperature. The performance characteristics listed in this section are achievable on the TAS5760M's EVM, which is representative of the popular "2 Layers / 1oz Copper" PCB configuration in a size that is representative of the amount of area often provided to the amplifier section of popular consumer audio electronics. As can be seen in the instantaneous power portion of this table, more power can be delivered from the TAS5760M if steps are taken to pull more heat out of the device. For instance, using a board with more layers or adding a small heatsink will result in an increase of continuous power, up to and including the instantaneous power level. This behavior can also been seen in the POUT vs. PVDD plots shown in the *Typical Characteristics (Mono PBTL Mode):* f<sub>SPK\_AMP</sub> = 384 kHz section of this data sheet.

# Speaker Amplifier in Mono Parallel Bridge Tied Load (PBTL) Mode (continued)

Test conditions (unless otherwise noted):  $T_C = 25^{\circ}C$ , input signal is 1 kHz Sine

|                        | PARAMETER                              | TEST CONDITIONS                                                                                                                                                | MIN TYP MAX | UNIT |

|------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

|                        |                                        | $\begin{array}{l} PVDD=12\ V,\ SPK\_GAIN[1:0]\ Pins=00,\\ R_{SPK}=2\Omega,\ Po=1\ W \end{array}$                                                               | 0.03%       |      |

|                        |                                        | $\begin{array}{l} PVDD = 12 \ V, \ SPK\_GAIN[1:0] \ Pins = 00, \\ R_{SPK} = 4\Omega, \ Po = 1 \ W \end{array}$                                                 | 0.02%       |      |

|                        |                                        | $\begin{array}{l} PVDD=12\ V,\ SPK\_GAIN[1:0]\ Pins=00,\\ R_{SPK}=8\Omega,\ Po=1\ W \end{array}$                                                               | 0.02%       |      |

|                        |                                        | $\begin{array}{l} PVDD=15\;V,\;SPK\_GAIN[1:0]\;Pins=01,\\ R_{SPK}=2\Omega,\;Po=1\;W \end{array}$                                                               | 0.03%       |      |

|                        | Total Harmonic Distortion and<br>Noise | $\begin{array}{l} PVDD=15\;V,SPK\_GAIN[1:0]\;Pins=01,\\ R_{SPK}=4\Omega,Po=1\;W \end{array}$                                                                   | 0.02%       |      |

|                        |                                        | $\begin{array}{l} PVDD=15\ V,\ SPK\_GAIN[1:0]\ Pins=01,\\ R_{SPK}=8\Omega,\ Po=1\ W \end{array}$                                                               | 0.02%       |      |

| THD+N <sub>(SPK)</sub> |                                        | $\begin{array}{l} PVDD=19\;V,\;SPK\_GAIN[1:0]\;Pins=01,\\ R_{SPK}=2\Omega,\;Po=1\;W \end{array}$                                                               | 0.03%       |      |

|                        |                                        | $\begin{array}{l} PVDD = 19 \; V, \; SPK\_GAIN[1:0] \; Pins = 01, \\ R_{SPK} = 4\Omega, \; Po = 1 \; W \end{array}$                                            | 0.02%       |      |

|                        |                                        | $\begin{array}{l} PVDD=19\;V,\;SPK\_GAIN[1:0]\;Pins=01,\\ R_{SPK}=8\Omega,\;Po=1\;W \end{array}$                                                               | 0.03%       |      |

|                        |                                        | $\begin{array}{l} PVDD = 24 \ V, \ SPK\_GAIN[1:0] \ Pins = 10, \\ R_{SPK} = 2\Omega, \ Po = 1 \ W \end{array}$                                                 | 0.03%       |      |

|                        |                                        | $\begin{array}{l} \mbox{PVDD} = 24 \mbox{ V, SPK}\mbox{GAIN}[1:0] \mbox{ Pins} = 10, \\ \mbox{R}_{\mbox{SPK}} = 4\Omega, \mbox{ Po} = 1 \mbox{ W} \end{array}$ | 0.02%       |      |

|                        |                                        | $\begin{array}{l} PVDD=24\ V,\ SPK\_GAIN[1:0]\ Pins=10,\\ R_{SPK}=8\Omega,\ Po=1\ W \end{array}$                                                               | 0.03%       |      |

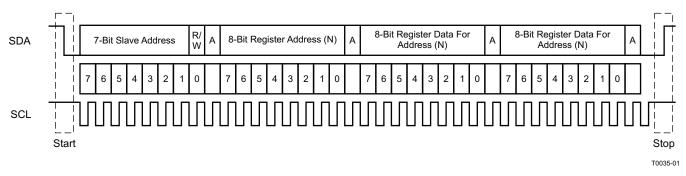

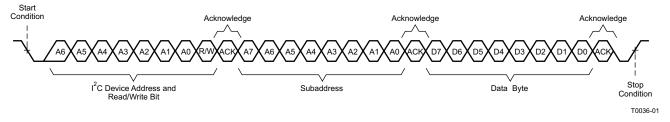

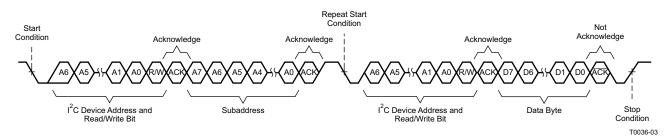

# 6.11 I<sup>2</sup>C Control Port

Test conditions (unless otherwise noted):  $T_C = 25^{\circ}C$

|                                | PARAMETER                                                 | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|--------------------------------|-----------------------------------------------------------|-----------------|-----|---------|------|

| C <sub>L(I<sup>2</sup>C)</sub> | Allowable Load Capacitance for Each I <sup>2</sup> C Line |                 |     | 400     | pF   |

| f <sub>SCL</sub>               | Support SCL frequency                                     | No Wait States  |     | 400     | kHz  |

| t <sub>buf</sub>               | Bus Free time between STOP and<br>START conditions        |                 | 1.3 |         | μS   |

| t <sub>f(I2C)</sub>            | Rise Time, SCL and SDA                                    |                 |     | 300     | ns   |

| t <sub>h1(I²C)</sub>           | Hold Time, SCL to SDA                                     |                 | 0   |         | ns   |

| t <sub>h2(I2C)</sub>           | Hold Time, START condition to SCL                         |                 | 0.6 |         | μs   |

| t <sub>l²C(start)</sub>        | I <sup>2</sup> C Startup Time                             |                 |     | 12      | mS   |

| t <sub>r(I2C)</sub>            | Rise Time, SCL and SDA                                    |                 |     | 300     | ns   |

| t <sub>su1(I2C)</sub>          | Setup Time, SDA to SCL                                    |                 | 100 |         | ns   |

| t <sub>su2(I2C)</sub>          | Setup Time, SCL to START condition                        |                 | 0.6 |         | μS   |

| t <sub>su3(I2C)</sub>          | Setup Time, SCL to STOP condition                         |                 | 0.6 |         | μS   |

| T <sub>w(H)</sub>              | Required Pulse Duration, SCL HIGH                         |                 | 0.6 |         | μS   |

| T <sub>w(L)</sub>              | Required Pulse Duration, SCL LOW                          |                 | 1.3 |         | μS   |

NSTRUMENTS

Texas

# 6.12 Typical Idle, Mute, Shutdown, Operational Power Consumption

Test conditions (unless otherwise noted):  $T_C = 25^{\circ}C$ , input signal is 1 kHz Sine

| V <sub>PVDD</sub><br>[V] | R <sub>SPK</sub><br>[Ω] | SPEAKER AMI                       | PLIFIER STATE   | I <sub>PVDD+AVDD</sub><br>[mA] | I <sub>DVDD</sub><br>[mA] | P <sub>DISS</sub><br>[W] |

|--------------------------|-------------------------|-----------------------------------|-----------------|--------------------------------|---------------------------|--------------------------|

|                          | 4                       |                                   | Idle            | 23.48                          | 3.73                      | 0.15                     |

|                          | 8                       |                                   | luie            | 23.44                          | 3.72                      | 0.15                     |

|                          | 4                       |                                   | Mute            | 23.53                          | 3.72                      | 0.15                     |

| -                        | 8                       | f <sub>SPK_AMP</sub> =            | Mute            | 23.46                          | 3.72                      | 0.15                     |

|                          | 4                       | 384kHz                            | Clean           | 13.26                          | 0.48                      | 0.08                     |

|                          | 8                       |                                   | Sleep           | 13.27                          | 0.53                      | 0.08                     |

|                          | 4                       |                                   | Shutdown        | 0.046                          | 0.04                      | 0                        |