### **Automotive USB Power Delivery Port Protector**

### **General Description**

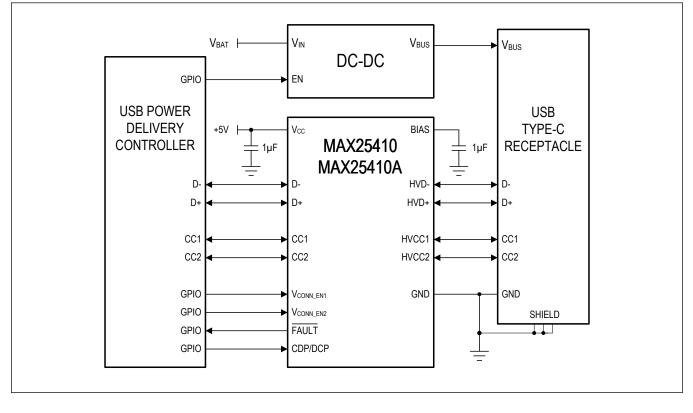

The MAX25410 is an automotive USB Power Delivery (USB-PD)-based Type-C protection solution for automotive radio, navigation, connectivity, and USB hub/multimedia module applications.

The device provides a one-chip automotive USB-PD protection solution for the CC1, CC2, D+, and D- signals on a USB Type-C connector. MAX25410 and MAX25410A also provide a  $V_{CONN}$  switch with advanced fault management that does not require a dedicated supply.

For ports that do not require  $V_{CONN}$  (i.e. do not support USB 3.0 or are rated at 3A or less), MAX25410B offers the designer a reduced-cost solution with the same protection level as MAX25410.

The device protection features include  $\pm 15$ kV IEC 61000-4-2, ISO 10605 ESD, and short-to-V<sub>BUS</sub> (24V) on the protected HVCC1, HVCC2, HVD+, and HVD- pins. The device also features integrated BC1.2 charge-detection CDP, DCP, or pass-through (SDP) modes, Apple® 2.4A, Samsung® 2A, and China YD/T 1591-2009 charge-emulation support.

The MAX25410 is available in a small 4mm x 4mm 16-pin TQFN package and requires very few external components.

### **Applications**

- Automotive Radio and Navigation

- Automotive USB Hubs

- Automotive Multimedia Box Applications

#### **Benefits and Features**

- USB Type-C CC1/CC2 Protection Switches

- Integrated 550mΩ V<sub>CONN</sub> FETs with 250mA Overcurrent Protection

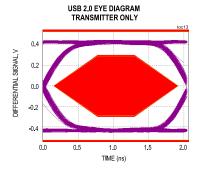

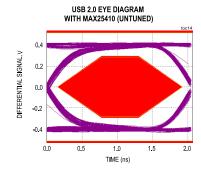

- USB 2.0 D+/D- Protection Switches with 1GHz Bandwidth

- 24V CC and USB 2.0 Protection against Short-to-V<sub>BUS</sub>

- Automatic Fault Detection and Recovery with Industry-Compliant Reset Timings

- Integrated Apple and Samsung Dedicated Charge-Termination Resistors

- · Supports USB BC1.2 CDP and DCP Modes

- Supports China YD/T 1591-2009

- Compatible with USB On-the-Go Specification and Apple CarPlay

- High ESD Protection (HVD+/HVD-, HVCC1/HVCC2)

- ±2kV Human Body Model

- ±15kV ISO 10605 Air Gap

- ±8kV ISO 10605 Contact

- ±15kV IEC 61000-4-2 Air Gap

- ±8kV IEC 61000-4-2 Contact

- 4mm x 4mm 16-Pin TQFN-EP Package

- -40°C to +105°C Operating Temperature Range

- AEC-Q100 and AEC-Q006 Qualified

Ordering Information appears at end of data sheet.

Apple is a registered trademark of Apple Inc. Samsung is a registered trademark of Samsung Electronics Co., Ltd.

## Automotive USB Power Delivery Port Protector

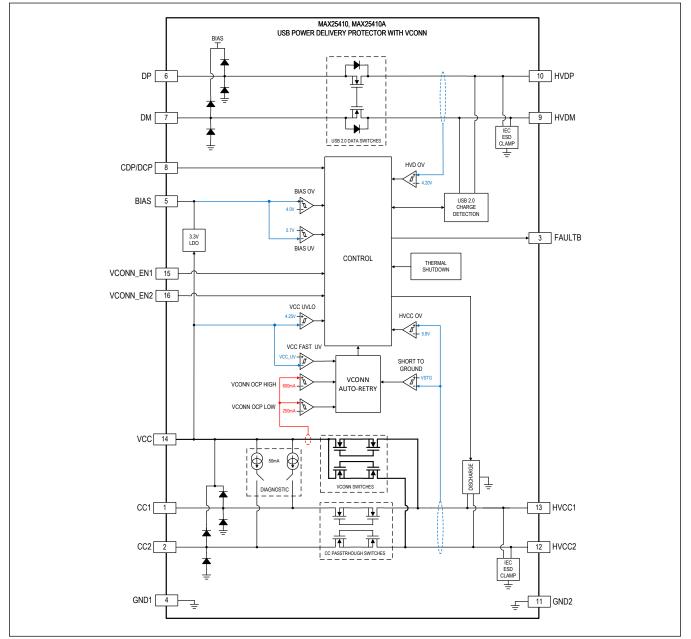

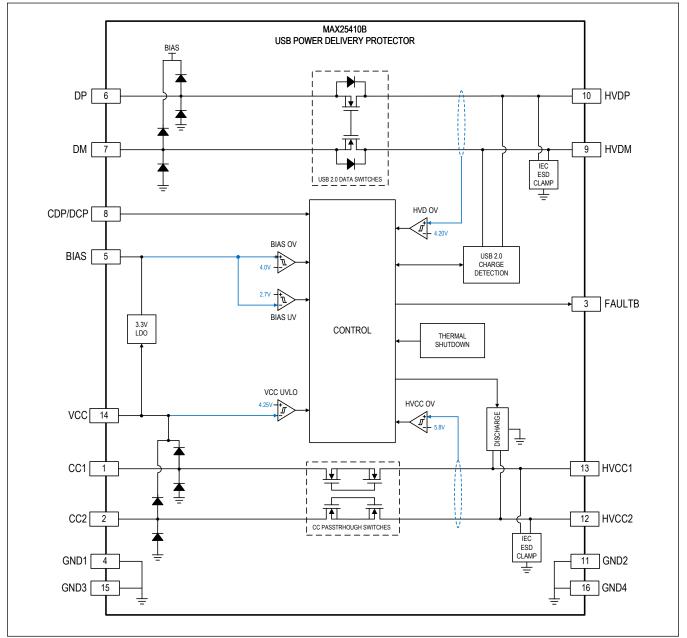

## Simplified Block Diagram

## Automotive USB Power Delivery Port Protector

### **Absolute Maximum Ratings**

| HVCC1, HVCC2 to GND (Note 1)                         | 0.3V to +24V                     |

|------------------------------------------------------|----------------------------------|

| HVD+, HVD- to GND (Note 1)                           | 0.3V to +24V                     |

| V <sub>CC</sub> to GND (Note 1)                      | 0.3V to +6.0V                    |

| CC1, CC2 to GND (Note 1)                             | 0.3V to +6.0V                    |

| D+, D- to GND (Note 1)                               | 0.3V to V <sub>BIAS</sub> + 0.3V |

| BIAS to GND (Note 1)                                 | 0.3V to +6.0V                    |

| V <sub>CONN EN1</sub> , V <sub>CONN EN2</sub> to GND | 0.3V to +6.0V                    |

| CDP/DCP, FAULT to GND                                |                                  |

Note 1: Self-protected from transient voltages exceeding these limits in circuit under normal operation.

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations see <u>http://www.maxim-ic.com/thermal-tutorial</u>

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### TQFN

| Package Code                            | T1644+4C       |

|-----------------------------------------|----------------|

| Outline Number                          | <u>21-0139</u> |

| Land Pattern Number                     | <u>90-0070</u> |

| Thermal Resistance, Single-Layer Board: |                |

| Junction to Ambient ( $\theta_{JA}$ )   | 59.3 °C/W      |

| Junction to Case ( $\theta_{JC}$ )      | 6°C/W          |

| Thermal Resistance, Four-Layer Board:   |                |

| Junction to Ambient ( $\theta_{JA}$ )   | 40°C/W         |

| Junction to Case ( $\theta_{JC}$ )      | 6°C/W          |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### **Electrical Characteristics**

(T<sub>A</sub> = -40 °C to +105 °C. Typical values are at V<sub>CC</sub> = 5.0V, T<sub>A</sub> = +25 °C, unless otherwise noted (Note 3))

| PARAMETER                                          | SYMBOL                  | CONDITIONS MIN TYP MAX                             |                    |      |     | UNITS |

|----------------------------------------------------|-------------------------|----------------------------------------------------|--------------------|------|-----|-------|

| V <sub>CC</sub> Supply Voltage<br>Range            | V <sub>CC</sub>         |                                                    | 4.7 5.0 5.5        |      |     |       |

| V <sub>CC</sub> Operating Current                  | Ivcc                    | V <sub>CC</sub> = 5.0V; V <sub>CONN</sub> disabled |                    |      | 1.5 | mA    |

| V <sub>CC</sub> Undervoltage<br>Lockout Rising     | V <sub>CC_UVLO</sub>    | V <sub>CC</sub> Rising, chip enabled               | 4.0                | 4.3  | 4.5 | V     |

| V <sub>CC</sub> Undervoltage<br>Lockout Hysteresis | V <sub>CC_UVLO_HY</sub> |                                                    |                    | 0.1  |     | V     |

| BIAS Regulator                                     |                         |                                                    |                    |      |     |       |

| Bias Regulator Voltage                             | V <sub>BIAS</sub>       | V <sub>CC</sub> = 4.7V to 5.5V                     |                    | 3.15 |     | V     |

| BIAS Undervoltage                                  | VUV_BIAS_F              | V <sub>BIAS</sub> undervoltage falling threshold   |                    | 2.70 |     | V     |

| BIAS Overvoltage                                   | V <sub>OV_BIAS</sub>    | V <sub>BIAS</sub> overvoltage rising threshold     | hold 3.85 4.0 4.25 |      |     | V     |

## **Electrical Characteristics (continued)**

$(T_A = -40 \degree C \text{ to } +105 \degree C.$  Typical values are at V<sub>CC</sub> = 5.0V, T<sub>A</sub> = +25 °C, unless otherwise noted (Note 3))

| BIAS Undervoltage                                 |                                |                                                                                                                                          |         |      |      | UNITS |

|---------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|-------|

| Blanking Time                                     | <sup>t</sup> BLANK_BIAS_<br>UV | From V <sub>BIAS</sub> below UV to FAULT asserted                                                                                        | 1.8     |      | ms   |       |

| HVD+/HVD- Analog Swite                            | ches                           |                                                                                                                                          |         |      |      |       |

| Analog Signal Range                               |                                | 0 3.6                                                                                                                                    |         | V    |      |       |

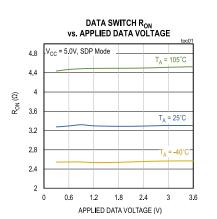

| Data Switch ON<br>Resistance                      | R <sub>ON_D</sub>              | $V_{D+}/V_{D-} = 0V$ to 3.6V, I <sub>L</sub> = 10mA                                                                                      |         | 4    |      | Ω     |

| Data Protection Trip<br>Threshold                 | V <sub>OV_D</sub>              | $V_{HVD+}/V_{HVD-}$ rising                                                                                                               | 4.05    | 4.20 | 4.30 | V     |

| Data Protection OV<br>Threshold Hysteresis        | V <sub>OV_D_HYST</sub>         |                                                                                                                                          |         | 15   |      | mV    |

| Data Protection<br>Response Time                  | t <sub>FP_D</sub>              | From OV condition to switch opened                                                                                                       |         | 2    |      | μs    |

| Data Overvoltage<br>Blanking Timeout Period       | t <sub>B_OV_D</sub>            | From switch opened for OV to FAULT asserted                                                                                              |         | 1    |      | μs    |

| Data Switch Differential<br>Bandwidth             | BW <sub>D_DIFF</sub>           | USB TEST_PACKET @ 240MHz<br>fundamental; -3dB BW                                                                                         |         | 1    |      | GHz   |

| ON-Resistance Match<br>Between Channels           | $\Delta R_{ON}sa$              | $I_L = 10mA, V_{D+}/V_{D-} = 1.5V \text{ to } 3.0V$                                                                                      | 0.2     |      |      | Ω     |

| ON-Resistance Flatness                            | R <sub>FLATON_A</sub>          | $I_L = 10 \text{mA}, V_{D+}/V_{D-} = 0.0 \text{V} \text{ and } 0.4 \text{V}$ 0.2                                                         |         | 0.2  | Ω    |       |

| D+/D- OFF Leakage                                 | ID_OFF                         | $V_{HVD+}/V_{HVD-}$ = 18V; $V_{D+}/V_{D-}$ = 0V;<br>D+/D- leakage to GND                                                                 |         |      | 1    | μA    |

| Data Switch ON<br>Leakage                         | ID_ON                          | $V_{D+}/V_{D-}$ = 3.6V; leakage to GND                                                                                                   | 7       |      | 7    | μA    |

| HVD+/HVD- OFF<br>Leakage                          | I <sub>HVD_OFF</sub>           | V <sub>HVD+</sub> /V <sub>HVD-</sub> = 18V; HVD+/HVD-<br>leakage to GND                                                                  |         | 60   |      | μA    |

| USB2.0 Host Charge Det                            | ection                         |                                                                                                                                          |         |      |      |       |

| Input Logic High                                  | VIH                            |                                                                                                                                          | 2.0     |      |      | V     |

| Input Logic Low                                   | V <sub>IL</sub>                |                                                                                                                                          |         |      | 0.8  | V     |

| Data Sink Current                                 | IDAT_SINK                      | V <sub>DAT_SINK</sub> = 0.25V to 0.4V                                                                                                    | 50      | 100  | 150  | μA    |

| Data Detection Voltage<br>High                    | V <sub>DAT_REFH</sub>          |                                                                                                                                          | 0.40    |      |      | V     |

| Data Detection Logic<br>Low                       | V <sub>DAT_REFL</sub>          |                                                                                                                                          | 0.25    |      | V    |       |

| Data Source Voltage                               | V <sub>DAT_SRC</sub>           | I <sub>SRC</sub> = 200μA                                                                                                                 | 0.5 0.7 |      | V    |       |

| V <sub>CONN</sub> Analog Switch (N                | IAX25410, MAX                  | 25410A)                                                                                                                                  |         |      |      |       |

| V <sub>CONN</sub> Switch ON<br>Resistance         | RON_VCONN                      | 100mA/200mA Load Current, V <sub>CC</sub> = 5.0V                                                                                         |         | 550  | 1150 | mΩ    |

| V <sub>CONN</sub> Overcurrent<br>Threshold (Low)  | V <sub>CONN_OCP_</sub><br>LOW  | Measured on HVCC1 and HVCC2, V <sub>CC</sub> 200         250         300           from 4.7V to 5.5V         200         250         300 |         | mA   |      |       |

| V <sub>CONN</sub> Overcurrent<br>Threshold (High) | V <sub>CONN_OCP_</sub><br>HIGH | Measured on HVCC1 and HVCC2, $V_{CC}$ = 5.0V                                                                                             | 480     | 600  | 710  | mA    |

## Automotive USB Power Delivery Port Protector

## **Electrical Characteristics (continued)**

$(T_A = -40 \degree C \text{ to } +105 \degree C.$  Typical values are at V<sub>CC</sub> = 5.0V, T<sub>A</sub> = +25 °C, unless otherwise noted (Note 3))

| PARAMETER                                                           | SYMBOL                           | CONDITIONS                                                                       | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>CONN</sub> Overcurrent<br>Protection Response<br>Time (Low)  | t <sub>VCONN_OCP_</sub><br>LOW   | Time from OC condition to V <sub>CONN</sub> FET open                             |      | 0.4  |      |       |

| V <sub>CONN</sub> Overcurrent<br>Protection Response<br>Time (High) | t <sub>VCONN_OCP_</sub><br>HIGH  | Time from OC condition to $V_{\mbox{CONN}}$ FET open                             |      | 5    |      | μs    |

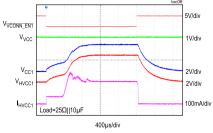

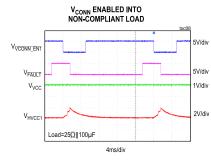

| V <sub>CONN</sub> ON Time                                           | t <sub>VCONN_ON</sub>            | Enable $V_{CONN}$ to HVCC at 95% of $V_{CC}$ with 25 $\Omega /\!/ 10 \mu F$ load |      | 700  |      | μs    |

| V <sub>CONN</sub> Discharge<br>Resistance                           | R <sub>VCONN_DIS</sub>           |                                                                                  |      | 3    |      | kΩ    |

| V <sub>CONN</sub> Discharge Time                                    | <sup>t</sup> VCONN_DIS           | During power-up and certain faults. See <u>Table 1</u> .                         |      | 30   |      | ms    |

| V <sub>CONN</sub> Diagnostic<br>Current                             | I <sub>DIAG</sub>                | $V_{CONN}$ enabled and before $V_{CONN}$ main FET soft-start                     |      | 60   |      | mA    |

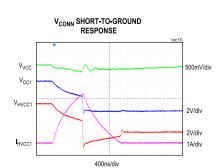

| V <sub>CONN</sub> Short-to-GND<br>Comparator Rising<br>Threshold    | V <sub>STG_R</sub>               | Active during V <sub>CONN</sub> startup only.<br>Measured at HVCC pin            |      | 0.35 |      | v     |

| V <sub>CC</sub> Fast UV Threshold                                   | V <sub>CC_FAST_UV</sub>          | $V_{CONN}$ enabled, measured at $V_{CC},V_{CC}$ falling                          |      | 4.65 |      | V     |

| V <sub>CC</sub> Fast UV Hysteresis                                  | V <sub>CC_FAST_UV</sub><br>_HYST | V <sub>CONN</sub> enabled                                                        | 60   |      | mV   |       |

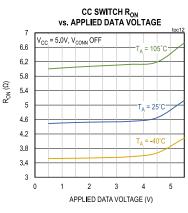

| CC Pass-Through Analo                                               | g Switches                       |                                                                                  |      |      |      |       |

| Analog Signal Range                                                 |                                  |                                                                                  | 0    |      | 5.5  | V     |

| CC Switch ON<br>Resistance                                          | R <sub>CC_ON</sub>               | Resistance from CC1 to HVCC1 or CC2 to HVCC2, $V_{CC1}/V_{CC2} = 0V$ to 5.5V     |      | 4    |      | Ω     |

| HVCC OV Protection<br>Trip Threshold                                | V <sub>OV_HVCC</sub>             |                                                                                  | 5.65 | 5.85 | 6.05 | V     |

| HVCC Protection OV<br>Threshold Hysteresis                          | V <sub>OV_HVCC_H</sub><br>YST    |                                                                                  |      | 75   |      | mV    |

|                                                                     | t <sub>FP_HVCC</sub>             | From OV condition to switch opened                                               |      | 2    |      |       |

| HVCC Overvoltage<br>Blanking Timeout Period                         | tB_OV_HVCC                       | From switch opened due to OV to FAULT asserted                                   |      | 1    |      | μs    |

| CC Switch Single-End<br>Capacitance                                 | C <sub>ON_CC</sub>               |                                                                                  |      | 100  |      | pF    |

| CC Switch ON Leakage                                                | ICC_ON_LKG                       | CC switch ON, $V_{CC1}/V_{CC2}$ = 5.5V, CC1/<br>CC2 pin leakage                  | 5    |      | μA   |       |

| FAULT Pin                                                           |                                  |                                                                                  |      |      |      |       |

| FAULT Output Low<br>Voltage                                         | V <sub>OL</sub>                  | 1mA forced into FAULT pin                                                        |      |      | 0.5  | V     |

| FAULT Leakage Current                                               | IFAULTB_LKG                      | FAULT Pin = 3.3V or 5.0V                                                         |      |      | 1    | μA    |

| FAULT Retry Timer                                                   | t <sub>RCV</sub>                 | See Table 1.                                                                     |      | 16   |      | ms    |

| V <sub>CONN_EN1</sub> , V <sub>CONN_EN2</sub>                       | Pins (MAX2541                    | 0, MAX25410A)                                                                    |      |      |      |       |

| Input Logic High                                                    | V <sub>VCONN_EN_I</sub><br>H     |                                                                                  | 1.6  |      |      | V     |

| •                                                                   | •                                |                                                                                  |      |      |      |       |

## **Electrical Characteristics (continued)**

$(T_A = -40 \degree C \text{ to } +105 \degree C.$  Typical values are at  $V_{CC} = 5.0V$ ,  $T_A = +25 \degree C$ , unless otherwise noted (Note 3))

| PARAMETER                       | SYMBOL                        | CONDITIONS                          | MIN | TYP | MAX | UNITS |

|---------------------------------|-------------------------------|-------------------------------------|-----|-----|-----|-------|

| Input Logic Low                 | V <sub>VCONN_EN_I</sub>       |                                     |     |     | 0.5 | v     |

| Input Leakage Current           | I <sub>VCONN_IN_LK</sub><br>G |                                     |     |     | 20  | μA    |

| CDP/DCP Pin                     |                               |                                     |     |     |     |       |

| Input Logic High                | V <sub>CDPDCP_EN</sub> _IH    |                                     | 1.6 |     |     | V     |

| Input Logic Low                 | V <sub>CDPDCP_EN</sub> _IL    |                                     |     |     | 0.5 | V     |

| Input Leakage Current           | ICDPDCP_IN_L<br>KG            |                                     |     |     | 5   | μA    |

| Thermal Shutdown                |                               |                                     |     |     |     |       |

| Thermal Shutdown<br>Temperature | T <sub>SHDN</sub>             | T <sub>J</sub> Rising               |     | 165 |     | °C    |

| Thermal Shutdown<br>Hysteresis  | T <sub>SHDN_HYS</sub>         | 10                                  |     |     | °C  |       |

| ESD Protection - HVCC           | 1/HVCC2/HVD+/H                | IVD- Pins                           |     |     |     |       |

| ESD Protection Level            | V <sub>ESD</sub>              | Human Body Model                    |     | ±2  |     | kV    |

|                                 |                               | ISO 10605 Air Gap (330pF, 2kΩ)      |     | ±15 |     | КV    |

| ESD Protection Level            |                               | ISO 10605 Contact (330pF, 2kΩ)      |     | ±8  |     |       |

| (Note 4)                        | V <sub>ESD</sub>              | IEC 61000-4-2 Air Gap (150pF, 330Ω) | ±15 |     | kV  |       |

|                                 |                               | IEC 61000-4-2 Contact (150pF, 330Ω) |     | ±8  |     | 1     |

Note 3: Specification with minimum and maximum limits are 100% production tested at  $T_A = 25^{\circ}C$  and are guaranteed over the operating temperature range by design and characterization. Actual typical values may vary and are not guaranteed.

Note 4: Tested on EV kit.

## Automotive USB Power Delivery Port Protector

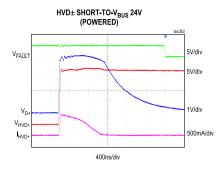

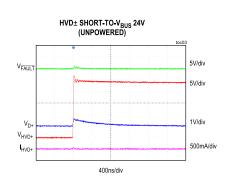

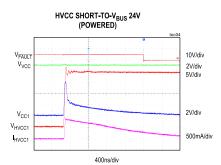

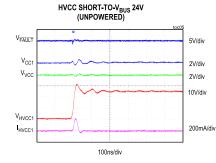

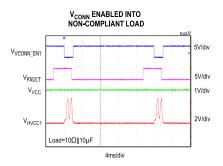

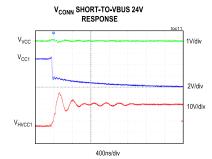

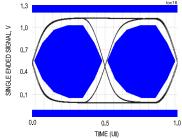

### **Typical Operating Characteristics**

(VCC = 5.0V;  $T_A = 25^{\circ}C$  unless otherwise noted)

## Automotive USB Power Delivery Port Protector

## **Typical Operating Characteristics (continued)**

(VCC = 5.0V;  $T_A = 25^{\circ}C$  unless otherwise noted)

BMC EYE DIAGRAM TRANSMITTER ONLY

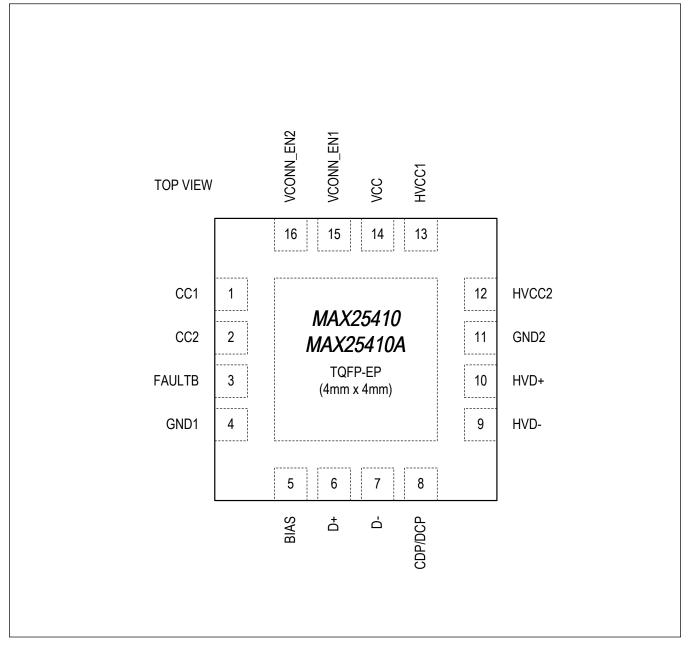

## **Pin Configurations**

#### MAX25410, MAX25410A

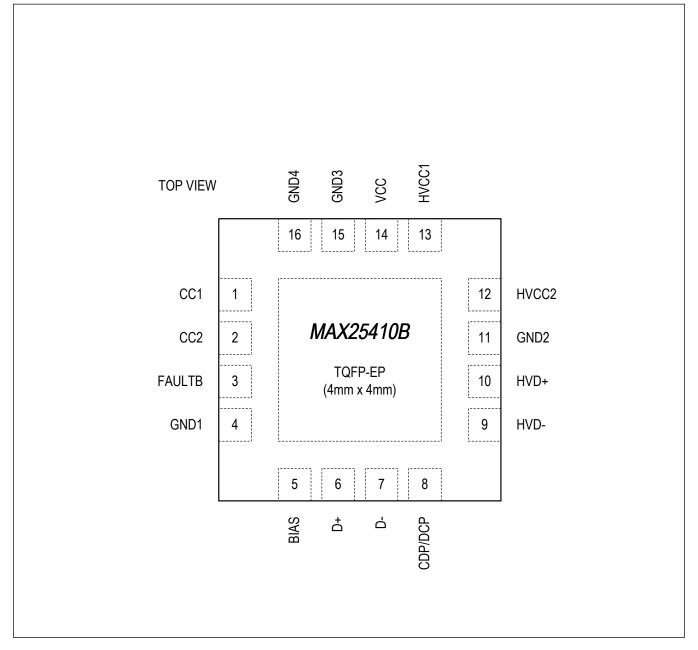

## Automotive USB Power Delivery Port Protector

#### MAX25410B

## **Pin Description**

| PIN                    |           |                       |                                                                                                                                                                  |  |

|------------------------|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX25410,<br>MAX25410A | MAX25410B | NAME                  | FUNCTION                                                                                                                                                         |  |

| 1                      | 1         | CC1                   | Upstream CC1 Connection to USB-PD Host/Controller                                                                                                                |  |

| 2                      | 2         | CC2                   | Upstream CC2 Connection to USB-PD Host/Controller                                                                                                                |  |

| 3                      | 3         | FAULT                 | Open-Drain Fault Output. Activation indicates that fault condition is present.<br>Connect to host microcontroller, Type-C/PD port controller, or hub controller. |  |

| 4                      | 4         | GND1                  | GND pin. Connect directly to GND; tie to GND pour underneath IC.                                                                                                 |  |

| 5                      | 5         | BIAS                  | BIAS Regulator Output. Connect 1µF ceramic decoupling capacitor from BIAS to GND.                                                                                |  |

| 6                      | 6         | D+                    | Upstream D+ or SBU Connection to Low-Voltage USB Transceiver                                                                                                     |  |

| 7                      | 7         | D-                    | Upstream D- or SBU Connection to Low-Voltage USB Transceiver                                                                                                     |  |

| 8                      | 8         | CDP/DCP               | Data Switch Mode Select. This pin selects between the two default modes of data switch operation. The default modes are defined in the <u>Table 5</u> .          |  |

| 9                      | 9         | HVD-                  | Protected HVD- Connection to Downstream USB Type-C Connector or Captive Cable                                                                                    |  |

| 10                     | 10        | HVD+                  | Protected HVD+ Connection to Downstream USB Type-C Connector or Captive Cable                                                                                    |  |

| 11                     | 11        | GND2                  | GND Pin. Connect directly to GND; tie to GND pour underneath IC. Low GND connection impedance is critical for USB system performance.                            |  |

| 12                     | 12        | HVCC2                 | Protected CC2 Connection to Downstream USB Type-C Connector or Captive Cable                                                                                     |  |

| 13                     | 13        | HVCC1                 | Protected CC1 Connection to Downstream USB Type-C Connector or Captive Cable                                                                                     |  |

| 14                     | 14        | V <sub>CC</sub>       | Main IC Supply and V <sub>CONN</sub> Switch Input. Connect a local 1µF ceramic capacitor from V <sub>CC</sub> to GND.                                            |  |

| 15                     | _         | V <sub>CONN_EN1</sub> | V <sub>CC</sub> -to-HVCC1 V <sub>CONN</sub> Switch Enable Pin. Active high or low depending on variant. Refer to <u>Ordering Information</u> .                   |  |

| _                      | 15        | GND3                  | GND pin. Connect directly to GND; tie to GND pour underneath IC.                                                                                                 |  |

| 16                     | _         | V <sub>CONN_EN2</sub> | V <sub>CC</sub> -to-HVCC2 V <sub>CONN</sub> switch Enable Pin. Active high or low depending on variant. Refer to <u>Ordering Information</u> .                   |  |

| _                      | 16        | GND4                  | GND pin. Connect directly to GND; tie to GND pour underneath IC.                                                                                                 |  |

| 17                     | 17        | EP                    | Exposed Pad. Connect directly to GND                                                                                                                             |  |

### **Functional Diagrams**

#### MAX25410, MAX25410A

## **Functional Diagrams (continued)**

### MAX25410B

### **Detailed Description**

The MAX25410 combines USB Type-C CC1/CC2 and D+/D-protection switches with an industry-leading integrated ESD and overvoltage protection. The IC is capable of delivering V<sub>CONN</sub> power to the HVCC1 or HVCC2 outputs with minimal voltage drop, supports charge emulation, and supports USB LS/FS/HS communication on the D+/D- switches.

The device features automotive-grade ±15kV IEC 61000-4-2 ESD protection on all protected outputs, as well as 24V overvoltage protection on the CC and data switches. The integrated Type-C discharge switch features high-ESD protection and integrated overvoltage-detection logic.

The MAX25410 is designed for installation in USB Type-C head units/hubs/dedicated charging ports where automotivegrade ESD and overvoltage protection is required for sensitive upstream hosts.

#### Protection and Control

#### CC1/CC2 Pins

The CC1 and CC2 pins are the protected side of the CC switches and connect directly to the USB-PD controller. A 390pF capacitance to ground is recommended on both CC1 and CC2 pins, which can be the USB-PD Controller's cReceiver capacitance.

#### HVCC1/HVCC2 Pins

The HVCC1 and HVCC2 pins connect directly to the downstream USB Type-C port connector or captive cable. No external circuitry is needed on either HVCC pin. HVCC1 and HVCC2 are tolerant to automotive high ESD, up to 24V DC, and up to 40V voltage transients. HVCC1 and HVCC2 are automatically discharged for 30ms at power-up or after specific fault conditions (see <u>Table 1</u>), and for 10ms every time  $V_{CONN}$  is disabled.

#### D+/D- Pins

The D+ and D- pins are the protected side of the USB data switches and connect directly to the low-voltage upstream USB PHY or captive cable. No external circuitry is used on either data pin.

#### HVD+/HVD- Pins

The HVD+ and HVD- pins should be routed to the downstream Type-C connector or captive cable. No external circuitry is required on either pin. The HVD+ pin and HVD- pin are tolerant to automotive high ESD, up to 24V DC, and up to 40V voltage transients.

### V<sub>CONN\_EN1</sub>/V<sub>CONN\_EN2</sub> Pins (MAX25410, MAX25410A)

The V<sub>CONN</sub> switch allows pins to enable only one of the two V<sub>CONN</sub> switches: V<sub>CC</sub>-to-HVCC1 pins or V<sub>CC</sub>-to-HVCC2 pins, active-low, depending on the variant. See <u>VCONN Switch/CC Pass Through Switch Enable Table</u> and the <u>Ordering Information</u> section.

#### FAULT Pin

The FAULT pin is an open-drain fault-indication pin that asserts upon fault detection. For faults unrelated to V<sub>CONN</sub>, such as an overvoltage on HVCC or HVD pins, the FAULT pin will remain asserted continuously until the fault is no longer present.

During a  $V_{CONN}$  short-to-ground fault, the FAULT pin asserts and remains asserted until the fault is no longer present or the PD controller disables  $V_{CONN}$ .

For a non-compliant V<sub>CONN</sub> load fault, the IC will attempt to retry and provide V<sub>CONN</sub> automatically until the fault is no longer present or the PD controller disables V<sub>CONN</sub>.

Refer to <u>Table 1</u> and the  $V_{CONN}$  Auto-Retry section for additional information.

#### V<sub>CONN</sub> Switches (MAX25410, MAX25410A)

The advantage of MAX25410 is the ability to switch power from a low-power system supply to a wide range of E-marked cables (that is, using the same supply that powers the USB-PD Controller). This essentially reduces the current budget needed for supplying  $V_{CONN}$  and therefore reduces solution cost and size.

Certain E-marked cables, however, draw currents that exceed the Type-C specification of 1W maximum shortly after  $V_{CONN}$  is sourced, which causes unwanted inrush currents and droops on the system supply, ultimately causing a module reset.

To overcome this limitation while providing the 1W V<sub>CONN</sub> required by Type-C, MAX25410 implements a Fast UV comparator on V<sub>CC</sub> and dual-threshold overcurrent protection with specific debounce timers. The first overcurrent threshold (OCP Low) is set at 250 mA with a debounce of 400 $\mu$ s, which permits exceeding the 1W limit momentarily to start up the E-marked cable circuitry. The second OCP threshold (OCP High) is set to 600 mA and has a debounce of 5  $\mu$ s, which protects the system supply from non-compliant V<sub>CONN</sub> loads and/or short circuits.

#### V<sub>CONN</sub> Auto-Retry (MAX25410, MAX25410A)

Due to the V<sub>CC</sub> supply being a shared supply, asynchronous system loads can occur while sourcing V<sub>CONN</sub>. For this reason, a V<sub>CONN</sub> Auto-Retry feature is implemented to minimize the software interaction of sourcing V<sub>CONN</sub> with a shared supply.

If a  $V_{CONN}$  load (E-marked cable or VPD) tries to draw an excessive amount of current for more than the debounce time, the  $V_{CONN}$  switch will automatically open to avoid drooping the upstream power supply, then automatically retry. The USB-PD Controller can take action when the FAULT pin asserts. If FAULT de-asserts upon disabling  $V_{CONN}$ , the PD Controller can proceed without powering the non-compliant E-marked cable until a new cable is detected.

The  $V_{CONN}$  auto-retry feature is active for the following  $V_{CONN}$ -related faults:

- V<sub>CONN</sub> OCP LOW

- V<sub>CONN</sub> OCP HIGH

- V<sub>CC</sub> FAST UV

- V<sub>CONN</sub> SHORT TO GROUND

For the other faults, such as HVD and HVCC OV, VCC UVLO, BIAS OV/UV, FAULT remains asserted as long as the fault exists.

After  $V_{CONN}$  is enabled on a CC channel, the IC monitors for additional faults related to  $V_{CONN}$  operation. On the first  $V_{CONN}$  fault and after the debounce time, the  $V_{CONN}$  switch is immediately turned off, the diagnostic current is enabled on the corresponding channel, and the short-to-ground comparator is active and monitoring HVCC.

Note that during the  $V_{CONN}$  fault conditions (except  $V_{CONN}$  OV), the CC pass-through switches are always on, which allows the PD Controller to monitor  $V_{CONN}$  for further diagnostics.

Automatic Discharge (MAX25410, MAX25410A) To comply with the Type-C specification, the HVCC pins will be discharged for 10ms every time  $V_{CONN}$  is disabled (i.e.,  $V_{CONN}_{EN1}$  goes from high to low for active-high variants, or goes from low to high for active-low variants).

#### Table 1. Fault Table

| FAULT                                                | COMPARATOR<br>DEBOUNCE<br>TIME PRIOR<br>TAKING<br>ACTION | ACTION TAKEN                                                                                                                                    | FAULT RECOVERY                                                                                                                                                                           |

|------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Thermal<br>Shutdown<br>(Die Temp<br>>165°C<br>(Typ)) | 100µs                                                    | Open CC pass-through switch, open data<br>switches, open V <sub>CONN</sub> switch, and reset<br>BC1.2 <u>charge</u> detection.<br>Assert FAULT. | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then discharge the HVCC1 and HVCC2 pins, then go to the current pin-configured state. |

| Bias<br>Overvoltage                                  | Immediate                                                | Open CC pass-through switch, open data switches, open V <sub>CONN</sub> switch, and reset BC1.2 charge detection.<br>Assert FAULT.              | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then discharge the HVCC1 and HVCC2 pins, then go to the current pin-configured state. |

## Automotive USB Power Delivery Port Protector

### Table 1. Fault Table (continued)

|                                                                                       | •         |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bias<br>Undervoltage                                                                  | 1.8ms     | Open CC pass-through switch, open data switches, open V <sub>CONN</sub> switch, and reset BC1.2 charge detection.<br>Assert FAULT.                                                                                                                                                | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then discharge the HVCC1 and HVCC2 pins, then go to the current pin-configured state.                                                                                                       |

| HVDM/<br>HVDP Pin<br>Overvoltage<br>or Short-to-<br>V <sub>BUS</sub>                  | Immediate | Open CC pass-through switch, open data<br>switches, open V <sub>CONN</sub> switch, and reset<br>BC1.2 <u>charge</u> detection.<br>Assert FAULT.                                                                                                                                   | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then discharge the HVCC1 and HVCC2 pins, then go to the current pin-configured state.                                                                                                       |

| V <sub>CC</sub> UVLO                                                                  | 16ms      | Open CC pass-through switch, open data switches, open V <sub>CONN</sub> switch, and reset BC1.2 charge detection.<br>Assert FAULT.                                                                                                                                                | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then discharge the HVCC1 and HVCC2 pins, then go to the current pin-configured state.                                                                                                       |

| V <sub>CC</sub> Fast UV<br>(Only when<br>V <sub>CONN</sub> is<br>Enabled)<br>(Note 5) | Immediate | Open V <sub>CONN</sub> switch.<br>Assert FAULT.                                                                                                                                                                                                                                   | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then re-start the $V_{CONN}$ switch based on the current $V_{CONN}_{EN1}$ and $V_{CONN}_{EN2}$ pin configuration.<br>No HVCC1 and HVCC2 discharge for this fault; ignore CDP/DCP pin state. |

| HVCC1/<br>HVCC2 Pin<br>Overvoltage<br>or Short-to-<br>V <sub>BUS</sub>                | Immediate | Open CC pass-through switch, open data<br>switches, open V <sub>CONN</sub> switch, and reset<br>BC1.2 <u>charge</u> detection.<br>Assert FAULT.                                                                                                                                   | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then discharge the HVCC1 and HVCC2 pins, then go to the current pin-configured state.                                                                                                       |

| V <sub>CONN</sub><br>Overcurrent<br>Threshold<br>(Low) (Note<br>5)                    | 400µs     | Open V <sub>CONN</sub> switch and if HVCC is below<br>the short-to-ground threshold, then assert<br>FAULT after 8ms. If HVCC is above the<br>short-to-ground threshold, restart the<br>V <sub>CONN</sub> switch. Assert FAULT if retry is<br>unsuccessful after two attempts.     | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then restart the $V_{CONN}$ switch based on the current $V_{CONN}$ EN1 and $V_{CONN}$ EN2 pin configuration. No HVCC1 and HVCC2 discharge for this fault; ignore CDP/DCP pin state.         |

| V <sub>CONN</sub><br>Overcurrent<br>Threshold<br>(High) (Note<br>5)                   | 5µs       | Open V <sub>CONN</sub> switch and<br>if HVCC is below the short-to-ground<br>threshold, then assert FAULT after 8ms. If<br>HVCC is above the short-to-ground<br>threshold, restart the V <sub>CONN</sub> switch. Assert<br>FAULT if re-try is unsuccessful after two<br>attempts. | When the fault condition no longer exists and the 16ms retry timer has expired, release the fault, then restart the $V_{CONN}$ switch based on the current $V_{CONN}$ EN1 and $V_{CONN}$ EN2 pin configuration. No HVCC1 and HVCC2 discharge for this fault; ignore CDP/DCP pin state.         |

| V <sub>CONN</sub><br>Overvoltage<br>(Note 5)                                          | Immediate | When HVCC1-to- $V_{CC}$ or HVCC2-to- $V_{CC}$ pin voltage exceeds 120mV (typ.) while $V_{CONN}$ is enabled:<br>open CC pass-through switch, open data switches, open $V_{CONN}$ switch, and reset BC1.2 charge detection.<br>Assert FAULT.                                        | When the fault condition no longer exists and the<br>16ms retry timer has expired, release the fault,<br>then discharge the HVCC1 and HVCC2 pins, then<br>go to the current pin-configured state.                                                                                              |

Note 5.  $V_{CONN}$  faults actions and fault recoveries are only applicable to MAX25410 and MAX2510A.

#### Power up and Enabling

### Supply and System Enable (V<sub>CC</sub>)

The V<sub>CC</sub> pin is the power-supply pin and also the internal chip-enable pin. All switches (CC1, CC2, D-, D+) remain ON any time that the V<sub>CC</sub> pin is above the undervoltage threshold and the FAULT pin is not asserted.

### **Modes of Operation**

### V<sub>CONN</sub> Switch/CC Pass-Through Switch Enable Tables Table 2. V<sub>CONN</sub> Switch-Enable Table (MAX25410: Active-High Variants)

|                                         | V                     | V                     | CC1/CC2      | HVCC1                    | HVCC2                    |

|-----------------------------------------|-----------------------|-----------------------|--------------|--------------------------|--------------------------|

| V <sub>CC</sub> > V <sub>CC</sub> _UVLO | V <sub>CONN_EN1</sub> | V <sub>CONN_EN2</sub> | PASS-THROUGH | V <sub>CONN</sub> SWITCH | V <sub>CONN</sub> SWITCH |

| No                                      | x                     | x                     | OFF          | OFF                      | OFF                      |

|                                         | 0                     | 0                     |              | OFF                      | OFF                      |

| Yes                                     | 0                     | 1                     | ON           | OFF                      | ON                       |

| Tes                                     | 1                     | 0                     | UN           | ON                       | OFF                      |

|                                         | 1                     | 1                     |              | OFF                      | OFF                      |

### Table 3. V<sub>CONN</sub> Switch-Enable Table (MAX25410A: Active-Low Variants)

| V <sub>CC</sub> > V <sub>CC_UVLO</sub> | V <sub>CONN_EN1</sub> | V <sub>CONN_EN2</sub> | CC1/CC2<br>PASS-THROUGH | HVCC1<br>V <sub>CONN</sub> SWITCH | HVCC2<br>V <sub>CONN</sub> SWITCH |

|----------------------------------------|-----------------------|-----------------------|-------------------------|-----------------------------------|-----------------------------------|

| No                                     | x                     | х                     | OFF                     | OFF                               | OFF                               |

|                                        | 0                     | 0                     |                         | OFF                               | OFF                               |

| Yes                                    | 0                     | 1                     | ON                      | ON                                | OFF                               |

| res                                    | 1                     | 0                     |                         | OFF                               | ON                                |

|                                        | 1                     | 1                     |                         | OFF                               | OFF                               |

### Table 4. CC Pass-Through Switch Enable Table (MAX25410B Variants)

| V <sub>CC</sub> > V <sub>CC_UVLO</sub> | CC1/CC2<br>PASS-THROUGH |

|----------------------------------------|-------------------------|

| No                                     | OFF                     |

| Yes                                    | ON                      |

#### **USB Host Adapter Emulator**

The USB protection switches integrate the latest USB-IF Battery-Charging Specification Revision 1.2 CDP and DCP circuitry, as well as 1.0A and 2.4A resistor-bias options for Apple-compliant devices. Legacy Samsung Galaxy 1.2V divider and China YD/T1591-2009 compatibility is also provided by the Auto-DCP mode.

### Table 5. Data Switch Mode Truth Table

| DEVICE                            | CDP/DCP PIN | CHARGE-DETECTION MODE       |

|-----------------------------------|-------------|-----------------------------|

| MAX25410BGTE/V+,                  | 0           | Auto-CDP                    |

| MAX25410AGTE/V+, MAX25410GTE/V+   | 1           | Auto-DCP/Apple 2.4A         |

| MAX25410BGTEA/V+,                 | 0           | Hi-Speed Pass-Through (SDP) |

| MAX25410AGTEA/V+, MAX25410GTEA/V+ | 1           | Auto-CDP                    |

#### USB On-the-Go and Dual-Role Applications

The MAX25410 is fully compatible with USB on-the-go (OTG) and dual-role applications. A negotiated role swap (HNP or Apple CarPlay) requires no software interaction with the IC. When there is no negotiation before the SoC enters peripheral mode, the MAX25410 must be in Hi-Speed pass-through (SDP mode) before and during the role swap. The MAX25410GTEA/V+, MAX25410AGTEA/V+ and MAX25410BGTEA/V+ default to SDP mode on startup if the CDP/DCP pin is logic-low. This configuration allows a role swap immediately on startup without microcontroller interaction

## Automotive USB Power Delivery Port Protector

### **Timing Diagrams/Test Circuits**

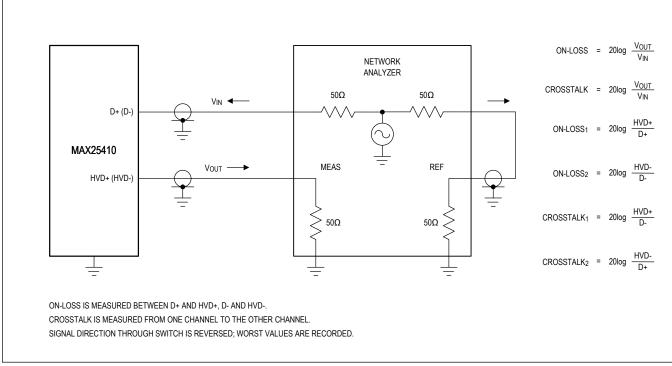

Figure 1. In-Channel -3dB Bandwidth and Crosstalk

### **Applications Information**

#### V<sub>CC</sub> Bypass Capacitor

$V_{CC}$  is the main IC supply, and the  $V_{CONN}$  switch input.  $V_{CC}$  requires a minimum 1µF ceramic capacitor (X5R or better) for input supply current and  $V_{CONN}$  switch usage. The capacitor must be as close as possible to the  $V_{CC}$  pin and have a short connection to the IC exposed pad. Using vias to connect to the ground layer is recommended. For best performance, use a low-impedance path to connect the 5V system power supply to the  $V_{CC}$  pin.

#### **BIAS Bypass Capacitor**

BIAS is the output of the internal LDO and clamp rail for the USB data switches. BIAS requires a minimum 1µF ceramic capacitor (X5R or better) for decoupling and to provide an AC return path on transient events (overvoltage, ESD). The capacitor must be as close as possible to the BIAS pin and have a short connection to the IC exposed pad. Ground flood over GND1 (pin 4) is recommended.

#### Layout of USB Data-Line Traces

USB Hi-Speed mode requires careful PCB layout with  $90\Omega$  controlled differential impedance-matched traces of equal length. Insert tuning peaking inductors and capacitors on the D+, D-, HVD+, and HVD- pins to tune out parasitic capacitance. The values are layout dependent. Contact Maxim Applications for assistance.

#### Tuning of USB Data Lines

USB Hi-Speed mode requires careful PCB layout with  $90\Omega$  controlled differential impedance, with matched traces of equal length and with no stubs or test points. MAX25410 includes high-bandwidth USB data switches (1GHz). This means data-line tuning is generally not required.

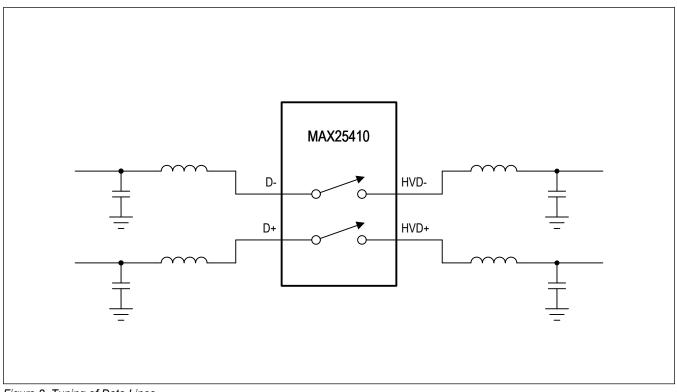

However, all designs are recommended to include pads that would allow LC components to be mounted on the data lines so that tuning can easily be performed later, if necessary. Tuning components should be placed as close as possible to the IC data pins, on the same layer of the PCB as the IC. The proper configuration of the tuning components is shown in <u>Figure 2</u>. Tuning inductors should be high-Q wire-wound inductors. Contact Maxim's application team for assistance with the tuning process for your specific application.

Figure 2. Tuning of Data Lines

#### ±15kV ESD Protection

Maxim devices incorporate ESD-protection structures to protect against electrostatic discharges encountered during handling and assembly. The devices provide additional protection against static electricity. Maxim's state-of-the-art structures protect against ESD of ±15kV on HVD+, HVD-, HVCC1, and HVCC2. The ESD structures withstand high ESD in all states: normal operation, shutdown, and powered down. While other solutions can latch up and require the power to be cycled after an ESD event, MAX25410 devices continue to work without latchup. The devices are characterized for protection to the following limits:

- 1. ±2kV using the Human Body Model

- 2. ±15kV using the IEC 61000-4-2 Air Gap method

- 3. ±8kV using the IEC 61000-4-2 Contact Discharge method

- 4. ±15kV using the ISO 10605 Air Gap method

- 5. ±8kV using the ISO 10605 Contact Discharge method

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

#### Human Body Model

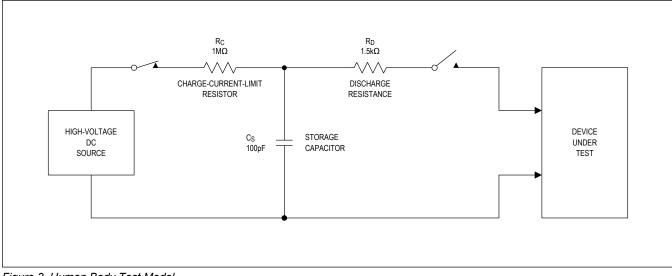

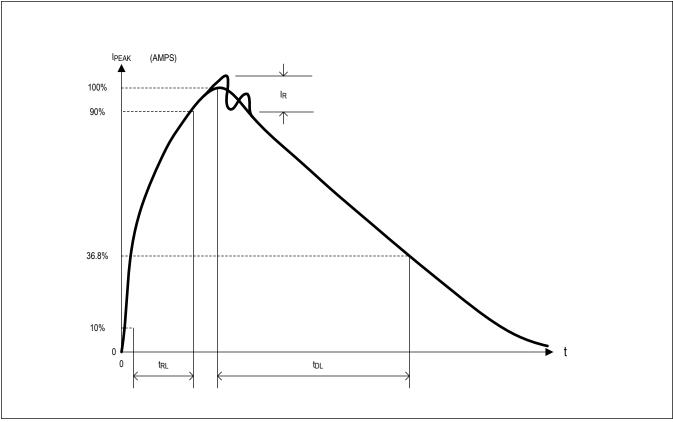

<u>Figure 3</u> shows the Human Body Model, and <u>Figure 4</u> shows the current waveform it generates when discharged into a low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a  $1.5k\Omega$  resistor.

### Human Body Test Model

Figure 3. Human Body Test Model

### Human Body Current Waveform

Figure 4. Human Body Current Waveform

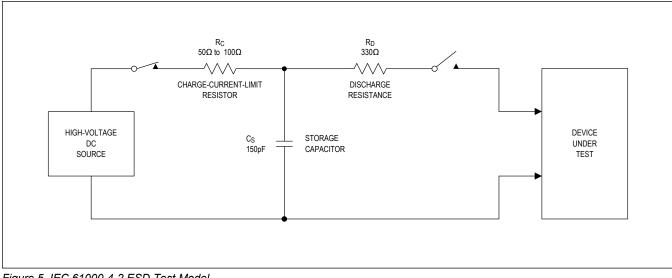

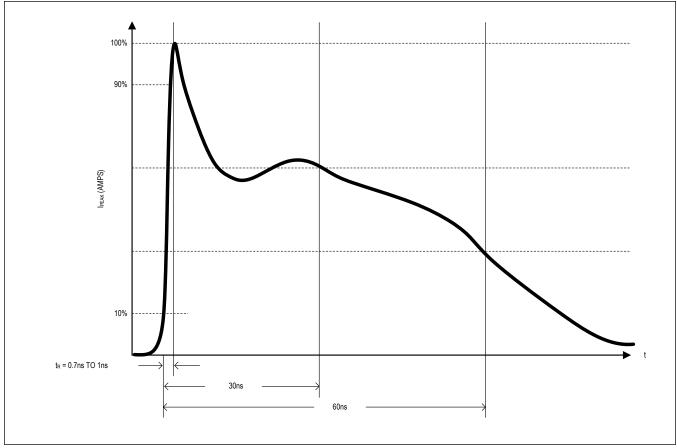

### IEC 61000-4-2

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. The devices help users design equipment that meet Level 4 of IEC 61000-4-2. The Human Body Model testing is performed on unpowered devices, while IEC 61000-4-2 is performed while the device is powered. The main difference between tests done using the Human Body Model and IEC 61000-4-2 is higher peak current in IEC 61000-4-2. Because series resistance is lower in the IEC 61000-4-2 ESD test model (Figure 5), the ESD-withstand voltage measured to this standard is generally lower than that measured using the Human Body Model. Figure 6 shows the current waveform for the ±8kV, IEC 61000-4-2 Level 4, ESD Contact Discharge test. The Air Gap Discharge test involves approaching the device with a charged probe. The Contact Discharge method connects the probe to the device before the probe is energized.

### IEC 61000-4-2 ESD Test Model

Figure 5. IEC 61000-4-2 ESD Test Model

### IEC 61000-4-2 ESD Generator Current Waveform

Figure 6. IEC 61000-4-2 ESD Generator Current Waveform

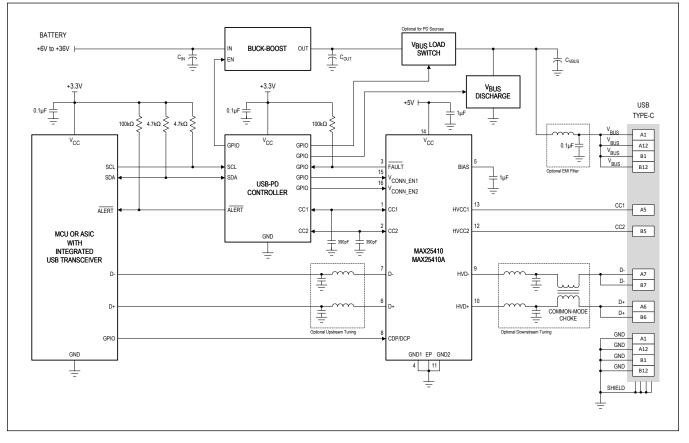

## **Typical Application Circuits**

### MAX25410, MAX25410A

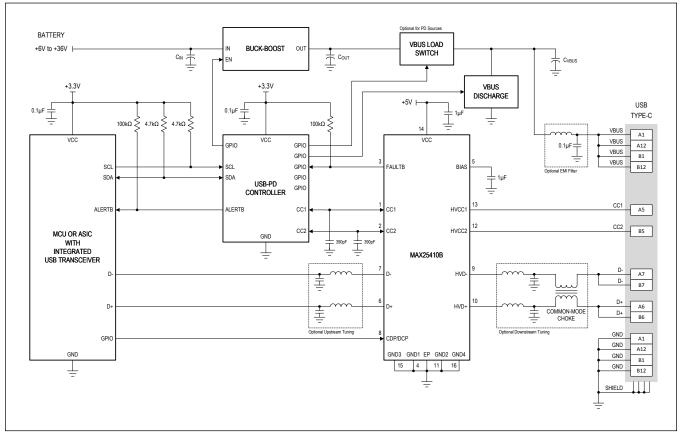

## **Typical Application Circuits (continued)**

#### MAX25410B

### **Ordering Information**

| PART NUMBER      | V <sub>CONN</sub> | V <sub>CONN</sub> ENABLE<br>POLARITY | USB MODES SUPPORTED           | TEMPERATURE<br>RANGE | PIN-<br>PACKAGE   |

|------------------|-------------------|--------------------------------------|-------------------------------|----------------------|-------------------|

| MAX25410AGTE/V+  | Yes               | Active-Low                           |                               | -40°C to +105°C      | TQFN-EP<br>16-pin |

| MAX25410GTE/V+   | res               | Active-High                          | Auto-CDP, Auto-DCP/Apple 2.4A |                      |                   |

| MAX25410BGTE/V+  | No                | -                                    |                               |                      |                   |

| MAX25410AGTEA/V+ | Yes               | Active-Low                           |                               |                      |                   |

| MAX25410GTEA/V+  | res               | Active-High                          | Auto-CDP, SDP(Pass-Through)   |                      |                   |

| MAX25410BGTEA/V+ | No                | -                                    |                               |                      |                   |

All devices operate over the temperature range of -40°C to +105°C and support USB CDP/HS modes.

To order Tape and Reel, suffix the part number with a T. Example: MAX25410GTE/V+T

/V denotes AEC-Q100 Automotive Qualified.

+ Denotes Lead(Pb)-Free/RoHS-compliant package.

EP denotes Exposed Pad

## Automotive USB Power Delivery Port Protector

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                          | PAGES<br>CHANGED                |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 0                  | 8/19             | Initial release                                                                                                                                                                                      | —                               |

| 1                  | 10/19            | Updated Ordering Information                                                                                                                                                                         | 25                              |

| 2                  | 4/20             | Updated General Description, Electrical Characteristics, Pin Configurations,<br>Functional Diagrams, Detailed Description, Modes of Operation, Typical Application<br>Circuits, Ordering Information | 1, 4, 5, 9, 10,<br>12–17, 25–27 |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

MAX25410AGTE/V+ MAX25410GTE/V+T MAX25410AGTEA/V+ MAX25410GTEA/V+ MAX25410GTEA/V+T MAX25410AGTE/V+T MAX25410AGTEA/V+T MAX25410GTE/V+ MAX25410BGTEA/V+T MAX25410BGTE/V+ MAX25410BGTE/V+T