# SRK1000 / SRK1000A / SRK1000B

## Adaptive synchronous rectification controller for flyback converter

Datasheet - production data

## Features

- Secondary side synchronous rectification controller optimized for flyback converter

- Suitable for QR and mixed CCM/DCM fixed frequency operation

- Wide Vcc operating voltage range 3.75 to 32 V

- CC regulation operation down to 2 V output supported

- Very low quiescent current in low consumption mode (160 μA)

- High-voltage sensing input for SR MOSFET drain-source voltage (100 V AMR)

- Operating frequency up to 300 kHz

- High-current gate-drive output for N-MOSFET

- Fast turn-on with minimum delay time and adaptive turn-off logic

- Programmable min. T<sub>ON</sub> and fixed min. T<sub>OFF</sub> (3 options: SRK1000, SRK1000A, SRK1000B)

- Low consumption mode entry by primary side burst-mode detection or by detection of SR MOSFET conduction lower than programmed min T<sub>ON</sub>

- SOT23-6L package

## Applications

- Battery chargers / quick chargers

- Adapters

- USB power delivery (profile 3)

#### July 2019

DS12787 Rev 3

## Description

The SRK1000 is a controller intended for secondary side synchronous rectification (SR) in flyback converters, suitable for operation in QR and mixed CCM/DCM fixed frequency circuits.

It provides a high-current gate-drive output, capable of driving N-channel Power MOSFETs.

The control scheme of this IC is such that the SR MOSFET is switched on as soon as current starts flowing through its body diode and it is then switched off as current approaches zero.

The fast turn-on, with minimum delay, and the innovative adaptive turn-off logic allow maximizing the conduction time of the SR MOSFET and eliminating the effect of parasitic inductance in the circuit.

The device enters low consumption mode when it detects primary controller burst-mode operation, or when the SR MOSFET conduction becomes lower than the programmed minimum  $T_{ON}$ . In this way, converter efficiency improves at light load where synchronous rectification is no longer beneficial.

After the converter restarts switching or the IC detects that the current conduction in the rectifiers has increased 20% above the min  $T_{ON}$  programmed value, the IC exits low consumption mode and resumes switching operation.

| Table | 1. | Device | summa | ry |

|-------|----|--------|-------|----|

|       |    |        |       |    |

| Tuble 11 Device cullulary |          |               |  |  |  |  |

|---------------------------|----------|---------------|--|--|--|--|

| Part number               | Package  | Packing       |  |  |  |  |

| SRK1000                   |          |               |  |  |  |  |

| SRK1000ATR                | SOT23-6L | Tape and reel |  |  |  |  |

| SRK1000BTR                |          |               |  |  |  |  |

This is information on a product in full production.

# Contents

| 1 | Block                      | Block diagram and pin connections                                            |  |  |  |  |  |

|---|----------------------------|------------------------------------------------------------------------------|--|--|--|--|--|

| 2 | Maxir                      | Maximum ratings                                                              |  |  |  |  |  |

| 3 | Туріс                      | al application schematics6                                                   |  |  |  |  |  |

| 4 | Elect                      | rical characteristics8                                                       |  |  |  |  |  |

| 5 | Opera                      | ation description                                                            |  |  |  |  |  |

|   | 5.1                        | Drain voltage sensing 12                                                     |  |  |  |  |  |

|   | 5.2                        | Turn-on                                                                      |  |  |  |  |  |

|   | 5.3                        | Minimum TON programming 12                                                   |  |  |  |  |  |

|   | 5.4                        | Adaptive turn-off and TIMER 13                                               |  |  |  |  |  |

|   | 5.5                        | Minimum TOFF                                                                 |  |  |  |  |  |

|   | 5.6                        | Start-up phase                                                               |  |  |  |  |  |

|   | 5.7                        | Low consumption mode operation: sleep mode and burst mode $\ldots \ldots 17$ |  |  |  |  |  |

|   | 5.8                        | VAUX pin operation in CC regulation                                          |  |  |  |  |  |

|   | 5.9                        | Operation in CC regulation and short-circuit                                 |  |  |  |  |  |

|   | 5.10                       | Adaptive gate drive                                                          |  |  |  |  |  |

| 6 | Layou                      | ut guidelines                                                                |  |  |  |  |  |

| 7 | Package mechanical data 24 |                                                                              |  |  |  |  |  |

| 8 | Revision history           |                                                                              |  |  |  |  |  |

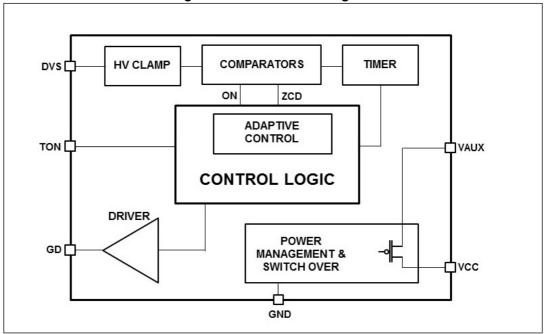

## **1** Block diagram and pin connections

Figure 1. Internal block diagram

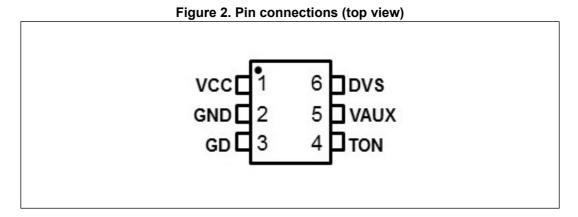

Table 2. Pin functions

| No. | Name | Function                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | VCC  | Supply voltage of the device. A bypass capacitor to GND, located as close to IC's pins as possible, helps to obtain a clean supply voltage for the internal control circuitry and acts as an effective energy buffer for the pulsed gate-drive current.                                                                                    |  |  |  |

| 2   | GND  | Return of the device bias current and return of the gate-drive current. Route this pin close to the source terminal of synchronous rectifier MOSFET.                                                                                                                                                                                       |  |  |  |

| 3   | GD   | Gate driver output. Totem pole output stage is able to drive the Power MOSFET with high peak current levels. To avoid excessive gate voltages where the device is supplied with a high VCC, the high level voltage of this pin is clamped to about 11.6 V (typ. value). The pin must be connected directly to the SR MOSFET gate terminal. |  |  |  |

| No. | Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | TON  | Programming pin for blanking time after turn-on. A resistor connected from this pin to GND, supplied by an internal current source, sets a voltage $V_{TON}$ ; depending on this voltage level, the user can choose the blanking time after turn-on, suitable to mask ZCD comparator output and avoid premature turn-off due to parasitic voltage oscillation on the DVS pin. In tracking with $V_{TON}$ , the thresholds to enter/exit automatic sleep mode are derived.<br>A capacitor larger than 60 pF (100 pF typ.) between this pin and GND sets the internal timer mode for SR MOSFET turn-off in mixed CCM/DCM operation. If no capacitor is used, timer mode is set for turn-off in QR or DCM operation. |

| 5   | VAUX | Auxiliary suppy voltage of the device. When VCC voltage is lower than the UVLO voltage threshold (Vcc_so_on), the bypass capacitor on the VCC pin (coupled to application V <sub>OUT</sub> through a diode) is supplied by the VAUX pin, if this is connected to an auxiliary winding or to an external capacitor sourced by a DVS voltage rectifier. If the functionality is not used, the VAUX pin must be connected to the VCC pin.                                                                                                                                                                                                                                                                            |

| 6   | DVS  | Drain voltage sensing. This pin must be connected to the drain terminal of the synchronous rectifier MOSFET through a series resistor of at least of 300 $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Table 2. Pin functions

# 2 Maximum ratings

| Symbol | Pin | Parameter                           | Value       | Unit |

|--------|-----|-------------------------------------|-------------|------|

| VCC    | 1   | DC supply voltage                   | -0.3 to 36  | V    |

| VTON   | 4   | TON pin voltage rating              | -0.3 to 36  | V    |

| VAUX   | 5   | Auxiliary DC supply voltage         | -0.3 to 100 | V    |

| DVS    | 6   | Drain sense voltage referred to GND | -3 to 100   | V    |

Table 3. Absolute maximum ratings

Stressing the device above the rating listed in *Table 3* may cause permanent damage to the device. Exposure to absolute maximum rated conditions may affect device reliability.

| Symbol                 | Parameter                                             | Value      | Unit |

|------------------------|-------------------------------------------------------|------------|------|

| R <sub>th j-amb</sub>  | Junction-to-ambient thermal resistance <sup>(1)</sup> | 200        | °C/W |

| R <sub>th j-case</sub> | Junction-to-case thermal resistance <sup>(1)</sup>    | 60         | °C/W |

| P <sub>tot</sub>       | Power dissipation at T <sub>amb</sub> = 50 °C         | 0.5        | W    |

| Тj                     | Junction temperature operating range                  | -40 to 150 | °C   |

| T <sub>stg</sub>       | Storage temperature                                   | -55 to 150 | °C   |

#### Table 4. Thermal data

With pin 2 soldered to a dissipating copper area of 10 mm<sup>2</sup>, 35 μm thickness (PCB material FR4 1.6 mm thickness).

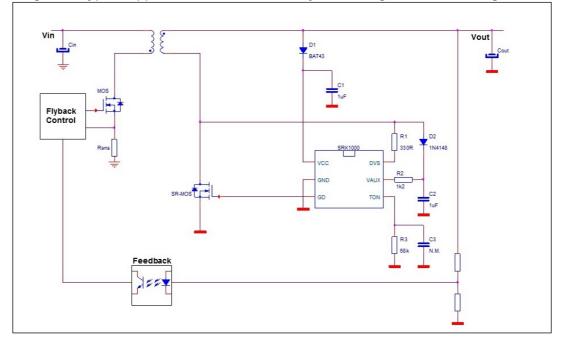

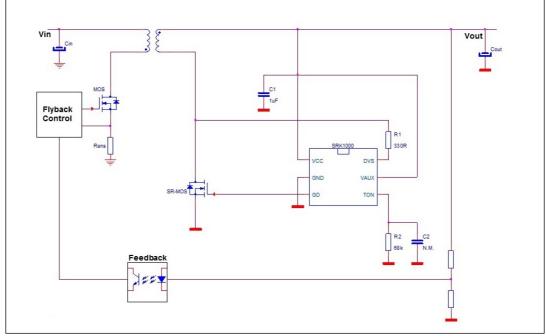

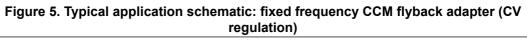

# 3 Typical application schematics

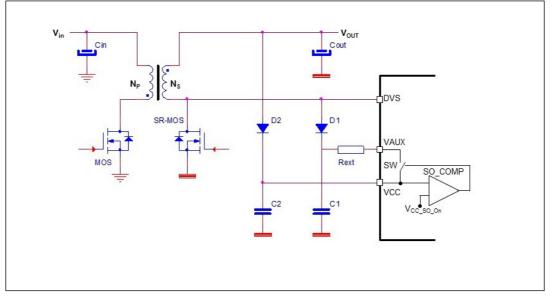

Figure 3. Typical application schematic: QR flyback charger with CV-CC regulation

Figure 4. Typical application schematic: QR flyback adapter (CV regulation)

# 4 Electrical characteristics

(T<sub>j</sub> = -25 °C to 125 °C, V<sub>CC</sub> = 12 V, C<sub>GD</sub> = 4.7 nF, unless otherwise specified, typical values refer to T<sub>j</sub> = 25 °C).

| Symbol                   | Parameter                                                                    | Test condition                                                                         | Min. | Тур. | Max. | Unit |

|--------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| Supply section           |                                                                              |                                                                                        |      |      |      |      |

| V <sub>AUX</sub>         | VAUX pin operating voltage                                                   |                                                                                        |      |      | 90   | V    |

| V <sub>CC</sub>          | Operating voltage range                                                      | After turn-on                                                                          | 3.75 |      | 32   | V    |

| V <sub>CC_On</sub>       | Turn-on supply voltage                                                       | Voltage rising <sup>(1)</sup>                                                          | 4.18 | 4.3  | 4.42 | V    |

| V <sub>CC_SO_On</sub>    | Turn-on supply voltage for VAUX switch activation                            | Voltage falling <sup>(1)</sup>                                                         | 3.75 | 3.95 | 4.15 |      |

| V <sub>CC_Off</sub>      | Turn-off supply voltage                                                      | Voltage falling <sup>(1)</sup>                                                         | 3.3  | 3.5  | 3.75 | V    |

| V <sub>CC_AGD_en</sub>   | $V_{CC}$ voltage above which adaptive drive is enabled                       | On V <sub>CC</sub> rising edge <sup>(2)</sup>                                          |      | 7.4  |      | V    |

| V <sub>CC_AGD_dis</sub>  | $V_{CC}$ voltage below which adaptive drive is disabled                      | On V <sub>CC</sub> falling edge <sup>(2)</sup>                                         |      | 6.5  |      | V    |

| I <sub>q_run</sub>       | Current consumption in run mode                                              | After turn-on (excluding SR MOS gate driving) @ 100 kHz                                |      | 600  |      | μA   |

| I <sub>CC</sub>          | Operating supply current                                                     | @ 300 kHz                                                                              |      | 17   |      | mA   |

| Ι <sub>q</sub>           | Quiescent current                                                            | Burst mode operation, DVS pin not switching,<br>Tj = $-25^{\circ}$ C to $85^{\circ}$ C |      | 160  | 210  | μA   |

| R <sub>on</sub>          | VAUX switch resistance                                                       |                                                                                        |      | 40   |      | Ω    |

| Drain-source se          | ensing inputs and synch functions                                            |                                                                                        |      |      |      |      |

| V <sub>DS</sub>          | DVS operating voltage                                                        |                                                                                        |      |      | 90   | V    |

| V <sub>TH_A</sub>        | Cycle comparator threshold                                                   |                                                                                        | 70   | 100  | 130  | mV   |

| V <sub>ZCD_OFF_MIN</sub> | Minimum ZCD comparator threshold                                             | (2)                                                                                    |      | -20  |      | mV   |

| T <sub>diode_off</sub>   | Body diode residual conduction time after turn-off                           |                                                                                        | 230  | 330  | 430  | ns   |

| T <sub>D_On</sub>        | Turn-on delay                                                                |                                                                                        | 55   | 85   | 105  | ns   |

| T <sub>ant_timer</sub>   | Anticipation time referred to DVS rising edge to force turn-off of SR MOSFET | DVS switching<br>Low level on DVS pin = -1 V                                           | 175  | 250  | 325  | ns   |

| T <sub>timer_step</sub>  | Timer step every 4 switching cycles (in FF operation)                        | With 100 pF on TON pin, during switching period increase                               |      | 56   |      | ns   |

| T <sub>ON_MAX</sub>      | Max. turn-on duration                                                        |                                                                                        | 45   | 60   | 80   | μs   |

|                          | fter turn-on and after turn-off                                              | •                                                                                      |      |      |      |      |

| <b>-</b>                 | Minimum turn-on time programmable by                                         | R <sub>TON_MIN</sub> = 33 kΩ                                                           | 0.28 | 0.4  | 0.52 |      |

| T <sub>ON_MIN</sub>      | $R_{TON}$ in the range [33 $\Omega$ - 250 $\Omega$ ]                         | <br>R <sub>TON_MAX</sub> = 250 kΩ                                                      | 2.1  | 3.0  | 3.9  | μs   |

#### Table 5. Electrical characteristics

8/27

| Symbol                    | Parameter                                                                                                  | Test condition                                   | Min. | Тур. | Max. | Unit |

|---------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|------|------|------|

| I <sub>TON</sub>          | Sourced current                                                                                            | In run mode                                      |      | 8    |      | μA   |

|                           |                                                                                                            | SRK1000                                          | 0.35 | 0.5  | 0.65 |      |

| T <sub>OFF_MIN</sub>      | Fixed blanking time after turn-off (with DVS voltage continuously above V <sub>TH_A</sub> )                | SRK1000A                                         | 1.4  | 2    | 2.6  | μs   |

|                           | Bite totage continuedory abore t <sub>IH_A</sub>                                                           | SRK1000B                                         | 2.1  | 3    | 3.9  |      |

| Low consumpt              | ion mode                                                                                                   |                                                  |      |      |      |      |

|                           | Minimum operating current conduction                                                                       | R <sub>TON_MIN</sub> = 33 kΩ                     | 0.49 | 0.7  | 0.91 |      |

| T <sub>ON_sleep_in</sub>  | time to enter sleep mode:<br>T <sub>ON_sleep_in</sub> = T <sub>ON_MIN</sub> + 300 ns                       | R <sub>TON_MAX</sub> = 250 kΩ                    | 2.3  | 3.3  | 43   | μs   |

|                           | Restart current conduction time from sleep                                                                 | R <sub>TON_MIN</sub> = 33 kΩ                     | 0.55 | 0.78 | 1.01 | μs   |

| T <sub>ON_sleep_out</sub> | mode:<br>T <sub>ON_sleep_out</sub> = 1.2 T <sub>ON_MIN</sub> + 300 ns                                      | R <sub>TON_MAX</sub> = 250 kΩ                    | 2.73 | 3.9  | 5.07 |      |

| T <sub>STOP</sub>         | Switching stop time interval detection to<br>enter low consumption mode (primary<br>controller burst mode) |                                                  | 80   | 120  | 160  | μs   |

| Gate drivers              |                                                                                                            |                                                  |      |      | •    |      |

| I <sub>source_pk</sub>    | Output source peak current                                                                                 | See <sup>(2)</sup>                               |      | 0.6  |      | Α    |

| I <sub>sink_pk</sub>      | Output sink peak current                                                                                   | See <sup>(2)</sup>                               |      | 1    |      | Α    |

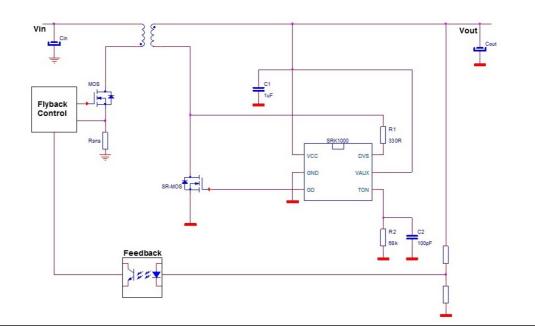

| 4                         | Rise time (see <i>Figure 6</i> )                                                                           | V <sub>CC</sub> = 20 V, C <sub>GD</sub> = 4.7 nF |      | 45   |      |      |

| t <sub>r_1</sub>          | Rise time (see Figure 0)                                                                                   | V <sub>CC</sub> = 20 V, C <sub>GD</sub> = 10 nF  |      | 75   |      | ns   |

| 4                         | Disa tima (asa <i>Figura</i> 6)                                                                            | V <sub>CC</sub> = 20 V, C <sub>GD</sub> = 4.7 nF |      | 140  |      |      |

| t <sub>r_2</sub>          | Rise time (see <i>Figure 6</i> )                                                                           | V <sub>CC</sub> = 20 V, C <sub>GD</sub> = 10 nF  |      | 140  |      | ns   |

| t <sub>f</sub>            | Fall time (see <i>Figure 6</i> )                                                                           | V <sub>CC</sub> = 20 V, C <sub>GD</sub> = 4.7 nF |      | 60   |      | ns   |

|                           | Fail time (see Figure 0)                                                                                   | V <sub>CC</sub> = 20 V, C <sub>GD</sub> = 10 nF  |      | 120  |      | 115  |

| V <sub>GDclamp</sub>      | Drive clamp voltage                                                                                        | $V_{CC} = 20 V^{(3)}$                            | 10.6 | 11.6 | 12.6 | V    |

| V <sub>GD_ad-step</sub>   | Adaptive driving step voltage                                                                              | $V_{CC} = 20 V^{(3)}$                            |      | 400  |      | mV   |

| V <sub>GDL_UVLO</sub>     | UVLO saturation                                                                                            | $V_{CC} = 0$ to $V_{CCOn}$ , $I_{sink} = 5$ mA   |      | 1    | 1.3  | V    |

Table 5. Electrical characteristics (continued)

1. Parameters tracking each other.

2. Parameter guaranteed by design.

3. Parameters tracking each other.

Figure 6. Rise and fall time definition

## 5 Operation description

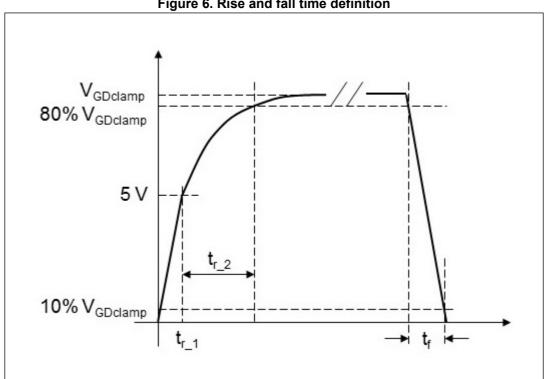

The SRK1000 (see *Figure 1*) is a controller specifically designed for synchronous rectification in flyback converters operating in QR or mixed CCM/DCM fixed frequency. This IC basically turns on the SR MOSFET with a minimum delay when the rectified current starts flowing through the body diode, and turns off the SR MOSFET when current approaches zero, using an adaptive mechanism that leads the body diode residual conduction time after turn-off to the target value T<sub>diode\_off</sub> (refer to *Table 5: Electrical characteristics* for the various parameter values).

The adaptive turn-off method presents some advantages, compared to a standard one based on a comparator with fixed threshold. The first advantage is that the adaptive method automatically compensates stray inductances  $L_S$  in series to rectified current path: this parasitic (mainly the SR MOSFET package inductances in series to drain and source terminals) normally produces an offset on the sensed voltage across MOSFET  $R_{DS_ON}$  that anticipates by  $T_X = L_S/R_{DS_ON}$  the turn-off in case of standard comparator.

The second aspect to consider is that a standard comparator with fixed threshold turns off at a current level  $I_{OFF}$  that depends on  $R_{DS\_ON}$  of the chosen SR MOSFET. Referring to the image in *Figure* 7 and considering a fixed comparator threshold  $V_{TH} = -5$  mV, the turn-off current in the rectifier can be calculated. In an application with an SR MOSFET having channel resistance  $R_{DS\_ON} = 2.5$  m $\Omega$  and package stray inductance  $L_S = 2.5$  nH, where the current slope is di/dt = -3 A/µs (for example starting from a peak current of 15 A with 5 µs transformer demagnetization), the turn-off current is:

$I_{OFF} = -V_{TH}/R_{DS}$  ON -  $T_X$  di/dt = 5 A, for comparator turn-off.

$I_{OFF AD} = -T_{diode off} di/dt = 0.9 A$ , for adaptive turn-off.

Furthermore, the adaptive turn-off method has a better behavior also in applications with CC regulation, where the standard comparator with fixed threshold anticipates more and more the turn-off during load impedance decreasing (since current slope continues to decrease too), while adaptive method fixes  $T_{diode\ off}$ .

The SRK1000 controller starts operation when the VCC pin voltage surpasses the turn-on threshold V<sub>CC\_On</sub>; then it stops operation when the V<sub>CC</sub> voltage drops below the turn-off threshold V<sub>CC\_Off</sub>.

In order to guarantee SR switching even with low V<sub>CC</sub> supply voltage, in the case of chargers operating in CC regulation, the device is provided with the VAUX pin. When the V<sub>CC</sub> voltage decreases below the threshold V<sub>CC\_SO\_On</sub> (> V<sub>CC\_Off</sub>), an internal switch is turned on allowing the VCC pin capacitor to be charged up to the turn-on threshold V<sub>CC\_On</sub> by a current drawn through the VAUX pin connected, for example, to the rectified SR MOSFET drain voltage or to another auxiliary voltage of the flyback transformer.

For the maximum flexibility in different applications and to overcome noise and ringing problems that may arise after SR MOSFET turn-on, the SRK1000 allows the user to program the blanking time after turn-on through a resistor connected between the TON pin and GND. The blanking time after turn-off is instead internally fixed to T<sub>OFF MIN</sub>.

Figure 7. Comparison between adaptive turn-off and comparator based turn-off

#### 5.1 Drain voltage sensing

The drain voltage of the SR MOSFET is sensed through the DVS pin: this is a high-voltage pin and needs to be properly routed to the MOSFET drain, through a resistor of at least 300  $\Omega$  (in order to limit dynamic current injection in any condition). The DVS signal is used to detect when current flows through the MOSFET body diode and for the internal timings.

## 5.2 Turn-on

After the flyback converter primary switch has been turned off, the voltage across the transformer reverses and the SR MOSFET drain voltage quickly decreases and goes negative (-V<sub>F</sub>), allowing the rectifier current to flow. Consequently, triggered on the falling edge of the DVS signal (when it decreases below the cycle comparator threshold  $V_{TH_A}$ ), the controller turns on the SR MOSFET, with a very short delay  $T_{D_On}$ . After turn-on, the sensed DVS signal passes from the (negative) body diode forward voltage to the drop across the MOSFET channel resistance ( $R_{DS_ON}$ ).

This drop is generally affected by some amount of noise, associated with the flyback transformer leakage inductance, and this could trigger a premature turn-off of the SR MOSFET.

## 5.3 Minimum TON programming

In order to avoid premature turn-off of the SR MOSFET due to ringing and oscillations, the IC allows the user to program a blanking time after turn-on. The circuit bases on an internal timing capacitance and an external resistor  $R_{TON}$  connected from the TON pin to ground. The blanking time settlement is done according to the following expression:

Equation 1

$$T_{ON MIN} = 12 \ 10^{-12} \ R_{TON}$$

(with R<sub>TON</sub> expressed in ohm and T<sub>ON\_MIN</sub> in seconds, starting when the DVS signal goes below  $V_{TH\_A}$ ). This blanking time of course sets a minimum turn-on time of the SR MOSFET as well: hence, when by reducing the load the SR MOSFET conduction time would become shorter than the programmed blanking time, the IC must stop driving the SR MOSFET to avoid current inversion (see Section 5.7: Low consumption mode operation: sleep mode and burst mode below).

#### 5.4 Adaptive turn-off and TIMER

The SR MOSFET can be turned off through two coexisting mechanisms (whichever triggers first); the first based on an adaptive algorithm, the second on the internal timer.

The adaptive turn-off consists of a ZCD\_OFF comparator, where the DVS signal is compared to an adapting threshold. This threshold is adapted in such a way that, at steady state, the measured residual conduction time of the SR MOSFET body diode after turn-off meets the target value  $T_{diode\_off}$  (as shown in *Figure 8*). The residual conduction time of the body diode is measured between the falling edge of the driving signal and the rising edge of the DVS signal (first time surpassing the threshold V<sub>TH A</sub>).

Figure 8. ZCD\_OFF threshold adapting for body diode target conduction

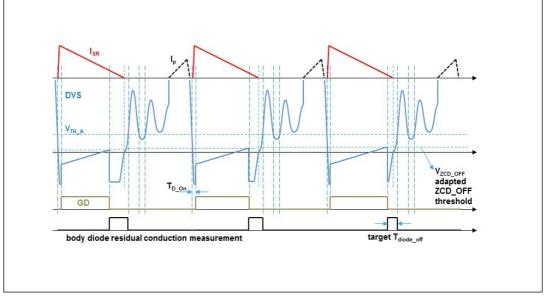

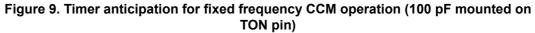

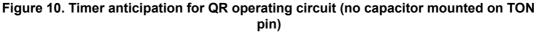

The internal timer basically turns off the SR MOSFET with a fixed anticipation time T<sub>ant\_timer</sub> with respect to the first rising edge of the DVS signal. The IC has two different timer operating modes, selectable by the user, optimized for fixed frequency mixed CCM/DCM converters or for QR/DCM applications. The selection of the proper timer mode is done

through a 100 pF capacitor across the TON pin: if it is present, mixed CCM/DCM operation is assumed; if the capacitor is not present, QR/DCM operation is assumed.

Here below the various operating modes are described.

Fixed frequency mixed DCM/CCM operation:

In fixed frequency operation, the SR MOSFET turn-off is triggered by ZCD\_OFF adaptive mechanism at load levels where DCM operation occurs, while it is triggered by timer at higher loads, where CCM operation occurs. The latter consists in turning off the SR MOSFET with a fixed anticipation time  $T_{ant\_timer}$  with respect to the first rising edge of the DVS signal, basing on a switching period  $T_{SW}$  estimate, (over few previous cycles) as illustrated in *Figure 9*.

Turn-off by timer may take over also during low-to-high load transients, where the ZCD\_OFF comparator threshold is in the adapting phase (close to the zero crossing and could not turn-off per time), preventing undesired current inversions.

Most of the flyback controllers available on the market, in order to help optimize the EMI filter, use operating frequency modulation. For correct operation of the SRK1000 timer, the maximum rate of change of modulated frequency must be limited, so that the switching period increase from current to next cycle results much shorter than the timer anticipation  $T_{ant\_timer}$  (14 ns maximum). In fact, the timer anticipation adapting during switching period increase is limited to  $T_{timer\_step}$  every 4 cycles and with a switching period increase longer than 14 ns from one cycle to the next, the timer turn-off would progressively anticipate (increasing the body diode conduction).

In QR flyback application the circuit works at variable frequency and, after transformer demagnetization, a resonance occurs due to primary inductance and total parasitic capacitance across primary switch. In this case, at steady state, SR MOSFET turn-off is triggered by ZCD\_OFF adaptive mechanism.

During load transitions or during CC regulation operation (where output voltage may decrease), turn-off by adaptive ZCD\_OFF comparator would be too late (since the threshold needs to adapt to the new slope of current flowing into the SR MOSFET), while turn-off by internal timer prevents current inversion.

The timer for fixed frequency CCM is not suitable in QR operation (that inherently operates at variable frequency). In this case, the timer operating mode consists in turning off the SR MOSFET with a fixed anticipation time  $T_{ant\_timer}$  with respect to the first rising edge of the DVS signal, based on the duration of the previous demagnetization time of transformer  $T_{dem}$ , as shown in *Figure 10*.

Looking at the image in *Figure 10*, during the first two switching cycles (steady state operation) the turn-off is triggered by the ZCD\_OFF comparator. This is because the DVS signal reaches the adapted ZCD\_OFF threshold before the timer OFF event (since target diode  $T_{diode_off}$  is larger than timer anticipation  $T_{ant\_timer}$ ). In the third switching cycle, as a consequence of the transient, the turn-off is instead triggered by the timer, since current slope has decreased and the ZCD\_OFF threshold would be reached too late. In the following cycle (not shown in the figure) the timer settles the anticipation to the duration of the demagnetization period of the third cycle.

#### Fixed frequency DCM operation:

In fixed frequency circuits designed to operate always in DCM in all line and load conditions, the SRK1000 operates basically like in the case of QR operation: the turn-off is accomplished by adaptive mechanism in steady state operation, while timer turn-off is invoked to protect against current inversion during load transitions and in CC regulation. In this case, the timer mode can be either the one for FF CCM or the one for QR application; the preferred one is the latter, as it is less expensive (no capacitor on the TON pin is required).

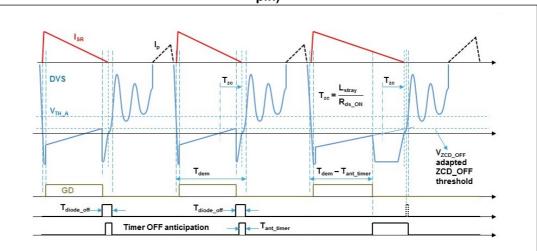

#### 5.5 Minimum TOFF

In flyback applications operating in DCM and QR with valley skipping, a resonance takes place across transformer windings after demagnetization, whose period  $T_{RES}$  depends on the transformer primary inductance and on the total capacitance across primary switch. In

order to avoid this ringing affecting SRK1000 internal timings, an internally fixed blanking time ( $T_{OFF\ MIN}$ ) after turn-off is provided.

Referring to *Figure 11*, the circuit provides a blanking time from the falling edge of the driving signal to the time instant occurring after the DVS pin voltage, ( $V_{DS}$ ) is permanently higher than  $V_{TH}$  A for  $T_{OFF}$  MIN.

The device allows for three different choices of blanking after turn-off, according to the selected option (SRK1000, SRK1000A and SRK1000B): for correct operation, the user must select the device option with  $T_{OFF\mmodel{optimes}min} > T_{RES}$  (the ringing period).

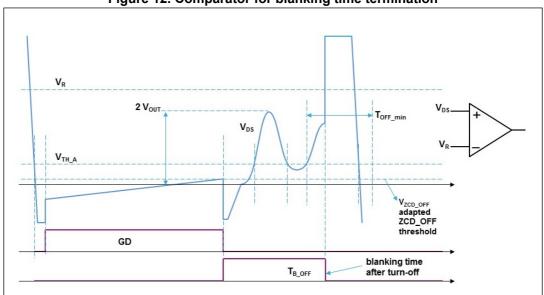

Furthermore, referring to *Figure 12*, an internal comparator referenced to a voltage  $V_R$  higher than 2  $V_{OUT}$  senses the DVS pin voltage (where  $V_R$  and  $V_{DS}$  are conveniently scaled). When the  $V_{DS}$  voltage gets higher than  $V_R$ , the comparator triggers and the blanking time is terminated. This helps during constant voltage regulation operation, at high input voltage levels (where typically the conduction time of the primary MOSFET is short), avoiding that the blanking time determined by  $T_{OFF\_min}$  might delay the SR MOSFET turnon. The internal threshold  $V_R$  is fixed to 2.83  $V_{CC}$  (where  $V_{CC}$  equals  $V_{OUT}$  or  $V_{OUT-VF}$ , depending on whether VAUX functionality is used or not; see *Section 5.8: VAUX pin operation in CC regulation* below).

Figure 12. Comparator for blanking time termination

#### 5.6 Start-up phase

At converter start-up, after the VCC pin voltage has surpassed the turn-on threshold  $V_{CC\_On}$ , the SRK1000 enters the pinstrap phase (lasting 5 switching cycles), where it checks whether a 100 pF capacitor is present on the TON pin or not and internally stores this information as long as  $V_{CC}$  voltage stays above the turn-off threshold  $V_{CC\_Off}$ . After pinstrap, the SRK1000 enters sleep-mode state and, when it detects that the demagnetization time is longer than the programmed sleep-mode exiting threshold (see *Section 5.7: Low consumption mode operation: sleep mode and burst mode* below), finally it enters run mode and starts adapting the turn-off (with the ZCD comparator threshold starting from the minimum level  $V_{ZCD OFF MIN}$ ).

# 5.7 Low consumption mode operation: sleep mode and burst mode

By progressively reducing the load, SR MOSFET conduction time (the transformer demagnetization time) decreases as well: when the conduction time approaches the programmed minimum  $T_{ON}$ , the IC stops switching, reduces its consumption and enters automatic sleep-mode state. The SR MOSFET conduction time to enter sleep mode (measured between the falling and the rising edge of the DVS signal across  $V_{TH}$  A) is:

**Equation 2**

$$T_{ON\_sleep\_in} = T_{ON\_MIN} + 300 \text{ ns}$$

The IC resumes operation when the load is increased and the conduction time of the SR MOSFET body diode becomes a fixed amount longer than the programmed minimum  $T_{ON}$ :

#### **Equation 3**

$$T_{ON \text{ sleep out}} = 1.2 T_{ON \text{ MIN}} + 300 \text{ ns}$$

Both  $T_{ON\_sleep\_in}$  and  $T_{ON\_sleep\_out}$  are measured from the time instant when the DVS signal falls below  $V_{TH\_A}$  and the time instant when it rises above  $V_{TH\_A}$  the first time. The device, once the condition is detected, only takes one cycle to enter/exit sleep-mode operation.

The controller enters low consumption mode also when it detects primary controller burstmode operation, that is, when a switching stop occurs for more than  $T_{stop}$  (i.e.  $V_{DS}$  is sensed higher than  $V_{TH\_A}$  for more than  $T_{stop}$ ). On converter operation resuming, the SRK1000 sleep-out transition takes place after the first negative going edge of the DVS voltage (falling below the threshold  $V_{TH\_A}$ ): in this first cycle, the gate driving is skipped; in the next cycle, the driving signal width equals the programmed minimum  $T_{ON}$ .

It may happen that the SRK1000 enters sleep mode first and then (after further load reduction) it detects primary controller burst-mode operation: in this case, when primary side switching operation restarts, the SRK1000 resumes SR MOSFET driving after it detects the body diode conduction time is larger than the sleep out value  $T_{ON \ sleep \ out}$  for one cycle.

## 5.8 VAUX pin operation in CC regulation

In charger applications operating in CC regulation, the output voltage  $V_{OUT}$  (which is also used to supply the SRK1000) may considerably decrease while output current is kept constant at progressively reduced load impedance. For example, a 10 W charger, set at +5 V output in CV regulation, may be required to operate down to 2 V output while it is regulating the output current to somewhat more than 2 A in CC regulation.

In order to guarantee SR MOSFET switching even with low V<sub>CC</sub> supply voltage, the SRK1000 is provided with the VAUX pin. Referring to the schematic in *Figure 13*, when the V<sub>CC</sub> voltage decreases below the threshold V<sub>CC\_SO\_On</sub> (> V<sub>CC\_Off</sub>), an internal switch is turned on allowing the capacitor C2 placed on the VCC pin to be charged up to the turn-on threshold V<sub>CC\_On</sub> by a current drawn through the VAUX pin.

Figure 13. VAUX supply for CC regulation operation (from rectified SR MOSFET drain)

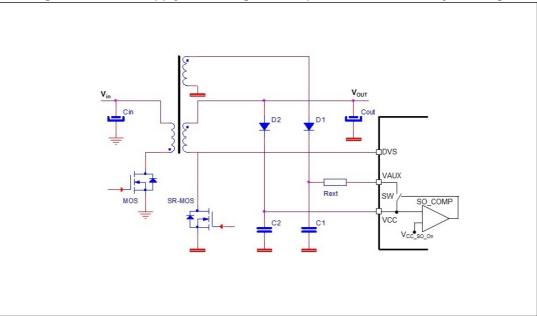

The VAUX pin may be connected, for example, to the rectified SR MOSFET drain voltage, like in *Figure 13* or to another auxiliary voltage of the flyback transformer as shown in *Figure 14*.

In either case, a (Schottky) decoupling diode (D2) is necessary to avoid the VAUX pin charging the output capacitor. An external resistor  $R_{ext}$  may be used in series to the VAUX pin in order to dissipate externally some power amount that, without that resistor, would be totally dissipated inside the SRK1000.

Figure 14. VAUX supply for CC regulation operation from auxiliary winding

Considering the circuit in *Figure 13*, the following exemplification is provided to calculate the value of  $R_{ext}$  resistor and power dissipation, in the case of a +5 V charger with operation

down to 2 V in CC regulation and transformer secondary-to-primary reflected voltage of 75V:

- a) Measure or estimate the IC current consumption during CC regulation operation as below:

- $I_{CC} = I_{q run} + V_{CC} avg C_{iss} F_{sw} = 0.7 \text{ mA} + 4.1 \text{ V} 5 \text{ nF} 50 \text{ kHz} = 1.725 \text{ mA}$

where I<sub>q</sub> is the IC quiescent current, V<sub>CC\_avg</sub> is the average voltage across the VCC pin (mean value between V<sub>CC\_On</sub> and V<sub>CC\_SO\_On</sub>), C<sub>iss</sub> is the SR MOSFET input capacitance and F<sub>sw</sub> is the operating frequency.

b) Calculate the maximum and minimum voltage available at the VAUX pin:

$V_{AUX min} = V_{o.CC} + V_{in.min} (N_S/N_P) - V_F = 2 V + 75 V (1/15) - 0.35 V = 6.65 V$

$$V_{AUX max} = V_{o.CC} + V_{in.max} (N_S/N_P) - V_F = 2 V + 375 V (1/15) - 0.35 V = 26.65 V$$

where  $V_{o.CC}$  is the output voltage in CC regulation,  $V_{in.min} / V_{in.max}$  is the converter minimum/maximum input DC voltage,  $N_S/N_P$  is the transformer turn ratio, and VF is the voltage drop of D1.

c) Calculate the power dissipation of the SRK1000, including device consumption and driving:

$$P_{d CC} = V_{CC avg} I_{CC} = 4.1 V 1.725 mA = 7.072 mW$$

where  $V_{CC avg}$  is the mean value between  $V_{CC On}$  and  $V_{CC SO On}$ .

d) Calculate the maximum external resistance in series to the VAUX pin:

$R_{ext\_MAX}$  = (V\_{AUX\\_min} - V\_CC\_On) / I\_CC - R\_on = (6.65 V - 4.3 V) / 1.725 mA - 40  $\Omega$  = 1.322 k $\Omega$

=>

$$R_{ext}$$

= 1.2 kΩ Rtot = Rext + Ron = 1.2 kΩ +40 Ω = 1.24 kΩ

where Ron is the resistance of the internal VAUX switch.

e) Calculate the maximum and minimum current from the VAUX pin:

$I_{AUX min} = (V_{AUX min} - V_{CC On}) / R_{tot} = (6.65 V - 4.3 V) / 1.24 k\Omega = 1.89 mA$

$I_{AUX max} = (V_{AUX max} - V_{CC On}) / R_{tot} = (26.65 V - 4.3 V) / 1.24 k\Omega = 18.02 mA$

- f) Calculate the maximum power dissipation from VAUX at maximum input voltage (V<sub>in.max</sub>):

- P<sub>d AUX</sub> = V<sub>AUX max</sub> I<sub>CC</sub> = 26.65 V 1.725 mA = 45.971 mW

- g) Calculate the maximum power dissipation on external resistance and inside SRK1000:

$$P_{d\_Rext}$$

= ( $P_{d\_AUX}$  -  $P_{d\_CC}$ )  $R_{ext}$  /  $R_{tot}$  = (45.971 mW - 7.072 mW) 1.2 kΩ / 1.24 kΩ = 37.64 mW

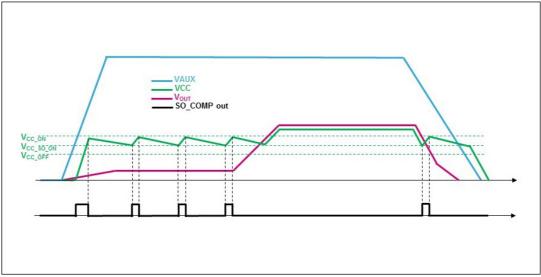

The image in *Figure 15* shows VAUX pin operation during the various circuit phases (startup phase, CC-CV regulation and mains turn-off).

#### 5.9 Operation in CC regulation and short-circuit

During CC regulation operation in QR applications, the demagnetization time progressively increases while reducing the load impedance and the output voltage consequently reduces. Therefore, the conduction duty cycle of SR MOSFET driving increases: the SRK1000 fixes the maximum driving pulse width level to  $T_{ON\_MAX}$  and after this time interval has elapsed, it turns off the SR MOSFET. This means that, for the rest of the demagnetization time after  $T_{ON\_MAX}$ , the rectified current continues to flow through the body diode.

If CC regulation is extended down to short-circuit condition, (i.e. the output current is regulated also during short-circuit and the primary controller does not enter hiccup protection), some care must be taken to avoid temperature increase of the SR MOSFET (i.e. a proper thermal design or the usage of an external Schottky diode).

#### 5.10 Adaptive gate drive

The IC is provided with a low-noise, high-current gate-drive output, capable of directly driving N-channel Power MOSFETs.

The high-level voltage provided by the driver is in fact clamped at  $V_{GDclamp}$  (11.6 V typ.) through an accurate circuitry; this avoids excessive voltage levels on the gate in case the device is supplied with a high  $V_{CC}$ , thus minimizing the gate charge provided in each switching cycle.

Furthermore, the gate driver has a pull-down capability that ensures the SR MOSFET cannot be spuriously turned on even at low  $V_{CC}$ : in fact, the driver has a 1 V (typ.) saturation level at  $V_{CC}$  below the turn-on threshold.

In order to optimize efficiency at low load levels (where driving losses may be relevant with respect to conduction losses), the high-level of driver output is adapted, decreasing with decreasing demagnetization time. The adaptive gate drive changes the driving high-level  $V_{\text{HIGH}}$  in 16 steps of 400 mV, corresponding to 16 steps of detected demagnetization time  $T_{\text{D}}$  of the transformer, as described by the following relationships:

#### Equation 4

$$\Gamma_{\rm D} = 300 \text{ ns} + T_{\rm ON \min} (n+6)/6$$

where  $V_{GD}$  ad step is the voltage step and n (= 1 to 16) is the step number.

The voltage step increase/decrease is done after the demagnetization time interval  $T_D$  has been detected increasing/decreasing by one step for 32 cycles consecutively.

The driver voltage level V<sub>HIGH</sub> is of course limited by the supply voltage on the VCC pin and, in any case, when V<sub>CC</sub> voltage supply is detected lower than a threshold, the driver high-level modulation is disabled. A comparator with hysteresis enables adaptive drive when V<sub>CC</sub> supply increases above V<sub>CC AGD en</sub> and disables it as V<sub>CC</sub> goes below V<sub>CC AGD dis</sub>.

This means that, if the V<sub>CC</sub> supply is low (but higher than V<sub>CC\_AGD\_dis</sub>), the driver high-level V<sub>HIGH</sub> is the minimum between the value of above formula and a value equal to:

- V<sub>CC</sub> supply → if VAUX function is used (and VAUX pin voltage is larger than V<sub>CC</sub> -1.2 V).

- or to V<sub>CC</sub> -1.2 V → if VAUX function is not used; in which case the VAUX pin has to be connected to the VCC pin.

The adaptive gate drive is disabled also when the circuit enters burst-mode operation: at resuming operation from burst mode, the gate drive always starts from the highest voltage level; then it continues progressively adapting it according to the sensed demagnetization period.

In the case of sleep mode, the behavior is different: when the load (after entering sleep mode) increases and the SRK1000 resumes switching operation, the gate drive starts from lower level and then it progressively adapts with step  $V_{GD\_ad\_step}$  according to the sensed demagnetization period.

It is worth noting that, generally speaking, an SR MOSFET is always switched on after current starts flowing through its body diode, when the drain-source voltage is already low (equal to  $V_F$ ); therefore, there is no Miller effect nor switching losses at MOSFET turn-on. This is true also at turn-off, since rectifier current, after SR MOSFET is switched off, continues flowing into the body diode. Consequently, the required gate charge the driver must provide each cycle for ON-OFF switching is rather lower than in the case of hard switching and can be easily found/estimated from the MOSFET datasheet in order to calculate the driver power dissipation.

## 6 Layout guidelines

The GND pin is the return of the bias current of the device and return for gate drive current: it should be routed in the shortest way possible to the common point where the source terminal of the SR MOSFET and output capacitor negative terminal are connected. When laying out the PCB, care must be taken to keep the source terminal of the SR MOSFET as close to output capacitor negative terminal as possible.

DVS connection to SR MOSFET drain terminal is not critical (since adaptive turn-off algorithm automatically compensates for stray inductances in the SR MOSFET current path); nevertheless, it should be preferred to sense the MOSFET voltage as close to its drain terminal as possible.

The usage of bypass capacitors between the VCC pin and GND pin is recommended. They should be low-ESR, low-ESL type and located as close to the IC pins as possible. Sometimes, a series resistor (in the tens ohm) between the converter's output voltage and the VCC pin, forming an RC filter along with the bypass capacitor, is useful to obtain a cleaner  $V_{CC}$  voltage.

Since the TON pin sourced current is relatively low, this pin may be affected by current injections coming from close tracks with high dV/dt (i.e. drain sense signals); therefore, the TON pin should be kept away from SR MOSFET drain tracks, with a proper layout.

In case of large noise, a capacitor can be used on TON pin for filtering; since it is also used for internal timer setting according to user selected operation (quasi-resonant or fixed frequency), the allowed capacitance  $C_{ON}$  is as follows:

max 22pF

➔ for quasi-resonant operation

min 100pF and time constant  $R_{ON} C_{ON} < 100 \ \mu s$

➔ for fixed frequency operation

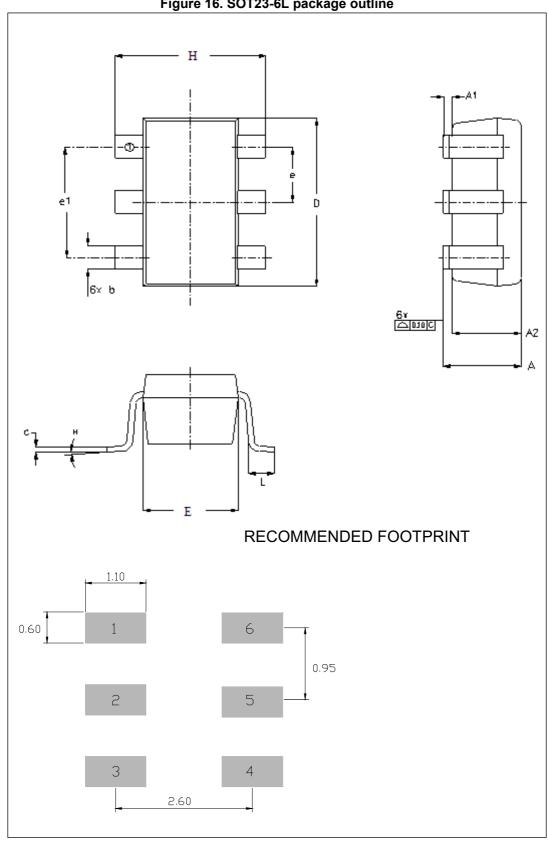

# 7 Package mechanical data

|             | Dimensions |      |      |       |       |       |

|-------------|------------|------|------|-------|-------|-------|

| Dof         |            | mm   |      |       |       |       |

| Ref         | Min.       | Тур. | Max. | Min.  | Тур.  | Max.  |

| А           | 0.90       |      | 1.45 | 0.035 |       | 0.057 |

| A1          | 0.00       |      | 0.15 | 0.000 |       | 0.006 |

| A2          | 0.90       |      | 1.30 | 0.035 |       | 0.051 |

| b           | 0.30       |      | 0.50 | 0.012 |       | 0.020 |

| с           | 0.14       |      | 0.20 | 0.006 |       | 0.009 |

| D           |            | 2.90 |      |       | 0.114 |       |

| E           |            | 1.60 |      |       | 0.063 |       |

| е           |            | 0.95 |      |       | 0.037 |       |

| Н           |            | 2.8  |      |       | 0.110 |       |

| L           | 0.30       |      | 0.60 | 0.012 |       | 0.022 |

| ) (degrees) | 0°         |      | 8°   | 0°    |       | 8°    |

#### Table 6. SOT23-6L mechanical data

Figure 16. SOT23-6L package outline

# 8 Revision history

| Date        | Revision | Changes                                                          |

|-------------|----------|------------------------------------------------------------------|

| 16-Oct-2018 | 1        | Initial release.                                                 |

| 11-Jan-2019 | 2        | Updated Table 1.                                                 |

| 23-Jul-2019 | 3        | Change made to <i>Table 5</i> and text added to <i>Section 6</i> |

Table 7. Document revision history

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics – All rights reserved

DS12787 Rev 3