## S1D13L01 Simple LCDC

# Hardware Functional Specification

Document Number:XA9A-A-001-01

Issue Date: 1/22/15

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2015, All rights reserved.

## **Table of Contents**

| 1.1       Scope       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . </th <th>.7<br/>8<br/>.8<br/>.8<br/>.8<br/>.9<br/>.9<br/>0<br/>0<br/>4</th> | .7<br>8<br>.8<br>.8<br>.8<br>.9<br>.9<br>0<br>0<br>4 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Chapter 2 Features       2.1       Display Resolution       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                                                               | 8<br>.8<br>.8<br>.9<br>.9<br>.9<br>0                 |

| 2.1       Display Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .8<br>.8<br>.9<br>.9<br>.9<br>.9                     |

| 2.2       CPU Interface         2.3       Input Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .8<br>.8<br>.9<br>.9<br>0                            |

| 2.3 Input Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .8<br>.9<br>.9<br>0                                  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8<br>9<br>9<br>0                                     |

| 2.4 Display Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9<br>9<br>0<br>4                                     |

| 2.4 Display Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9<br>0<br>4                                          |

| 2.5 Display Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0<br>4                                               |

| 2.6 Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                    |

| Chapter 3 Typical System Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |

| Chapter 4 Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                    |

| 4.1 Pinout Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .4                                                   |

| 4.2 Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                    |

| 4.2.1 Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                                    |

| 4.2.2 Panel Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                   |

| 4.2.3 Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17                                                   |

| 4.2.4 Miscellaneous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                    |

| 4.2.5 Power And Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                                                    |

| 4.3 Summary of Configuration Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                    |

| 4.4 Host Interface Pin Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20                                                   |

| 4.5 Panel Interface Pin Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                   |

| Chapter 5 Logic Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22                                                   |

| Chapter 6 Embedded Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                                                   |

| 6.1 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                   |

| 6.2 Sample Maximum Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                   |

| Chapter 7 Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                                   |

| 7.1 Clock Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                                   |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                   |

| Chapter 8 D.C. Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                   |

| 8.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27                                                   |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28                                                   |

| Chapter 9 A.C. Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                   |

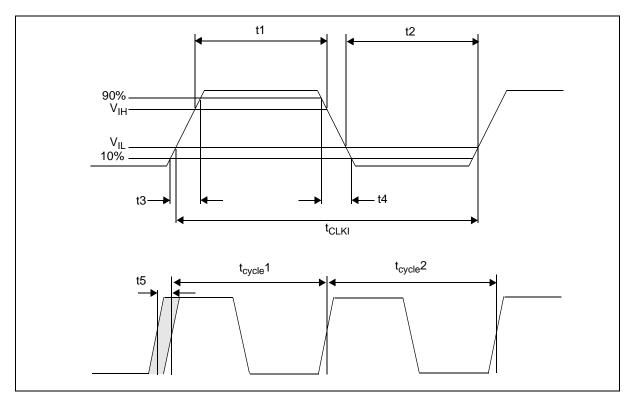

| 9.1 Clock Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                    |

| 9.1.1 Input Clocks                                               | 9  |

|------------------------------------------------------------------|----|

| 9.1.2 PLL Clock                                                  | 1  |

| 9.2 RESET# Timing                                                | 2  |

| 9.3 Power Supply Sequence                                        | 3  |

| 9.3.1 Power-On Sequence                                          | 3  |

| 9.3.2 Power-Off Sequence                                         | 3  |

| 9.4 Host Interface Timing                                        | 4  |

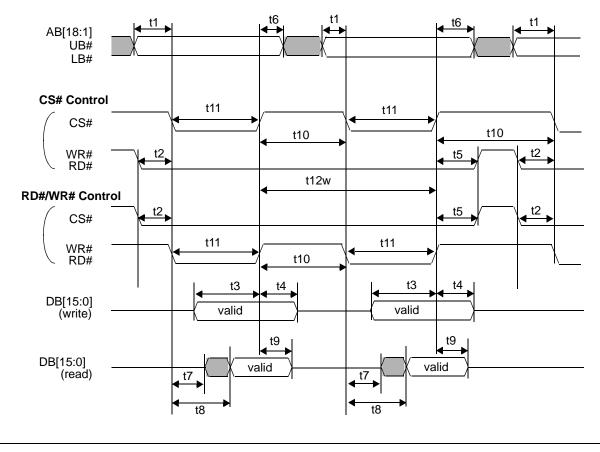

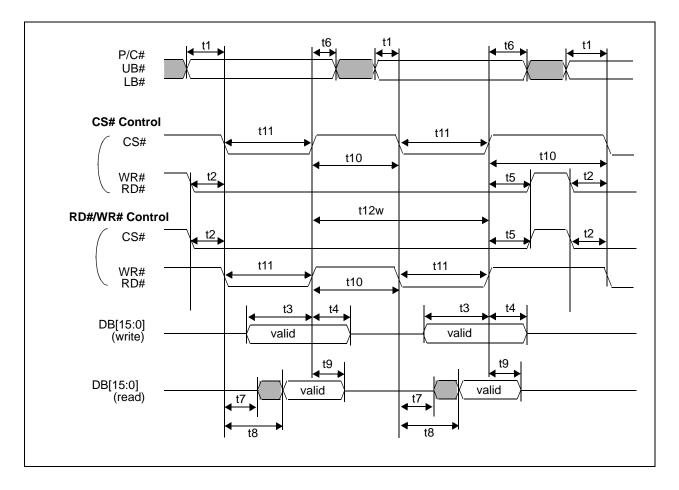

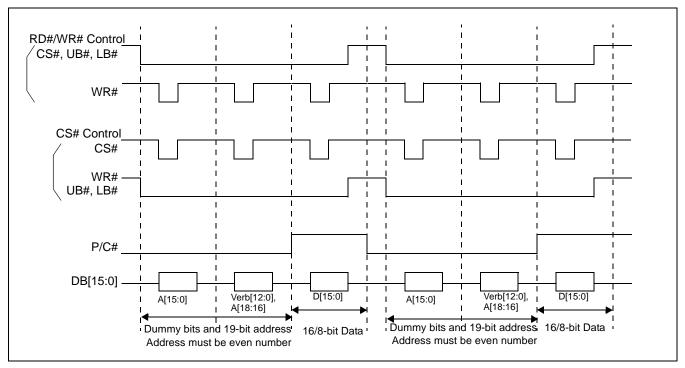

| 9.4.1 Direct 16-bit Mode 1 Timing                                | 4  |

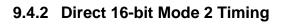

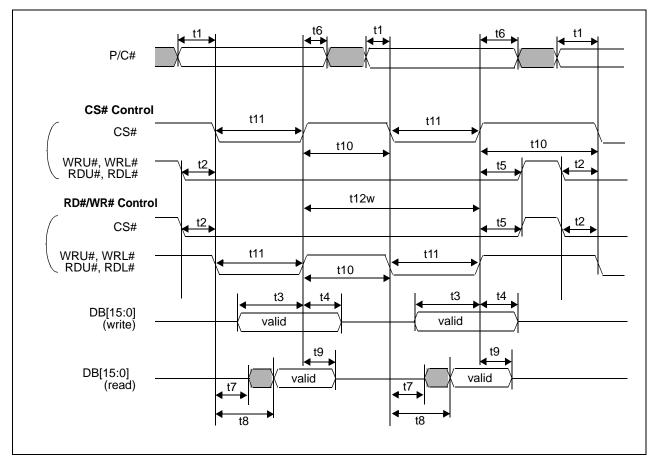

| 9.4.2 Direct 16-bit Mode 2 Timing                                | 6  |

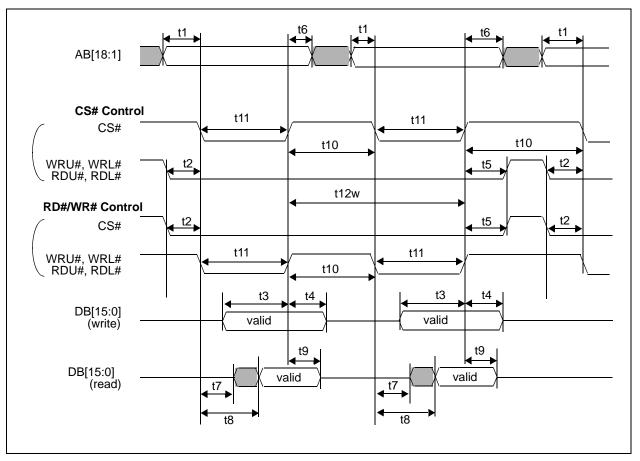

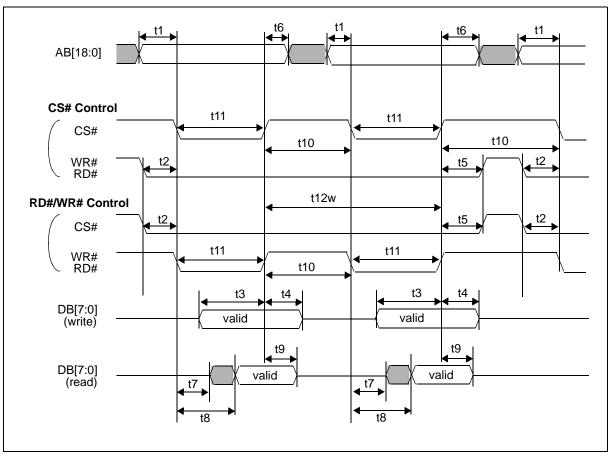

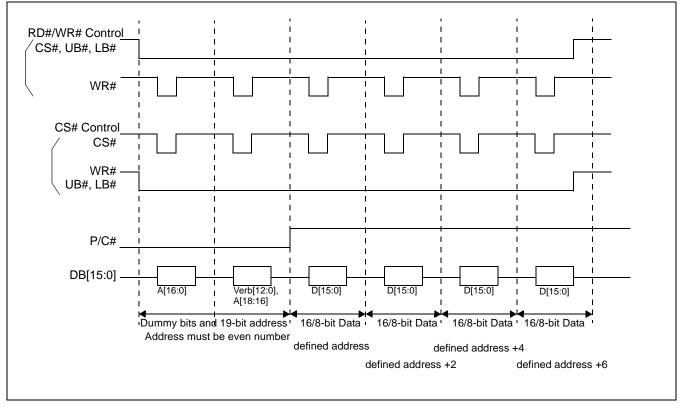

| 9.4.3 Indirect 16-bit Mode 1 Timing                              | 8  |

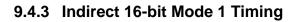

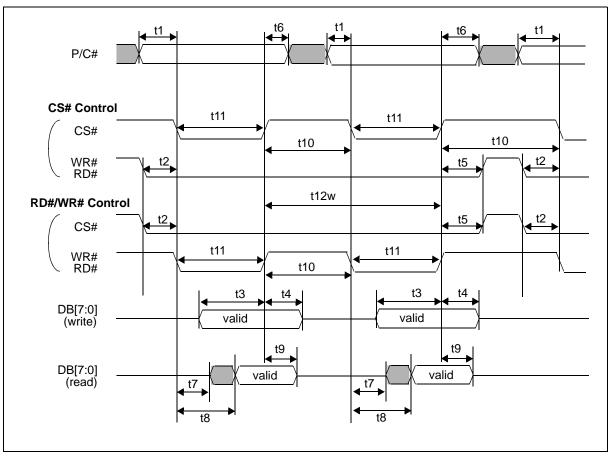

| 9.4.4 Indirect 16-bit Mode 2 Timing                              | 0  |

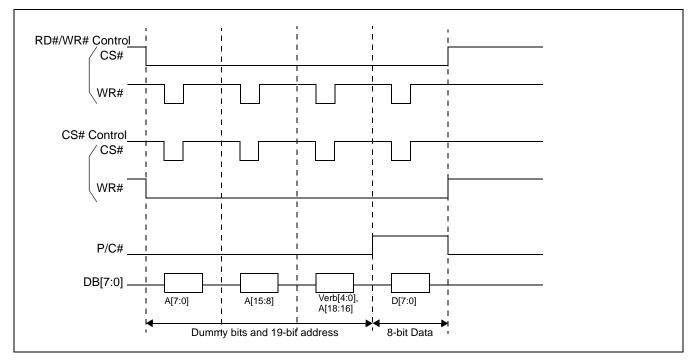

| 9.4.5 Direct 8-bit Timing                                        | .2 |

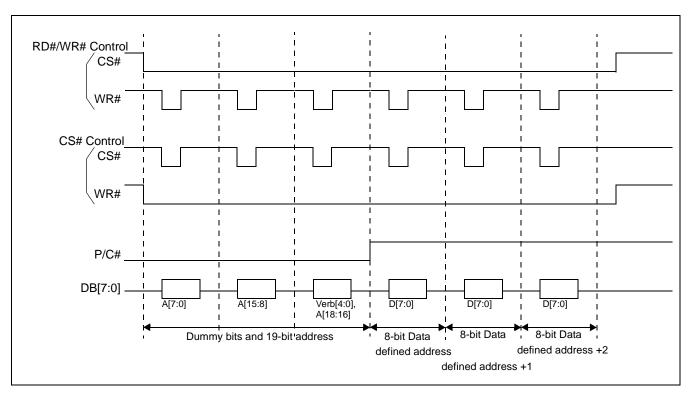

| 9.4.6 Indirect 8-bit Timing                                      | 4  |

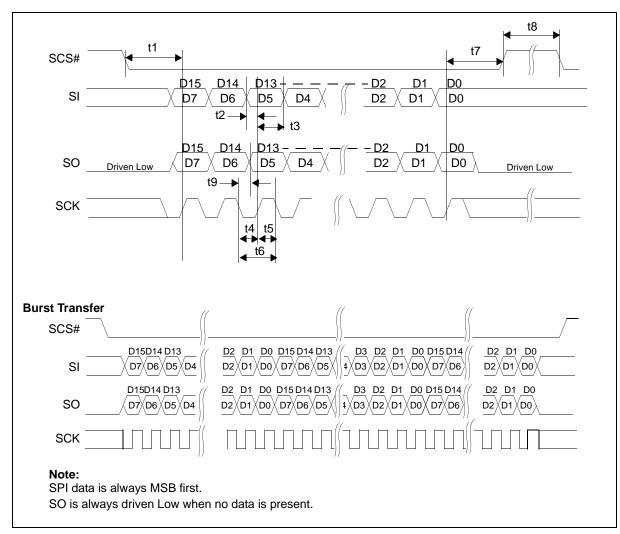

| 9.4.7 SPI Timing                                                 | 6  |

| 9.5 Panel Interface Timing                                       | .8 |

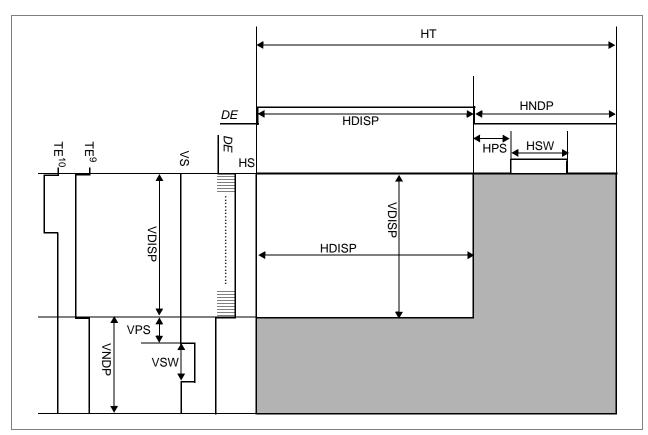

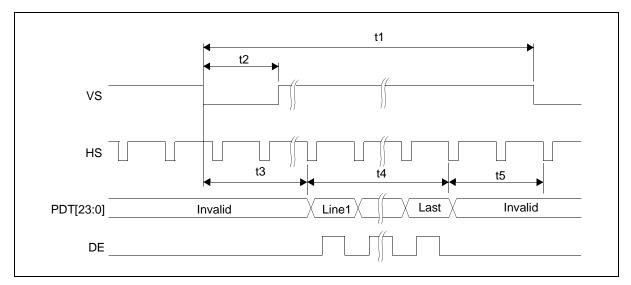

| 9.5.1 General TFT Panel Timing 4                                 | 8  |

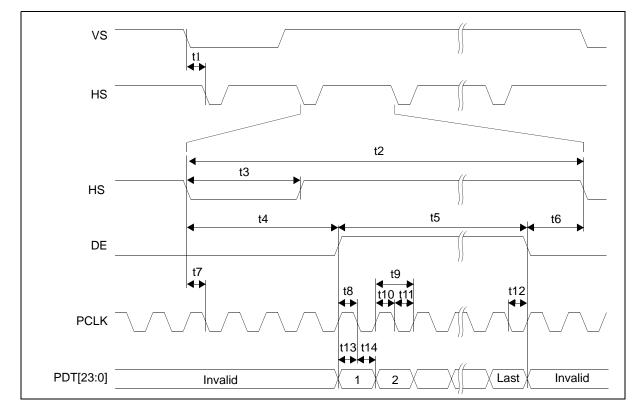

| 9.5.2 TFT 16/18/24-Bit Panel Timing                              | 0  |

| Chapter 10 Registers                                             | 2  |

| 10.1 General                                                     | 2  |

| 10.2 Configuration Registers                                     | 4  |

| 10.3 Clock Configuration Registers                               | 5  |

| 10.4 Panel Configuration Registers                               | 0  |

| 10.5 Layer Configuration Registers                               | 8  |

| 10.6 GPIO Setting Registers                                      | 9  |

| 10.7 Look-Up Table Registers                                     | 0  |

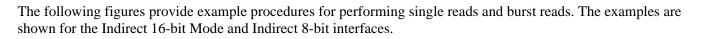

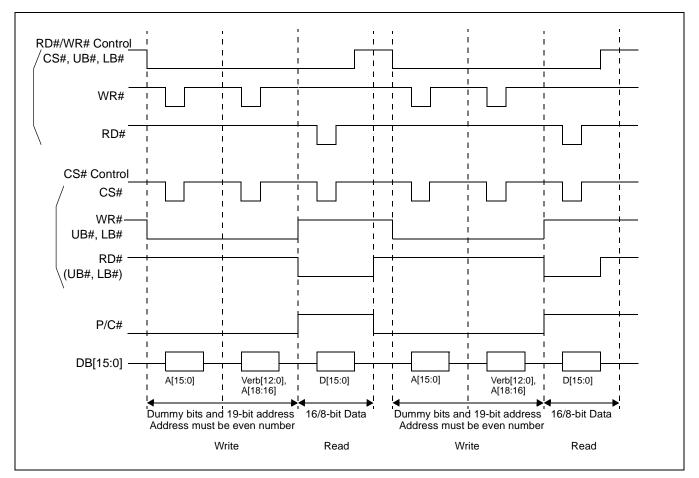

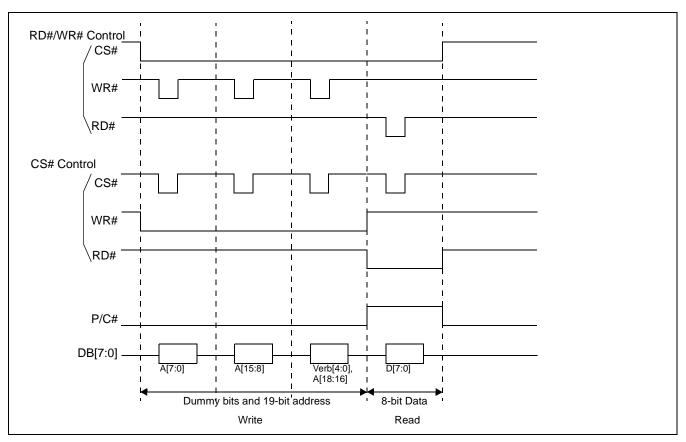

| Chapter 11 Indirect and Serial Host Interface Accessing Sequence | 6  |

| 11.1 Indirect Interface                                          | 6  |

| 11.1.1 Write Procedure                                           | 6  |

| 11.1.2 Read Procedure                                            | 9  |

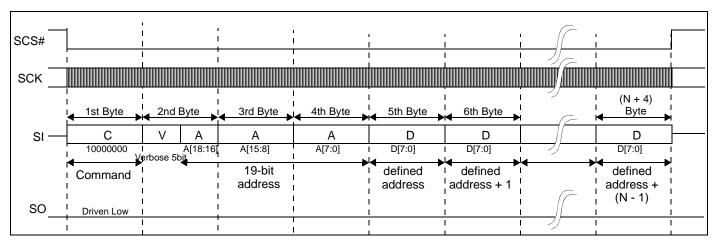

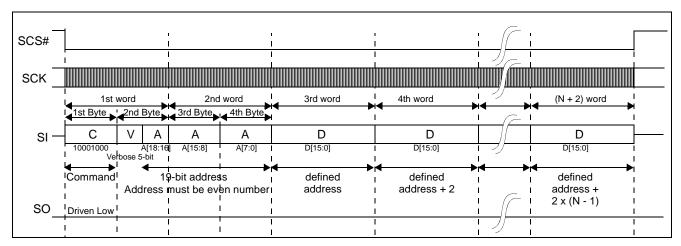

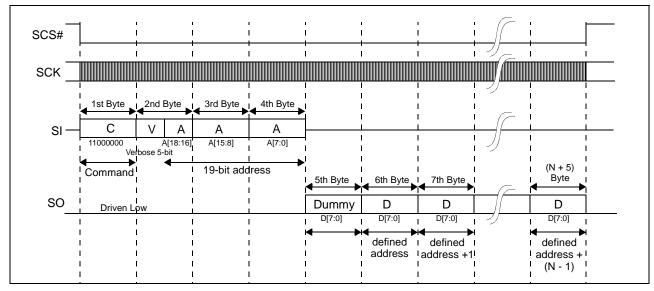

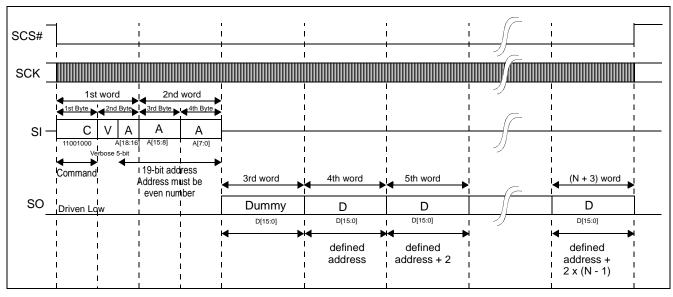

| 11.2 SPI                                                         | 3  |

| 11.2.1 Write Procedure                                           | 94 |

| 11.2.2 Read Procedure                                            | 5  |

| Chapter 12 Image Data Formats                                    | 6  |

| 12.1 Image Data Formats for Host Interface                       |    |

| 12.1.1 RGB 8:8:8 Data Format                                     | 6  |

| 12.1.2 RGB 5:6:5 Data Format                                     |    |

| 12.1.3 24 bpp + LUT Data Format                                  | 8  |

| 12.1.4 16 bpp + LUT Data Format                                  |    |

| 12.1.5 8 bpp + LUT Data Format                                   |    |

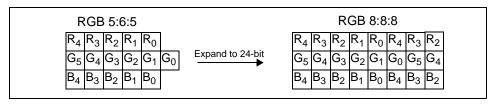

| 12.2 Data Expansion                   |

|---------------------------------------|

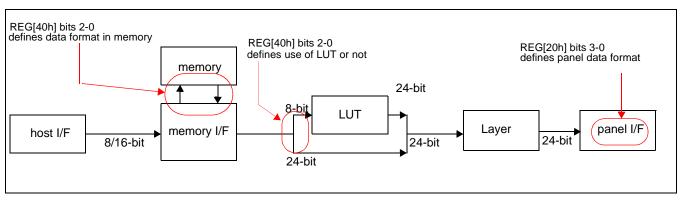

| 12.3 Color Depth                      |

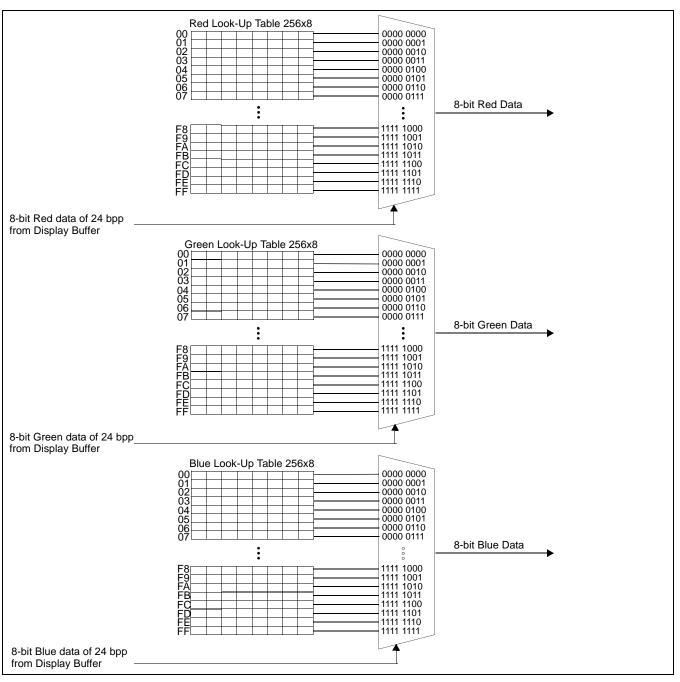

| Chapter 13 Look-Up Table Architecture |

| 13.1 24 bpp LUT                       |

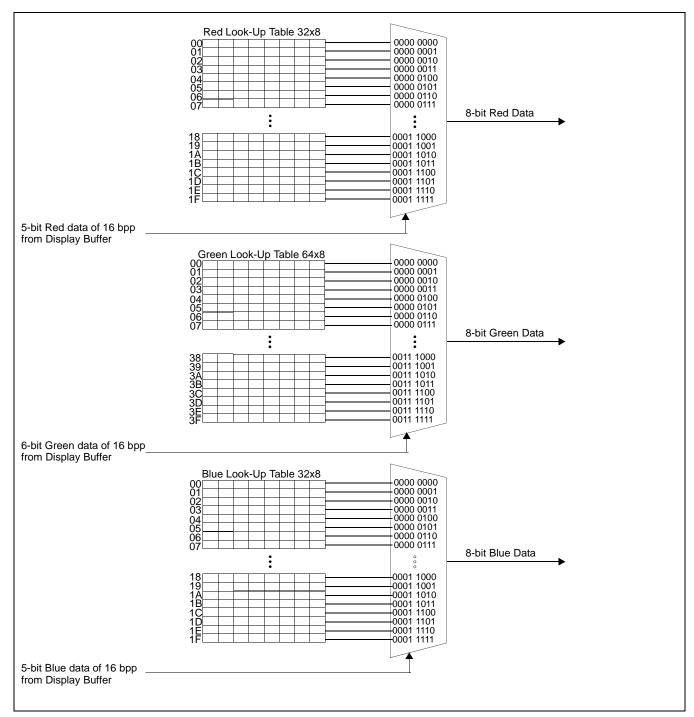

| 13.2 16 bpp LUT                       |

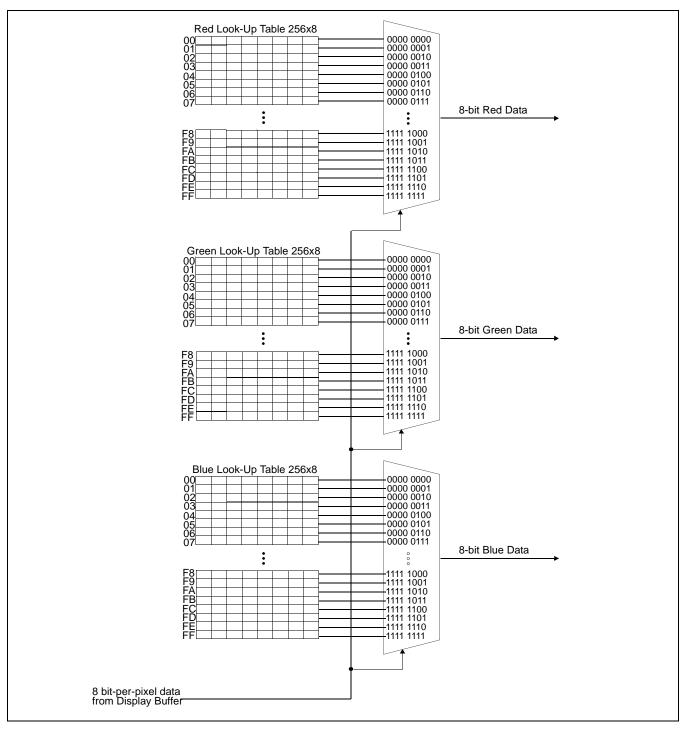

| 13.3 8 bpp LUT in Color Mode          |

| Chapter 14 Display Features           |

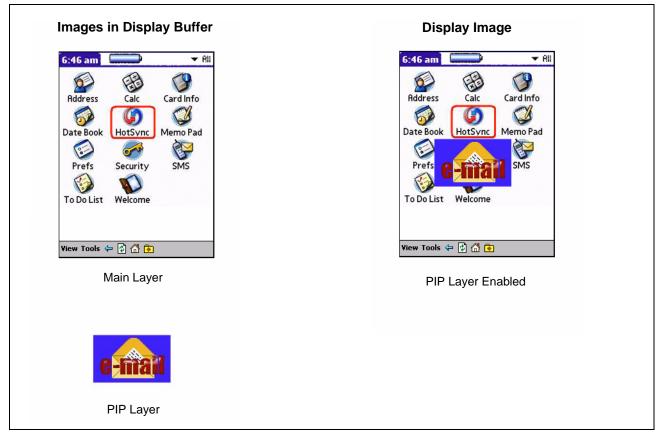

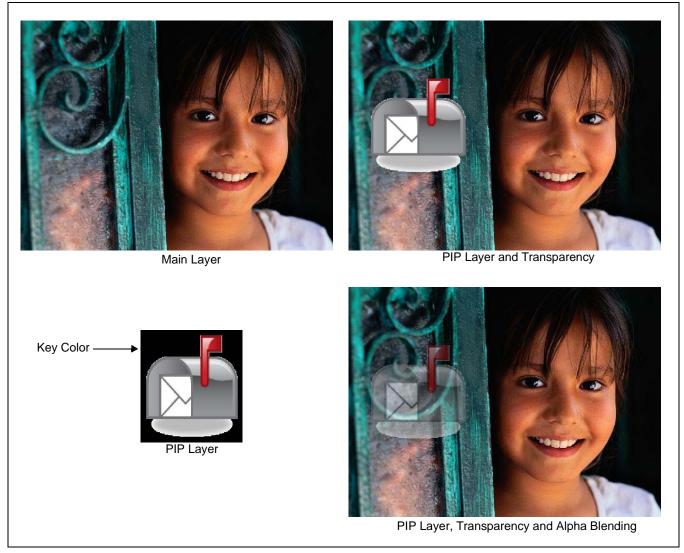

| 14.1 PIP (Picture-in-Picture) Layer   |

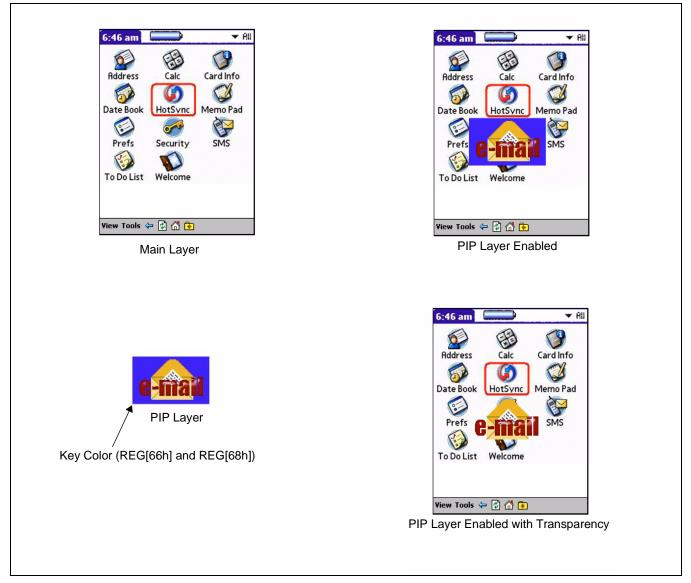

| 14.2 Transparency                     |

| 14.3 Alpha Blending                   |

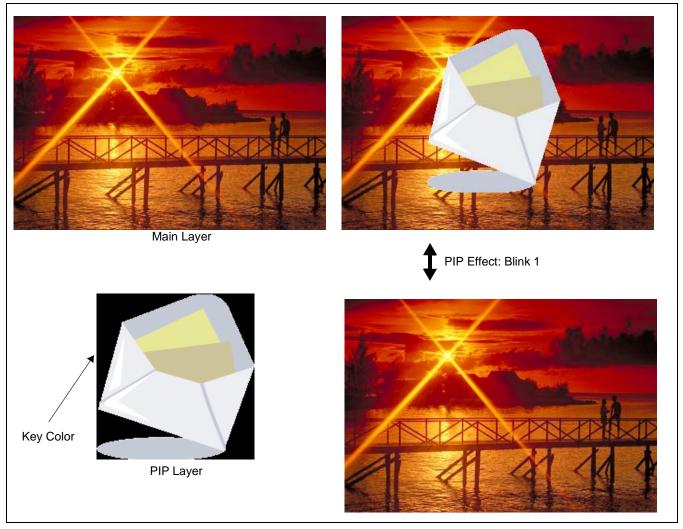

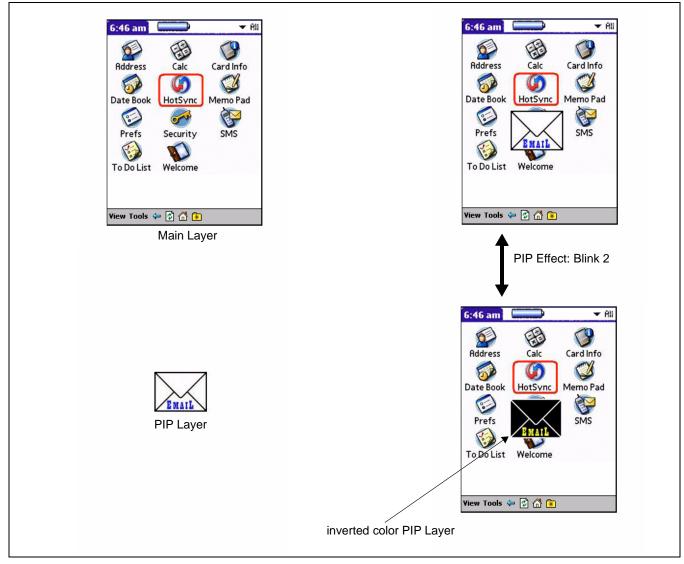

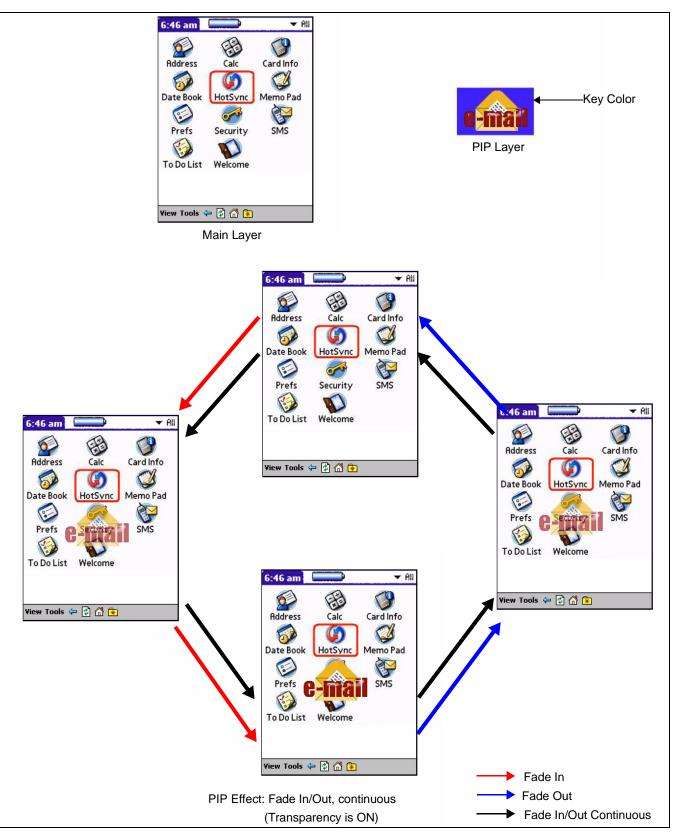

| 14.4 PIP Effects                      |

| 14.4.1 Blinking and Fading Effects    |

| 14.4.2 Blink/Fade Period              |

| 14.4.3 Fade Steps                     |

| 14.4.4 PIP Effect State Transitions   |

| 14.5 Rotation                         |

| 14.5.1 Location Address               |

| 14.5.2 Start Address                  |

| 14.6 Operating Modes                  |

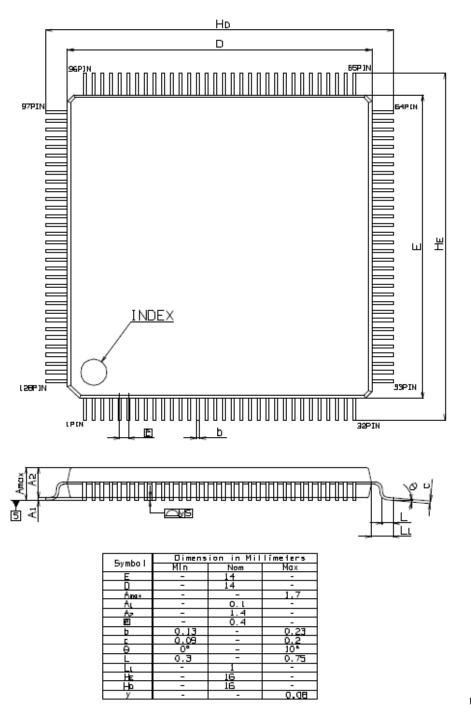

| Chapter 15 Mechanical Data            |

| Chapter 16 Change Record              |

6

## **Chapter 1 Introduction**

## 1.1 Scope

This is the Hardware Functional Specification for the S1D13L01 Series Simple LCD Controller. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at vdc.epson.com.

We appreciate your comments on our documentation. Please contact us via email at documentation@eea.epson.com

## 1.2 Operational Overview

The S1D13L01 is a simple LCD controller with an embedded 384K byte display buffer. The S1D13L01 supports both 8/16-bit direct/indirect CPU interfaces and a SPI CPU interface.

Resolutions supported are up to 480x272 at 24 bpp or 800x480 at 8 bpp for single layer display, or 400x240 at 24 bpp (Main Layer) and 400x240 at 8 bpp (PIP Layer) for two layer display. TFT panels are supported.

The S1D13L01 provides hardware rotation of the display memory transparent to the software application. The S1D13L01 supports both Alpha Blending and Transparency, and with PIP Layer Flashing both preset Blinking and Fade In/Out is achieved with simple register settings. With PIP Layer Flashing the displayed image looks rich, even when used with a low performance CPU.

## **Chapter 2 Features**

## 2.1 Display Resolution

- 384K bytes of embedded VRAM for storing the image data

- Display Resolutions for one layer display (Main Layer Only):

- Up to 480x272 at 24 bpp

- Up to 800x480 at 8 bpp

- Display Resolutions for two layer display (Main and PIP Layer):

- Up to 400x240 at 24 bpp (Main Layer) and 400x240 at 8 bpp (PIP Layer)

## 2.2 CPU Interface

- 8/16-bit Direct interface

- 8/16-bit Indirect interface

- SPI (Mode 0, Mode 3)

## 2.3 Input Data Format

• RGB 8:8:8, RGB 5:6:5, 8 bpp grayscale, or 8/16/24 bpp with Look-Up Table (LUT)

## 2.4 Display Interface

- Active Matrix TFT panels

- 16/18/24-bit

### 2.5 Display Features

- Up to two display layers:

- Main Layer

- 8/16/24 bpp color depths with optional Look-up Table (LUT)

- Independent rotation (0, 90, 180, 270° counter-clockwise)

- PIP Layer

- 8/16/24 bpp color depths with optional Look-up Table (LUT)

- Independent rotation (0, 90, 180, 270° counter-clockwise)

- Configurable PIP Effects allow automatic blink and fade in/out effects

- Alpha Blending

- Transparency

- Look-up Tables for Main and PIP Layers (256 address x 24 bpp)

#### 2.6 Miscellaneous

- Single Clock Input: CLKI

- Embedded PLL

- Software initiated Power Save Modes

- General Purpose IO Pins are available

- Operating Temperature: S1D13L01F00A\*\*\* -40 to 85 °C

- Package:

- QFP15 128-pin (14mm x 14mm x 1.7mm)

## **Chapter 3 Typical System Implementation**

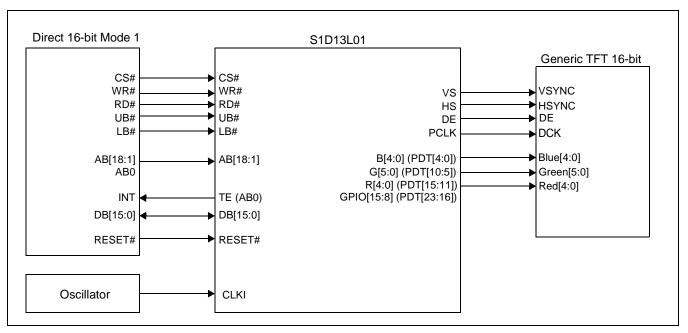

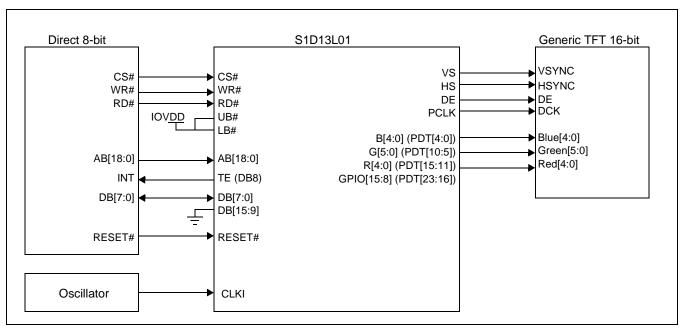

Figure 3-1: Typical System Diagram (Direct 16-bit Mode 1, Panel Generic TFT 16-bit)

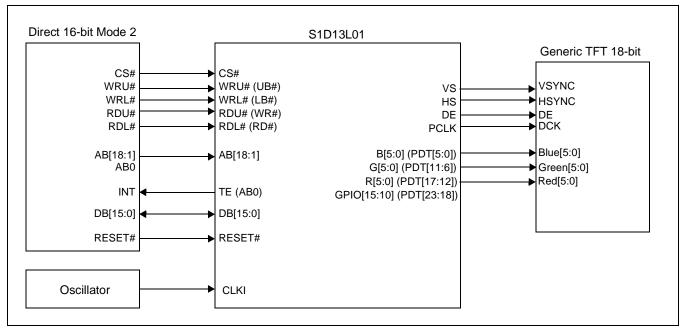

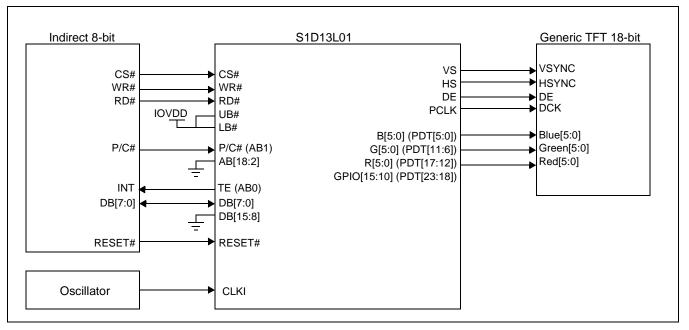

Figure 3-2: Typical System Diagram (Direct 16-bit Mode 2, Generic TFT 18-bit)

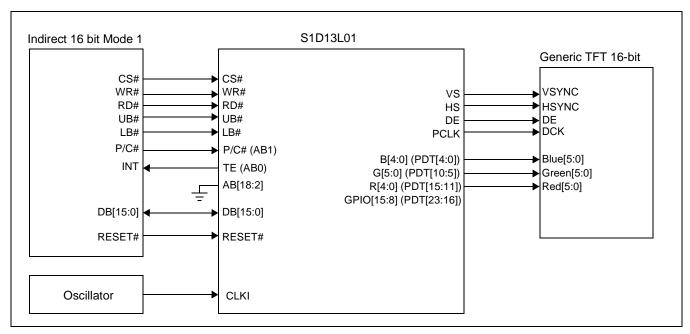

Figure 3-3: Typical System Diagram (Indirect 16-bit Mode 1, Generic TFT 16-bit)

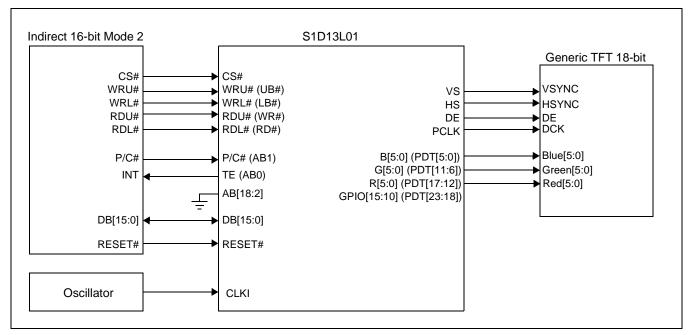

Figure 3-4: Typical System Diagram (Indirect 16-bit Mode 2, Generic TFT 18-bit)

Figure 3-5: Typical System Diagram (Direct 8-bit, Generic TFT 16-bit)

Figure 3-6: Typical System Diagram (Indirect 8-bit, Generic TFT 18-bit)

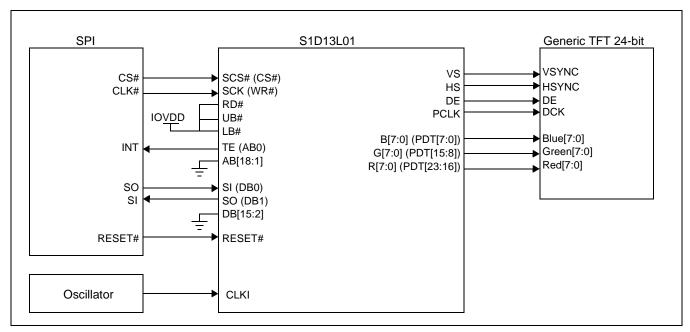

Figure 3-7: Typical System Diagram (SPI, Generic TFT 24-bit)

## Chapter 4 Pins

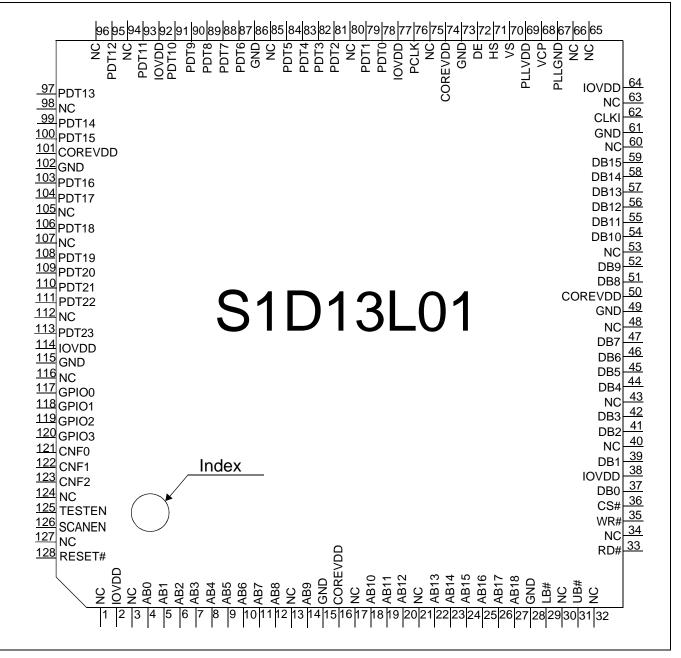

#### 4.1 Pinout Diagram

Figure 4-1 S1D13L01 Pinout Diagram (QFP15-128pin) - Top View

### 4.2 Pin Description

#### Key:

| Pin Types |   |                               |

|-----------|---|-------------------------------|

| I         | = | Input                         |

| 0         | = | Output                        |

| IO        | = | Bi-Directional (Input/Output) |

| Р         | = | Power pin                     |

| AP        | = | Analog Power pin              |

| G         | = | Ground                        |

| AG        | = | Analog Ground                 |

|           |   |                               |

#### **RESET# / Power Save State**

| н    | = | High level output                             |

|------|---|-----------------------------------------------|

| L    | = | Low level output                              |

| Hi-Z | = | High Impedance                                |

| Q    | = | Output Pin, retains output state              |

| QB   | = | IO Pin, if configured as output retains state |

#### Table 4-1: Cell Description

| Item | Description                                                                |

|------|----------------------------------------------------------------------------|

| HIS  | H System LVCMOS Schmitt Input Buffer with Fail Safe                        |

| HISD | H System LVCMOS Schmitt Input Buffer with pull-down resistor and Fail Safe |

| HISU | H System LVCMOS Schmitt Input Buffer with pull-up resistor and Fail Safe   |

| HID  | H System LVCMOS Input Buffer with pull-down resistor and Fail Safe         |

| НО   | H System LVCOMOS Output buffer with Fail Safe                              |

| HB   | H System LVCMOS Bidirectional Buffer with Fail Safe                        |

| HBD  | H System LVCMOS Bidirectional Buffer with pull-down resistor and Fail Safe |

| LIDS | L System <sup>2</sup> LVCMOS Schmitt Input Buffer with pull-down resistor  |

| LITR | L System Transparent Input Buffer                                          |

<sup>1</sup> H System is IOVDD (see Chapter 8, "D.C. Characteristics" on page 27).

<sup>2</sup> L System is COREVDD (see Chapter 8, "D.C. Characteristics" on page 27).

<sup>3</sup> LVCMOS is Low Voltage CMOS (see Chapter 8, "D.C. Characteristics" on page 27).

#### 4.2.1 Host Interface

| Pin Name | Туре | Pin#                        | Cell | Power | Power<br>Save<br>State | RESET#<br>State | Description                                                                                                                                          |

|----------|------|-----------------------------|------|-------|------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#      | Ι    | 36                          | HIS  | IOVDD | —                      | —               | This input pin is the Chip Select signal.                                                                                                            |

| WR#      | I    | 35                          | HIS  | IOVDD |                        |                 | This input pin has multiple functions, WR#, RDU#<br>and SCK. See Section 4.4, "Host Interface Pin<br>Mapping" on page 20 for details.                |

| RD#      | I    | 33                          | HISU | IOVDD | _                      | _               | This input pin has multiple functions, RD# and RDL#.<br>See Section 4.4, "Host Interface Pin Mapping" on<br>page 20 for details.                     |

| UB#      | I    | 31                          | HISU | IOVDD | _                      | _               | This input pin has multiple functions, UB# and WRU#. See Section 4.4, "Host Interface Pin Mapping" on page 20 for details.                           |

| LB#      | I    | 29                          | HISU | IOVDD | _                      | _               | This input pin has multiple functions, LB# and WRL#.<br>See Section 4.4, "Host Interface Pin Mapping" on<br>page 20 for details.                     |

| AB0      | Ю    | 4                           | HB   | IOVDD | QB                     | _               | This bidirectional pin has multiple functions, AB0 and TE. See Section 4.4, "Host Interface Pin Mapping" on page 20 for details.                     |

| AB1      | I    | 5                           | HID  | IOVDD | _                      | _               | This input pin has multiple functions, AB1 and P/C#.<br>See Section 4.4, "Host Interface Pin Mapping" on<br>page 20 for details.                     |

| AB[18:2] | I    | 27~22,<br>20~18,<br>14,12~6 | HID  | IOVDD | _                      | _               | These input pins are the host address bus AB[18:2].<br>See Section 4.4, "Host Interface Pin Mapping" on<br>page 20 for details.                      |

| DB0      | ю    | 37                          | HB   | IOVDD | _                      | _               | This bidirectional pin has multiple functions, host<br>data bus DB0 and SI. See Section 4.4, "Host<br>Interface Pin Mapping" on page 20 for details. |

| DB1      | ю    | 39                          | НВ   | IOVDD | _                      | _               | This bidirectional pin has multiple functions, host<br>data bus DB1 and SO. See Section 4.4, "Host<br>Interface Pin Mapping" on page 20 for details. |

| DB[7:2]  | ю    | 47~44,<br>42~41             | НВ   | IOVDD | _                      | _               | These bidirectional pins are the host data bus<br>DB[7:2]. See Section 4.4, "Host Interface Pin<br>Mapping" on page 20 for details.                  |

| DB8      | ю    | 51                          | HB   | IOVDD | _                      | _               | This bidirectional pin has multiple functions, host<br>data bus DB8 and TE. See Section 4.4, "Host<br>Interface Pin Mapping" on page 20 for details. |

| DB[15:9] | Ю    | 59~54,52                    | HB   | IOVDD | _                      | _               | These bidirectional pins are the host data bus<br>DB[15:9]. See Section 4.4, "Host Interface Pin<br>Mapping" on page 20 for details.                 |

| RESET#   | I    | 128                         | HIS  | IOVDD | _                      |                 | Active low input to set all internal registers to the default state and to force all signals to their inactive states.                               |

Table 4-2: Host Interface Pin Descriptions

#### 4.2.2 Panel Interface

| Pin Name   | Туре | Pin#                                                     | Cell | Power | Power<br>Save<br>State | RESET#<br>State | Description                                                                                                                                                           |

|------------|------|----------------------------------------------------------|------|-------|------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDT[11:0]  | 0    | 93,91~87,<br>84~81,<br>79~78                             | НО   | IOVDD | Q                      | L               | These output pins are the panel data bus<br>PDT[11:0]. See Section 4.5, "Panel Interface Pin<br>Mapping" on page 21 for details.                                      |

| PDT[23:12] | Ю    | 113,<br>111~108,<br>106,<br>104~103,<br>100~99,<br>97,95 | HBD  | IOVDD | QB                     | L               | These bidirectional pins have multiple functions,<br>panel data bus PDT[23:12] and GPIO. See Section<br>4.5, "Panel Interface Pin Mapping" on page 21 for<br>details. |

| VS         | 0    | 70                                                       | НО   | IOVDD | Q                      | L               | This output pin is VS, the panel vertical sync signal.<br>See Section 4.5, "Panel Interface Pin Mapping" on<br>page 21 for details.                                   |

| HS         | 0    | 71                                                       | НО   | IOVDD | Q                      | L               | This output pin is HS, the panel horizontal sync<br>signal. See Section 4.5, "Panel Interface Pin<br>Mapping" on page 21 for details.                                 |

| DE         | 0    | 72                                                       | НО   | IOVDD | Q                      | L               | This output pin has multiple functions, panel data<br>bus enable DE and MOD. See Section 4.5, "Panel<br>Interface Pin Mapping" on page 21 for details.                |

| PDCLK      | 0    | 76                                                       | НО   | IOVDD | Q                      | L               | This output pin is PDCLK, pixel clock for panels.<br>See Section 4.5, "Panel Interface Pin Mapping" on<br>page 21 for details.                                        |

Table 4-3: Panel Interface Pin Descriptions

#### 4.2.3 Clock Input

| Pin Name | Туре | Pin# | Cell | Power | Power<br>Save<br>State | RESET#<br>State | Description                         |

|----------|------|------|------|-------|------------------------|-----------------|-------------------------------------|

| CLKI     | - 1  | 62   | HIS  | IOVDD | —                      | _               | Input clock source for PLL or MCLK. |

Table 4-4: Clock Input Pin Descriptions

#### 4.2.4 Miscellaneous

| Pin Name  | Туре | Pin#                                                                                                                        | Cell | Power   | Power<br>Save<br>State | RESET#<br>State | Description                                                                                                                                                         |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------|------|---------|------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TESTEN    | Ι    | 125                                                                                                                         | LIDS | COREVDD | _                      | _               | Test Enable input used for production test only. This<br>pin must be connected directly to GND for normal<br>operation.                                             |

| SCANEN    | Ι    | 126                                                                                                                         | HISD | IOVDD   | _                      | _               | Scan Enable input used for production test only. This<br>pin must be connected directly to GND for normal<br>operation.                                             |

| VCP       | 0    | 68                                                                                                                          | LITR | PLLVDD  | _                      | _               | This pin is for production test only and should be left unconnected for normal operation.                                                                           |

| CNF[2:0]  | I    | 123~121                                                                                                                     | HIS  | IOVDD   |                        |                 | These inputs are used for power-on configuration.<br>For details, see Table 4-7: "Summary of Power-<br>On/Reset Options (Host Interface Selection)," on<br>page 19. |

|           |      |                                                                                                                             |      |         |                        |                 | <b>Note:</b> These pins must be connected directly to IOVDD or GND.                                                                                                 |

| GPIO[3:0] | Ю    | 120~117                                                                                                                     | HBD  | IOVDD   | QB                     | _               | These pins are a general purpose input/output.<br>Default is input. See Section 10.6, "GPIO Setting<br>Registers" on page 79 for details.                           |

| NC        | _    | 1,3,13,17,<br>21,30,32,<br>34,40,43,<br>48,53,60,<br>63,65,66,<br>75,80,85,<br>94,96,98,<br>105,107,<br>112,116,<br>124,127 | _    | _       | _                      | _               | This pin must be left unconnected.                                                                                                                                  |

Table 4-5: Miscelaneous Pin Descriptions

#### 4.2.5 Power And Ground

| Pin Name | Туре | Pin#                                | Cell | Power | Power<br>Save<br>State | RESET#<br>State | Description       |

|----------|------|-------------------------------------|------|-------|------------------------|-----------------|-------------------|

| IOVDD    | Ρ    | 2, 38, 64<br>77, 92, 114            | Ρ    | _     |                        |                 | IO power supply   |

| COREVDD  | Р    | 16, 50, 74, 101                     | Р    | —     |                        |                 | Core power supply |

| GND      | G    | 15, 28, 49, 61, 73, 86,<br>102, 115 | Р    | _     | _                      | _               | GND for digital   |

| PLLVDD   | AP   | 69                                  | Р    | —     | _                      | —               | PLL Power Supply  |

| PLLGND   | AG   | 67                                  | Р    | —     | _                      |                 | GND for PLL       |

Table 4-6: Power And Ground Pin Descriptions

## 4.3 Summary of Configuration Options

The CNF[2:0] pins are used for Host Interface selection and must be connected directly to IOVDD or GND.

| Configuration | Power-On/Reset State                                                                                                                                                                          |                      |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|

| Input         | 1 (connected to IOVDD)                                                                                                                                                                        | 0 (connected to GND) |  |  |  |  |  |

| CNF[2:0]      | 000: Direct 16-bit mode 1<br>001: Direct 16-bit mode 2<br>010: Indirect 16-bit mode 1<br>011: Indirect 16-bit mode 2<br>100: Direct 8-bit<br>101: Indirect 8-bit<br>110: Reserved<br>111: SPI |                      |  |  |  |  |  |

Table 4-7: Summary of Power-On/Reset Options (Host Interface Selection)

## 4.4 Host Interface Pin Mapping

The S1D13L01 Host interface is selected by setting of the CNF[2:0] pins. For a summary of the Host interface options, see Section 4.3, "Summary of Configuration Options" on page 19.

| S1D13L01<br>Pin Name | Direct 16-bit<br>Mode 1 | Direct 16-bit<br>Mode 2 | Indirect 16-bit<br>Mode 1 | Indirect 16-bit<br>Mode 2 | Direct 8-bit | Indirect 8-bit | SPI  |

|----------------------|-------------------------|-------------------------|---------------------------|---------------------------|--------------|----------------|------|

| CS#                  | CS#                     | CS#                     | CS#                       | CS#                       | CS#          | CS#            | SCS# |

| WR#                  | WR#                     | RDU#                    | WR#                       | RDU#                      | WR#          | WR#            | SCK  |

| RD#                  | RD#                     | RDL#                    | RD#                       | RDL#                      | RD#          | RD#            | Н    |

| UB#                  | UB#                     | WRU#                    | UB#                       | WRU#                      | Н            | Н              | Н    |

| LB#                  | LB#                     | WRL#                    | LB#                       | WRL#                      | Н            | Н              | Н    |

| AB0                  | TE                      | TE                      | TE                        | TE                        | AB0          | TE             | TE   |

| AB1                  | AB1                     | AB1                     | P/C#                      | P/C#                      | AB1          | P/C#           | Low  |

| AB[18:2]             | AB[18:2]                | AB[18:2]                | Low                       | Low                       | AB[18:2]     | Low            | Low  |

| DB0                  | DB0                     | DB0                     | DB0                       | DB0                       | DB0          | DB0            | SI   |

| DB1                  | DB1                     | DB1                     | DB1                       | DB1                       | DB1          | DB1            | SO   |

| DB[7:2]              | DB[7:2]                 | DB[7:2]                 | DB[7:2]                   | DB[7:2]                   | DB[7:2]      | DB[7:2]        | L    |

| DB8                  | DB8                     | DB8                     | DB8                       | DB8                       | TE           | L              | L    |

| DB[15:9]             | DB[15:9]                | DB[15:9]                | DB[15:9]                  | DB[15:9]                  | L            | L              | L    |

Table 4-8: Host Interface Pin Mapping

Where:

H = Connect directly to IOVDD.

L = Connect directly to GND.

Low = Internal pull-down for address bus is active.

TE is defined by REG[22h] bits 6-5.

## 4.5 Panel Interface Pin Mapping

Panel interface mode selection is specified by REG[20h] bits 3-0.

| S1D13L01 |        | Generic TFT | Г      |

|----------|--------|-------------|--------|

| Pin      | 16-bit | 18-bit      | 24-bit |

| VS       | VS     | VS          | VS     |

| HS       | HS     | HS          | HS     |

| DE       | DE     | DE          | DE     |

| PDCLK    | PCLK   | PCLK        | PCLK   |

| PDT0     | B0     | B0          | B0     |

| PDT1     | B1     | B1          | B1     |

| PDT2     | B2     | B2          | B2     |

| PDT3     | B3     | B3          | B3     |

| PDT4     | B4     | B4          | B4     |

| PDT5     | G0     | B5          | B5     |

| PDT6     | G1     | G0          | B6     |

| PDT7     | G2     | G1          | B7     |

| PDT8     | G3     | G2          | G0     |

| PDT9     | G4     | G3          | G1     |

| PDT10    | G5     | G4          | G2     |

| PDT11    | R0     | G5          | G3     |

| PDT12    | R1     | R0          | G4     |

| PDT13    | R2     | R1          | G5     |

| PDT14    | R3     | R2          | G6     |

| PDT15    | R4     | R3          | G7     |

| PDT16    | GPI08  | R4          | R0     |

| PDT17    | GPIO9  | R5          | R1     |

| PDT18    | GPIO10 | GPIO10      | R2     |

| PDT19    | GPIO11 | GPIO11      | R3     |

| PDT20    | GPIO12 | GPIO12      | R4     |

| PDT21    | GPIO13 | GPIO13      | R5     |

| PDT22    | GPIO14 | GPIO14      | R6     |

| PDT23    | GPIO15 | GPIO15      | R7     |

Table 4-9: Panel Interface Pin Mapping

#### Note

When PDT[23:12] are assigned as panel data bus, the internal pull down is inactive. When PDT[23:12] are assigned as GPIO, the internal pull down is controlled by REG[D4h].

## Chapter 5 Logic Diagram

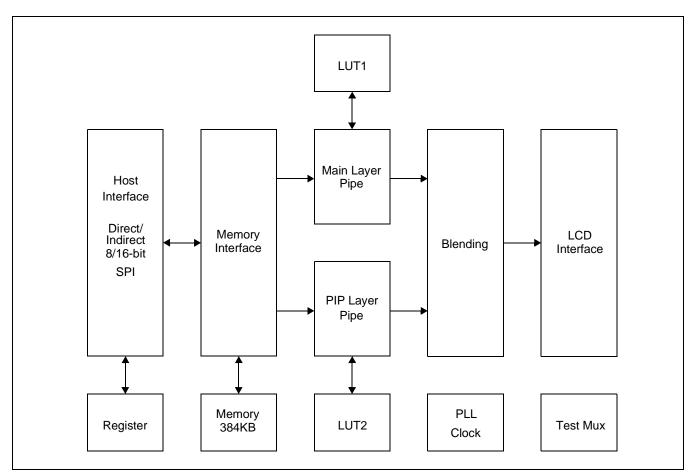

Figure 5-1: Block Diagram

## **Chapter 6 Embedded Memory**

#### 1 Layer Mode 2 Layer Mode 00000h must start 32-bit alignment must start 32-bit alignment Main Layer 384K Bytes Main Layer VRAM must start 32-bit alignment **PIP Layer** 5FFFFh 60000h LUT 1 LUT 1 LUT 1 603FFh 60400h LUT 2 LUT 2 607FFh 60800h Registers Registers Registers 608FFh

### 6.1 Memory Map

Figure 6-1: Memory Construction for Direct Interface

The S1D13L01 has 384K bytes of memory. The VRAM, Registers, and LUT are directly mapped.

### 6.2 Sample Maximum Resolution

When in 1 Layer Mode (PIP Layer off, REG[60h] bits 2-0 = 000b), all 384K bytes of VRAM are assigned for the Main Layer. The Main Layer start address (REG[42h] ~ REG[44h]) must maintain 32-bit alignment. Maximum Main Layer resolutions are shown in the following table.

| Input Data Format | Horizontal | Vertical |

|-------------------|------------|----------|

| RGB 8:8:8         | 480        | 273      |

| RGB 5:6:5         | 480        | 409      |

| 8 bpp + LUT1      | 800        | 491      |

Table 6-1: Maximum Main Layer Resolutions for 1 Layer Mode

When in 2 Layer Mode (PIP Layer on, REG[60h] bits  $2-0 = 001b \sim 111b$ ), the 384K bytes of VRAM are assigned to both the Main Layer and PIP Layer. Both the Main Layer Start Address (REG[42h] ~ REG[44h]) and PIP Layer Start Address (REG[52h] ~ REG[54h]) must maintain 32-bit alignment. maximum combination resolutions for Main and PIP layer are shown in the following table.

| Example | Layer | Input Data Format | Horizontal | Vertical |

|---------|-------|-------------------|------------|----------|

| 1       | Main  | RGB 8:8:8         | 400        | 240      |

| 1       | PIP   | 8 bpp + LUT2      | 400        | 240      |

| 2       | Main  | RGB 8:8:8         | 480        | 240      |

| Z       | PIP   | RGB 5:6:5         | 200        | 110      |

| 3       | Main  | RGB 8:8:8         | 270        | 240      |

| 5       | PIP   | RGB 8:8:8         | 270        | 240      |

Table 6-2: Maximum Combination Resolutions for 2 Layer Mode

## **Chapter 7 Clocks**

## 7.1 Clock Tree

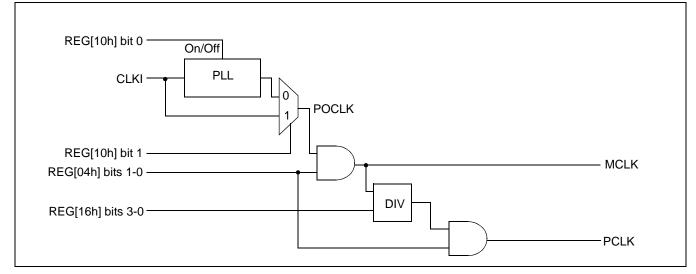

Figure 7-1: Clock Diagram

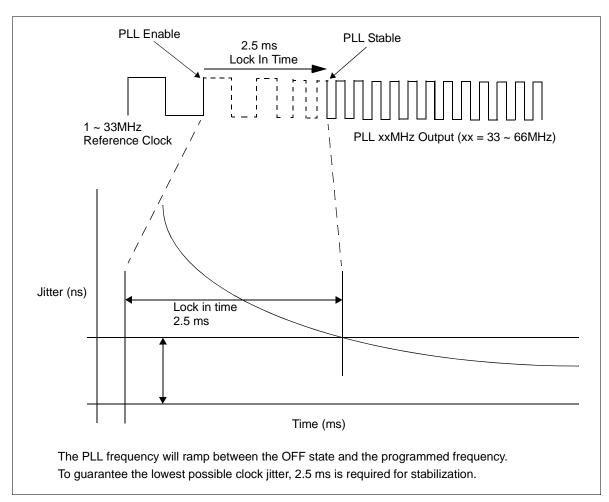

## 7.2 PLL Setting

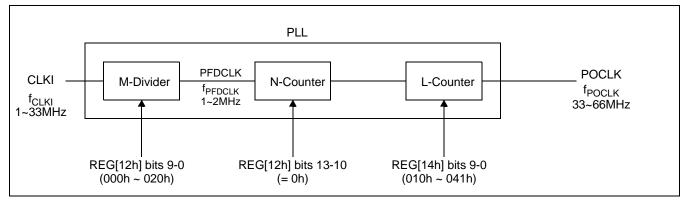

PLL related registers (REG[10h] through REG[14h]) must be set as shown in the following figure.

Figure 7-2: PLL Settings

#### Note

If the S1D13L01 is configured to use the PLL output as the MCLK source and the Host wants to turn off the input clock (CLKI), the Host must disable the PLL (REG[10h] bit 0 = 0b) before shutting off CLKI. This procedure ensures that the PLL Lock bit (REG[10h] bit 15) goes low. Once CLKI has been turned back on, the Host should reenable the PLL.

## 7.3 Clock Setting Minimum Requirement

REG[16h], the Internal Clock Configuration Register, defines the PCLK (Pixel Clock) ratio from MCLK (Memory Clock). When the panel interface block requests more pixel data than the memory interface block can provide, garbage data will be displayed. This means that when the MCLK to PCLK divide ratio is too low (REG[16h] bits 3-0), the memory interface block cannot provide data to the PCLK at the rate set. Panel interface block requirements depend on PIP enable and rotation of both Main and PIP window. Following table shows minimum setting examples for REG[16h].

| Main Window             | Врр       | 8       | 8       | 16      | 16      | 24      | 24      | 24      | 24      |

|-------------------------|-----------|---------|---------|---------|---------|---------|---------|---------|---------|

|                         | Rotation  | 0/180   | 90/270  | 0/180   | 90/270  | 0/180   | 90/270  | 0/180   | 90/270  |

|                         | Hit Ratio | 0.25    | 1.00    | 0.50    | 1.00    | 0.75    | 2.00    | 0.75    | 2.00    |

|                         | Врр       | -       | 8       | 8       | 16      | 8       | 16      | 24      | 24      |

| PIP Window              | Rotation  | -       | 0/180   | 0/180   | 0/180   | 0/180   | 0/180   | 0/180   | 90/270  |

|                         | Hit Ratio | 0.00    | 0.25    | 0.25    | 0.50    | 0.25    | 0.50    | 0.75    | 2.00    |

| Total Hit Ratio         |           | 0.25    | 1.25    | 0.75    | 1.50    | 1.00    | 2.50    | 1.50    | 4.00    |

| REG[16] Minimum Setting |           | 0 (1:1) | 1 (2:1) | 0 (1:1) | 1 (2:1) | 0 (1:1) | 2 (3:1) | 1 (2:1) | 3 (4:1) |

Table 7-1: REG[16] Minimum Setting Examples

#### Note

The above table does not take into account Host accessing. For actual settings, space must be reserved for Host accessing.

## **Chapter 8 D.C. Characteristics**

## 8.1 Absolute Maximum Ratings

| Table 8-1: Absolute Maximum Rat | ings |

|---------------------------------|------|

|---------------------------------|------|

| Symbol               | Parameter              | Rating                   | Units |

|----------------------|------------------------|--------------------------|-------|

| Core V <sub>DD</sub> | Core Supply Voltage    | GND - 0.3 to 2.0         | V     |

| PLL V <sub>DD</sub>  | PLL Supply Voltage     | GND - 0.3 to 2.0         | V     |

| $IO V_{DD}$          | Host IO Supply Voltage | COREVDD to 4.0           | V     |

| V <sub>IN</sub>      | Input Voltage          | GND - 0.3 to IOVDD + 0.3 | V     |

| V <sub>OUT</sub>     | Output Voltage         | GND - 0.3 to IOVDD + 0.3 | V     |

| I <sub>OUT</sub>     | Output Current         | ±10                      | mA    |

## 8.2 Recommended Operating Conditions

| Symbol               | Parameter              | Condition       | Min  | Тур     | Max   | Units |

|----------------------|------------------------|-----------------|------|---------|-------|-------|

| Core V <sub>DD</sub> | Core Supply Voltage    | GND = 0 V       | 1.35 | 1.5     | 1.65  | V     |

| PLL V <sub>DD</sub>  | PLL Supply Voltage     | GND = 0 V       | 1.35 | 1.5     | 1.65  | V     |

| IO V <sub>DD</sub>   | Host IO Supply Voltage | GND = 0 V       | 1.62 | 1.8/3.3 | 3.6   | V     |

| V <sub>IN</sub>      | Input Voltage          | —               | GND  | _       | IOVDD | V     |

| T <sub>OPR</sub>     | Operating Temperature  | S1D13L01F00A*** | -40  | 25      | 85    | °C    |

| T <sub>stg</sub>     | Storage Temperature    | S1D13L01F00A*** | -65  |         | 150   | °C    |

| Table 8-2: Recommended | Operating | Conditions |

|------------------------|-----------|------------|

|------------------------|-----------|------------|

## **8.3 Electrical Characteristics**

The following characteristics are for:  $T_{OPR}$  = -40 to 85 °C (S1D13L01F00A\*\*\*)

| Symbol            | Parameter                 | Condition                     | Min       | Тур | Max       | Units |  |

|-------------------|---------------------------|-------------------------------|-----------|-----|-----------|-------|--|

| I <sub>IZ</sub>   | Input Leakage Current     | —                             | -5        | _   | 5         |       |  |

| I <sub>OZ</sub>   | Off State Leakage Current | —                             | -5        | _   | 5         | μA    |  |

| IOV <sub>OH</sub> | High Level Output Voltage | IOVDD = Min.<br>IOH = -4mA    | IOVDD-0.4 |     | —         | V     |  |

| IOV <sub>OL</sub> | Low Level Output Voltage  | IOVDD = Min.<br>IOL = 4mA     | —         | _   | 0.4       | V     |  |

| V <sub>IH</sub>   | High Level Input Voltage  | LVCMOS Level,<br>IOVDD = Max. | 2.2       | _   | IOVDD+0.3 | V     |  |

| V <sub>IL</sub>   | Low Level Input Voltage   | LVCMOS Level,<br>IOVDD = Min. | -0.3      | _   | 0.8       | V     |  |

| V <sub>T+</sub>   | Positive Trigger Voltage  | LVCMOS Schmitt                | 1.2       | _   | 2.52      | V     |  |

| V <sub>T-</sub>   | Negative Trigger Voltage  | LVCMOS Schmitt                | 0.75      | _   | 1.98      | v     |  |

| $\Delta V$        | Hysteresis Voltage        | LVCMOS Schmitt                | 0.3       | —   | —         | V     |  |

| R <sub>PU</sub>   | Pull-up Resistance        | VI = 0V                       | 20        | 50  | 120       | kΩ    |  |

| R <sub>PD</sub>   | Pull-down Resistance      | VI = IOVDD                    | 20        | 50  | 120       | kΩ    |  |

| C <sub>IO</sub>   | Pin Capacitance           | f = 1MHz, IOVDD =<br>0V       | —         |     | 10        | pF    |  |

| <i>Table 8-3:</i> | IOVDD : | = 3.3V | +0.3V | GND = | = 0V |

|-------------------|---------|--------|-------|-------|------|

| 10010 0 0.        | 10,00   | 0.01   | ,     | 0110  | 0,   |

*Table* 8-4: *IOVDD* =  $1.8V \pm 0.18V$ , *GND* = 0V

| Symbol            | Parameter                 | Condition                     | Min       | Тур | Max       | Units |  |

|-------------------|---------------------------|-------------------------------|-----------|-----|-----------|-------|--|

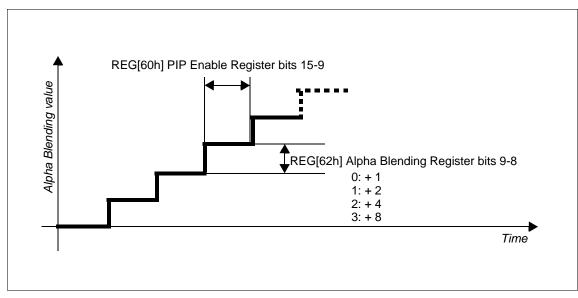

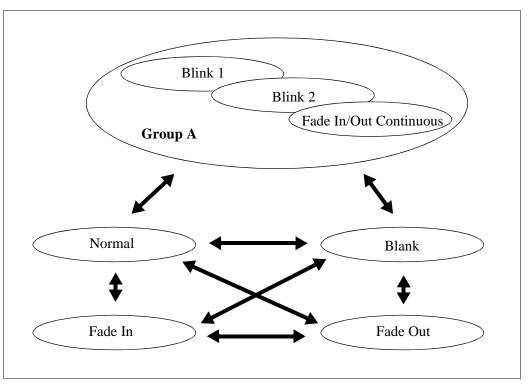

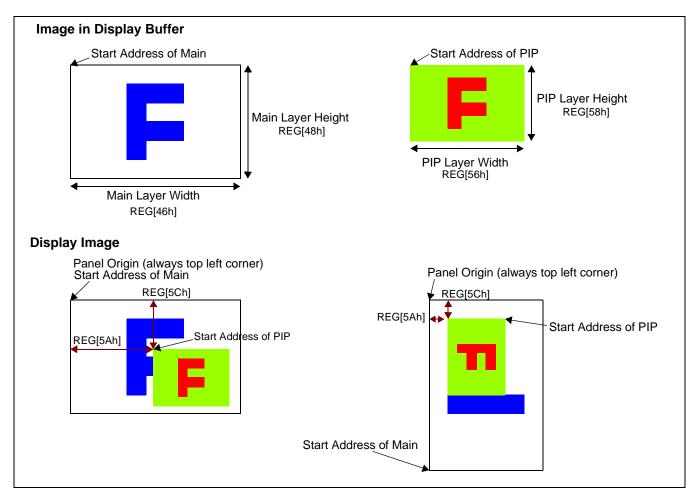

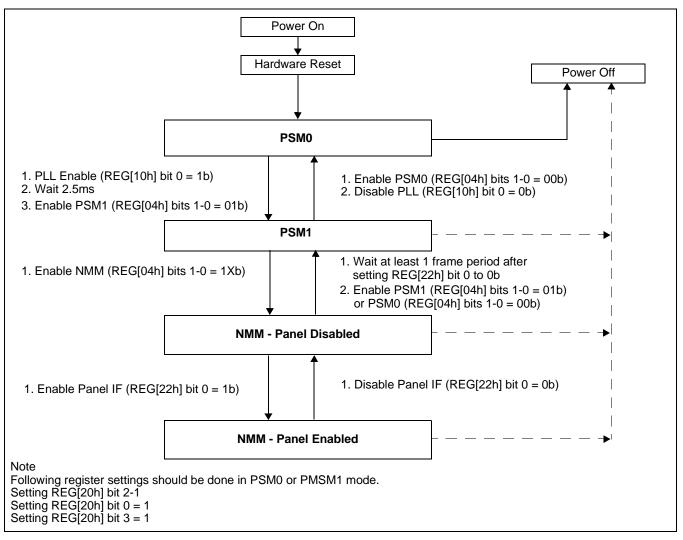

| I <sub>IZ</sub>   | Input Leakage Current     | —                             | -5        | _   | 5         | ۸     |  |