# High Voltage High Current High and Low Side Driver

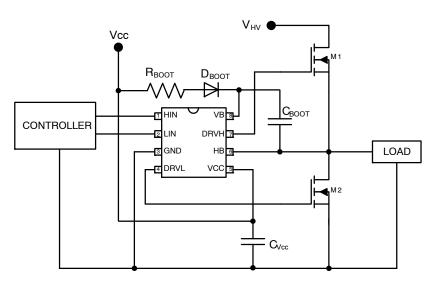

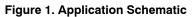

The NCP5183 is a High Voltage High Current Power MOSFET Driver providing two outputs for direct drive of 2 N-channel power MOSFETs arranged in a half-bridge (or any other high-side + low-side) configuration.

It uses the bootstrap technique to insure a proper drive of the High-side power switch. The driver works with 2 independent inputs to accommodate any topology (including half-bridge, asymmetrical half-bridge, active clamp and full-bridge...).

### Features

- Automotive Qualified to AEC Q100

- Voltage Range: up to 600 V

- dV/dt Immunity ±50 V/ns

- Gate Drive Supply Range from 9 V to 18 V

- Output Source / Sink Current Capability 4.3 A / 4.3 A

- 3.3 V and 5 V Input Logic Compatible

- Extended Allowable Negative Bridge Pin Voltage Swing to -10 V

- Matched Propagation Delays between Both Channels

- Propagation Delay 120 ns typically

- Under V<sub>CC</sub> LockOut (UVLO) for Both Channels

- Pin to Pin Compatible with Industry Standards

- These are Pb-free Devices

### **Typical Application**

- Power Supplies for Telecom and Datacom

- Half-Bridge and Full-Bridge Converters

- Push-Pull Converters

- High Voltage Synchronous-Buck Converters

- Motor Controls

- Electric Power Steering

- Class-D Audio Amplifiers

### **ON Semiconductor®**

www.onsemi.com

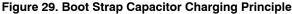

SOIC-8 NB CASE 751-07

### MARKING DIAGRAM

- x = P or V A = Assembly Location

- = Wafer Lot

- = Year

L

Y

W

- = Work Week

- = Pb-Free Package

(Note: Microdot may be in either location)

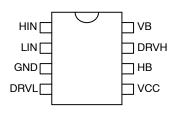

### **PIN CONNECTIONS**

### **ORDERING INFORMATION**

| Device      | Package             | Shipping <sup>†</sup> |

|-------------|---------------------|-----------------------|

| NCP5183DR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape<br>& Reel |

| NCV5183DR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape<br>& Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

| Pin No. (SOIC8) | Pin Name        | Description                                          |

|-----------------|-----------------|------------------------------------------------------|

| 1               | HIN             | High Side Logic Input                                |

| 2               | LIN             | Low Side Logic Input                                 |

| 3               | GND             | Ground                                               |

| 4               | DRVL            | Low Side Gate Drive Output                           |

| 5               | V <sub>CC</sub> | Main Power Supply                                    |

| 6               | HB              | Bootstrap Return or High Side Floating Supply Return |

| 7               | DRVH            | High Side Gate Drive Output                          |

| 8               | VB              | Bootstrap Power Supply                               |

| Table 1  | PIN | FUNCTIO | ON DES | CRIPTION |

|----------|-----|---------|--------|----------|

| Table I. |     |         |        |          |

### **Table 2. ABSOLUTE MAXIMUM RATINGS**

All voltages are referenced to GND pin

| Rating                                                                            | Symbol                              | Value                                      | Units |

|-----------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------|-------|

| Input Voltage Range                                                               | V <sub>CC</sub>                     | -0.3 to 18                                 | V     |

| Input Voltage on LIN and HIN pins                                                 | V <sub>LIN</sub> , V <sub>HIN</sub> | -0.3 to 18                                 | V     |

| High Side Boot pin Voltage                                                        | V <sub>B</sub>                      | (higher of {–0.3 ; $V_{CC}{-}1.5$ ) to 618 | V     |

| High Side Bridge pin Voltage                                                      | V <sub>HB</sub>                     | $V_B$ – 18 to $V_B$ + 0.3                  | V     |

| High Side Floating Voltage                                                        | $V_B - V_{HB}$                      | -0.3 to 18                                 | V     |

| High Side Output Voltage                                                          | V <sub>DRVH</sub>                   | $V_{HB}\!-\!0.3$ to $V_B$ + 0.3            | V     |

| Low Side Output Voltage                                                           | V <sub>DRVL</sub>                   | -0.3 to V <sub>CC</sub> + 0.3              | V     |

| Allowable output slew rate                                                        | dV <sub>HB</sub> /dt                | 50                                         | V/ns  |

| Maximum Operating Junction Temperature                                            | T <sub>J(max)</sub>                 | 150                                        | °C    |

| Storage Temperature Range                                                         | TSTG                                | –55 to 150                                 | °C    |

| ESD Capability, Human Body Model (Note 1)                                         | ESDHBM                              | 3                                          | kV    |

| ESD Capability, Charged Device Model (Note 1)                                     | ESDCDM                              | 1                                          | kV    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 2) | T <sub>SLD</sub>                    | 260                                        | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JÉSD22-A114)

ESD Charged Device Model tested per AEC-Q100-11 (EIA/JESD22-C101E)

Latchup Current Maximum Rating: ≤ 150 mA per JEDEC standard: JESD78 2. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

### **Table 3. THERMAL CHARACTERISTICS**

| Rating                                       | Symbol          | Value | Units |

|----------------------------------------------|-----------------|-------|-------|

| Thermal Characteristics SO8 (Note 3)         |                 |       | °C/W  |

| Thermal Resistance, Junction-to-Air (Note 4) | $R_{\theta JA}$ | 183   |       |

3. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

4. Values based on copper area of 645 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 1 oz copper thickness and FR4 PCB substrate.

#### Table 4. RECOMMENDED OPERATING CONDITIONS (Note 5)

All voltages are referenced to GND pin

| Rating                               | Symbol                              | Min             | Max                 | Units |

|--------------------------------------|-------------------------------------|-----------------|---------------------|-------|

| Input Voltage Range                  | V <sub>CC</sub>                     | 10              | 17                  | V     |

| High Side Floating Voltage           | $V_{B} - V_{HB}$                    | 10              | 17                  | V     |

| High Side Bridge pin Voltage         | V <sub>HB</sub>                     | -1              | 580                 | V     |

| High Side Output Voltage             | V <sub>DRVH</sub>                   | V <sub>HB</sub> | V <sub>B</sub>      | V     |

| Low Side Output Voltage              | V <sub>DRVL</sub>                   | GND             | V <sub>CC</sub>     | V     |

| Input Voltage on LIN and HIN pins    | V <sub>LIN</sub> , V <sub>HIN</sub> | GND             | V <sub>CC</sub> – 2 | V     |

| Operating Junction Temperature Range | TJ                                  | -40             | 125                 | °C    |

5. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

### **Table 5. ELECTRICAL CHARACTERISTICS**

$-40^{\circ}C \le T_J \le 125^{\circ}C$ ,  $V_{CC} = V_B = 15$  V,  $V_{HB} = GND$ , outputs are not loaded, all voltages are referenced to GND; unless otherwise noted. Typical values are at  $T_J = +25^{\circ}C$ . (Notes 6, 7)

| Parameter                                | Test Conditions                                 | Symbol              | Min | Тур | Max | Units |

|------------------------------------------|-------------------------------------------------|---------------------|-----|-----|-----|-------|

| Supply Section                           | •                                               | 1 1                 |     |     | •   |       |

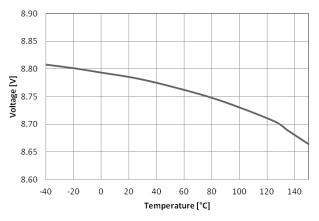

| V <sub>CC</sub> UVLO                     | V <sub>CC</sub> rising                          | V <sub>CCon</sub>   | 7.8 | 8.8 | 9.8 | V     |

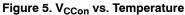

|                                          | V <sub>CC</sub> falling                         | V <sub>CCoff</sub>  | 7.2 | 8.3 | 9.1 | V     |

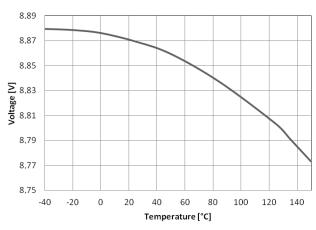

|                                          | V <sub>CC</sub> hysteresis                      | V <sub>CChyst</sub> |     | 0.5 |     | V     |

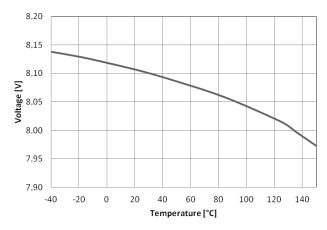

| V <sub>B</sub> UVLO                      | V <sub>B</sub> rising                           | V <sub>Bon</sub>    | 7.8 | 8.8 | 9.8 | V     |

|                                          | V <sub>B</sub> falling                          | V <sub>Boff</sub>   | 7.2 | 8.3 | 9.1 | V     |

|                                          | V <sub>B</sub> hysteresis                       | V <sub>Bhyst</sub>  |     | 0.5 |     | V     |

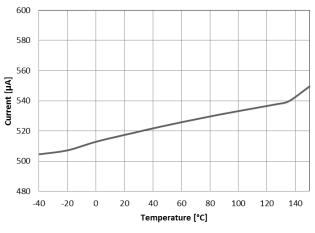

| V <sub>CC</sub> pin operating current    | f = 20 kHz, C <sub>L</sub> = 1 nF               | I <sub>CC1</sub>    |     | 520 | 700 | μA    |

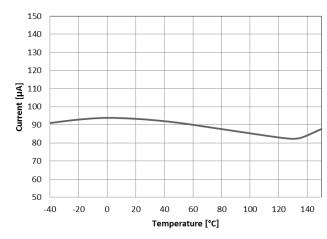

| V <sub>B</sub> pin operating current     | f = 20 kHz, C <sub>L</sub> = 1 nF               | I <sub>B1</sub>     |     | 700 | 800 | μA    |

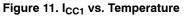

| V <sub>CC</sub> pin quiescent current    | V <sub>LIN</sub> = V <sub>HIN</sub> = 0 V       | I <sub>CC2</sub>    |     | 95  | 160 | μA    |

| V <sub>B</sub> pin quiescent current     | V <sub>LIN</sub> = V <sub>HIN</sub> = 0 V       | I <sub>B2</sub>     |     | 65  | 100 | μA    |

| V <sub>B</sub> to GND quiescent current  | V <sub>B</sub> = V <sub>HB</sub> = 600 V        | I <sub>HSleak</sub> |     |     | 50  | μΑ    |

| Input Section                            | •                                               | 1 1                 |     |     | •   |       |

| Logic High Input Voltage                 |                                                 | V <sub>INH</sub>    | 2.5 |     |     | V     |

| Logic Low Input Voltage                  |                                                 | V <sub>INL</sub>    |     |     | 1.2 | V     |

| Logic High Input Current                 | V <sub>xIN</sub> = 5 V                          | I <sub>xIN+</sub>   |     | 25  | 50  | μA    |

| Logic Low Input Current                  | V <sub>xIN</sub> = 0 V                          | I <sub>xIN-</sub>   |     |     | 1   | μA    |

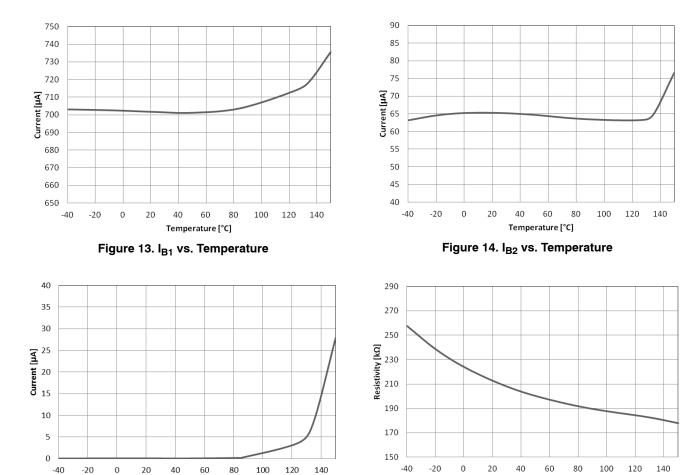

| Input Pull Down Resistance               | V <sub>xIN</sub> = 5 V                          | R <sub>xIN</sub>    | 100 | 250 |     | kΩ    |

| Output Section                           | •                                               |                     |     | •   | •   |       |

| Low Level Output Voltage                 | I <sub>DRVL</sub> = 0 A                         | V <sub>DRVLL</sub>  |     |     | 35  | mV    |

| Low Level Output Voltage (HS Driver)     | I <sub>DRVH</sub> = 0 A                         | V <sub>DRVHL</sub>  |     |     | 35  | mV    |

| High Level Output Voltage                | $I_{DRVL} = 0 A, V_{DRVLH} = V_{CC} - V_{DRVL}$ | V <sub>DRVLH</sub>  |     |     | 35  | mV    |

| High Level Output Voltage (HS Driver)    | $I_{DRVH} = 0 A, V_{DRVHH} = V_B - V_{DRVH}$    | V <sub>DRVHH</sub>  |     |     | 35  | mV    |

| Output Positive Peak current             | V <sub>DRVL</sub> = 0 V, PW = 10 μs             | I <sub>DRVLH</sub>  |     | 4.3 |     | Α     |

| Output Negative Peak current             | V <sub>DRVL</sub> = 15 V, PW = 10 μs            | I <sub>DRVLL</sub>  |     | 4.3 |     | Α     |

| Output Positive Peak current (HS Driver) | $V_{DRVH} = 0 V$ , PW = 10 $\mu$ s              | I <sub>DRVHH</sub>  |     | 4.3 |     | Α     |

| Output Negative Peak current (HS Driver) | V <sub>DRVH</sub> = 15 V, PW = 10 μs            | I <sub>DRVHL</sub>  |     | 4.3 |     | Α     |

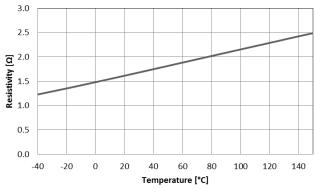

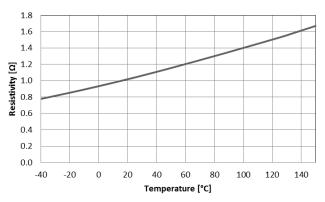

| Output Resistance                        |                                                 | R <sub>OH</sub>     |     | 1.7 |     | Ω     |

| Output Resistance                        |                                                 | R <sub>OL</sub>     |     | 1.1 |     | Ω     |

| Dynamic Section                          |                                                 |                     |     |     |     |       |

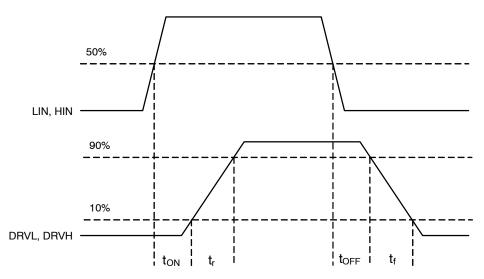

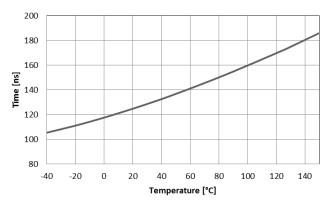

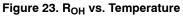

| Turn On Propagation Delay                |                                                 | t <sub>ON</sub>     |     | 120 | 200 | ns    |

| Turn Off Propagation Delay               |                                                 | t <sub>OFF</sub>    |     | 120 | 200 | ns    |

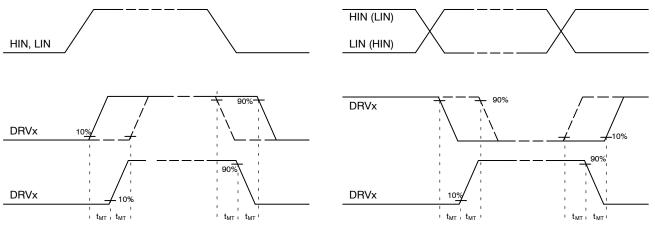

| Delay Matching                           | Pulse width = 1 μs                              | t <sub>MT</sub>     |     | 0   | 50  | ns    |

| Minimum Positive Pulse Width             | $V_{XIN} = 0 V \text{ to } 5 V$                 | t <sub>minH</sub>   |     |     | 150 | ns    |

| Minimum Negative Pulse Width             | $V_{XIN} = 5 V \text{ to } 0 V$                 | t <sub>minL</sub>   |     |     | 100 | ns    |

6. Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area

7. Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at  $T_J = T_A = 25^{\circ}$ C. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible

### **Table 5. ELECTRICAL CHARACTERISTICS**

$-40^{\circ}C \le T_J \le 125^{\circ}C$ ,  $V_{CC} = V_B = 15$  V,  $V_{HB} = GND$ , outputs are not loaded, all voltages are referenced to GND; unless otherwise noted. Typical values are at  $T_J = +25^{\circ}C$ . (Notes 6, 7)

| Parameter                | Test Conditions                              | Symbol             | Min | Тур | Max | Units |

|--------------------------|----------------------------------------------|--------------------|-----|-----|-----|-------|

| Switching Parameters     |                                              |                    |     |     |     |       |

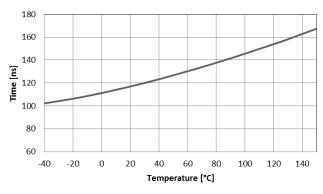

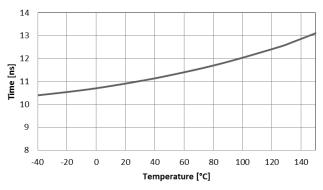

| Output Voltage Rise Time | 10% to 90%, C <sub>L</sub> = 1 nF            | t <sub>r</sub>     |     | 12  | 40  | ns    |

| Output Voltage Fall Time | 90% to 10%, C <sub>L</sub> = 1 nF            | t <sub>f</sub>     |     | 12  | 40  | ns    |

| Negative HB pin Voltage  | $PW \le t_{ON}, V_{CC} = V_B = 10 \text{ V}$ | V <sub>HBneg</sub> |     | -8  | -7  | V     |

6. Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area

Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at T<sub>J</sub> = T<sub>A</sub> = 25°C. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible

Figure 3. Propagation Delay, Rise Time and Fall Time Timing

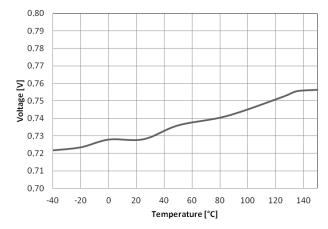

Figure 6. V<sub>CCoff</sub> vs. Temperature

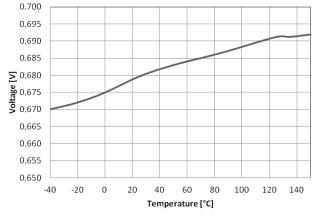

Figure 8. V<sub>Bon</sub> vs. Temperature

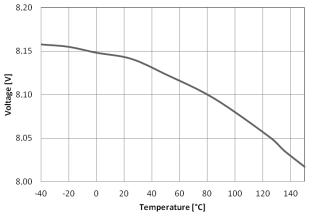

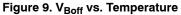

Figure 10. V<sub>Bhyst</sub> vs. Temperature

Figure 7.  $V_{CCUVLOHYS}$  vs. Temperature

Temperature [°C]

Temperature [°C]

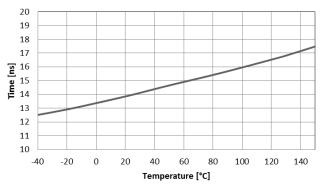

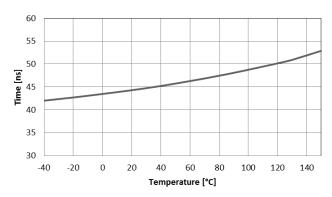

Figure 18. t<sub>OFF</sub> vs. Temperature

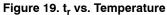

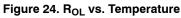

Figure 20. t<sub>f</sub> vs. Temperature

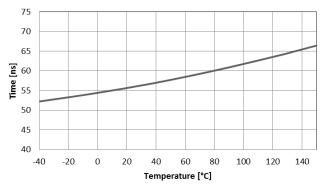

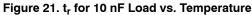

Figure 22. t<sub>f</sub> for 10 nF Load vs. Temperature

Figure 25.  $t_{MT}$  vs. Temperature

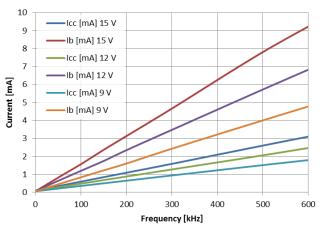

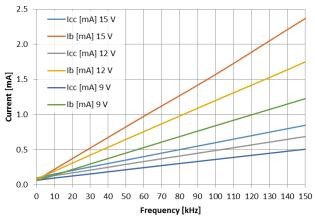

Figure 26.  $I_{CC}$  and  $I_{B}$  Current Consumption vs. Frequency

Detail of  $I_{CC}$  and  $I_B$  Consumption to 150 kHz

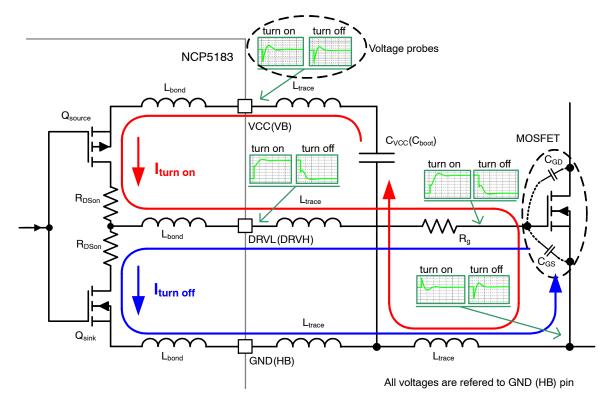

### **MOSFET Turn On and Turn Off Current Path**

A capacitor connected from VCC (VB) to GND (HB) terminal is source of energy for charging the gate terminal of an external MOSFET(s). For better understanding of this process see Figure 27 (all voltages are related to GND (HB) pin). When there is a request from internal logic to turn on the external MOSFET, then the  $Q_{source}$  is turned on. The current starts to flow from  $C_{VCC}$  ( $C_{boot}$ ), through  $Q_{source}$ , gate resistor  $R_g$  to the gate terminal of the external MOSFET (depictured by red line). The current loop is closed from external MOSFET source terminal back to the  $C_{VCC}$  ( $C_{boot}$ ) capacitor. After a while the  $C_{GS}$  capacitance is fully charged so no current flows this path. When the external MOSFET going to be turned off, the internal  $Q_{source}$  is turned off first

and after a short dead time  $Q_{sink}$  is turned on. Then  $C_{VCC}$  ( $C_{boot}$ ) is not a source any more, the source of energy became the  $C_{GS}$  (and all capacitance connected to this terminal, like Muller capacitance). Now the current flows from gate terminal, through  $R_g$  resistor and  $Q_{sink}$  back to the MOSFET (depictured by blue line). In both cases (charging and discharging external MOSFET) there are several parasitic inductances in the path. All of them play a role during switching. In Figure 27 an influence of the inductances in some places is showed. On VCC (VB) pin a drop during turn on and turn off is observed. If too long an UVLO protection can be triggered and the driver can be turned off subsequently, which result in improper operation of the application.

Figure 27. Equivalent Circuit of Power Switch Driver

### Layout Recommendation

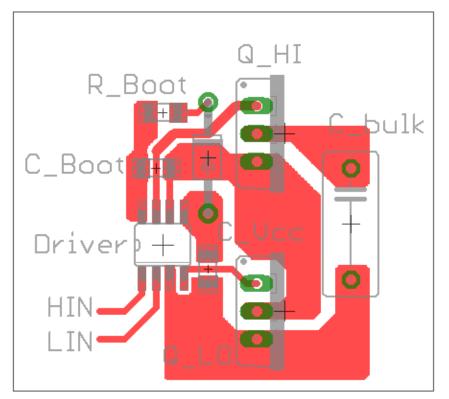

The NCP5183 is high speed, high current (sink/source 4.3 A/4.3 A) driver suitable for high power application. To avoid any damage and/or malfunction during switching (and/or during transients, overloads, shorts etc.) it is very important to avoid a high parasitic inductances in high current paths (see "MOSFET turn on and turn off current path" section). It is recommended to fulfill some rules in layout. One of a possible layout for the IC is depictured in Figure 28.

- Keep loop HB\_pin GND\_pin Q\_LO as small as possible. This loop (parasitic inductance) has potential to increase negative spike on HB pin which can cause of malfunction or damage of HB driver. The negative voltage presented on HB pin is added to  $V_{CC}-V_f$ voltage so  $V_{Cboot}$  is increased. In extreme case the  $C_{boot}$  voltage can be so high it will reach maximum rating value which can lead to device damage.

- Keep loop VDD\_pin GND\_pin C<sub>VCC</sub> as small as possible. The IC featured high current capability driver.

Any parasitic inductance in this path will result in slow Q\_LO turn on and voltage drop on VCC pin which can result in UVLO activation.

- Keep loop VB\_pin HB\_pin C<sub>boot</sub> as small as possible. The IC featured high current capability driver. Any parasitic inductance in this path will result in slow Q\_HI turn on and voltage drop on VB pin which can result in UVLO activation.

- Do not let high current flow through trace between GND\_pin and C<sub>VCC</sub> even a small parasitic inductance here will create high voltage drop if high current flows through this path. This voltage is added or subtracted from HIN and LIN signal, which results in incorrect thresholds or device damaging.

- Keep loops DRVL\_pin Q\_LO GND\_pin and DRVH\_pin – Q\_HI – HB\_pin as small as possible. A high parasitic inductance in these paths will result in slow MOSFET switching and undesired resonance on gate terminal.

Figure 28. Recommended Layout

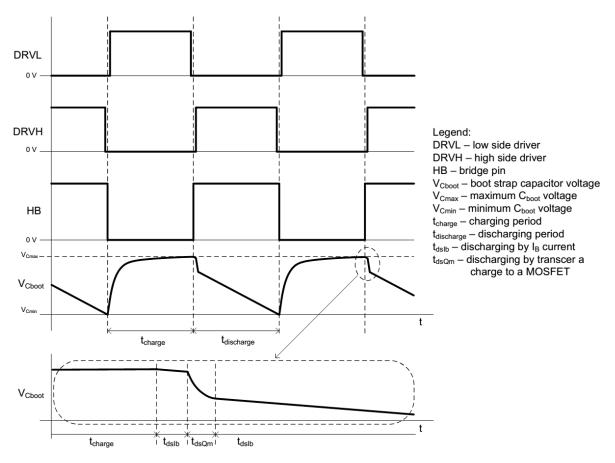

### **C**boot Capacitor Value Calculation

The device featured two independent 4.3 A sink and source drivers. The low side driver (DRVL) supplies a MOSFET whose source is connected to ground. The driver is powered from  $V_{CC}$  line. The high side driver (DRVH) supplies a MOSFET whose source is floating from GND to bulk voltage. The floating driver is powered from  $C_{boot}$  capacitor. The capacitor is charged only when HB pin is pulled to GND (by inductance or the low side MOSFET when turned on). If too small  $C_{boot}$  capacitor is used the high side UVLO protection can disable the high side driver which leads to improper switching.

Expected voltage on  $C_{boot}$  is depictured in Figure 29. The curves are valid for ZVS (Zero Voltage Switching) observed in LLC applications. For hard switch the curves are slightly different, but from charge on  $C_{boot}$  point of view more

favorable. Under the hard switch conditions the energy to charge  $Q_g$  (from zero voltage to  $V_{th}$  of the MOSFET) is taken from  $V_{CC}$  capacitor (through an external boot strap diode) so the voltage drop on  $C_{boot}$  is smaller. For the calculation of  $C_{boot}$  value the ZVS conditions are taken account.

The switching cycle is divided into two parts, the charging ( $t_{charge}$ ) and the discharging ( $t_{discharge}$ ) of the C<sub>boot</sub> capacitor. The discharging can be divided even more to discharging by floating driver current consumption I<sub>B2</sub> ( $t_{dslb}$ ) and to discharging by transfering energy from C<sub>boot</sub> to gate terminal of the MOSFET ( $t_{dsQm}$ ). Discharging by I<sub>B2</sub> becoming more dominant when driver runs at lower frequencies and/or during skip mode operation. To calculate C<sub>boot</sub> value, follow these steps:

- 1. For example, let's have a MOSFET with  $Q_g = 30$  nC,  $V_{DD} = 15$  V.

- 2. Charge stored in  $C_{boot}$  necessary to cover the period the  $C_{boot}$  is not supplied from  $V_{CC}$  line (which is basically the period the high side MOSFET is turned on). Let's say the application is switching at 100 kHz, 50% duty cycle, which means the upper MOSFET is conductive for 5  $\mu$ s. It means the  $C_{boot}$  is discharged by  $I_{B2}$  current

(65  $\mu$ A typ) for 5  $\mu$ s, so the charge consumed by floating driver is:

$$Q_{b} = I_{B2} \cdot t_{discharge} = 65\mu \cdot 5\mu = 325 \text{ pC}$$

(eq. 1)

3. Total charge loss during one switching cycle is sum of charge to supply the high side driver and MOSFET's gate charge:

$$Q_{tot} = Q_g + Q_b = 30n + 325p = 30.3 \text{ nC}$$

(eq. 2)

Let's determine acceptable voltage ripple on C<sub>boot</sub> to 1% of nominal value, which is 150 mV. To cover charge losses from eq. 2

$$C_{boot} = \frac{Q_{tot}}{V_{ripple}} = \frac{30.3n}{0.15} = 202 \text{ nF} \tag{eq. 3}$$

It is recommended to increase the value as consumption and gate charge are temperature and voltage dependent, so let's choose a capacitor 330 nF in this case.

#### **R**boot Resistor Value Calculation

To keep the application running properly, it is necessary to charge the  $C_{boot}$  again. This is done by external diode from  $V_{CC}$  line to VB pin. In serial with the diode a resistor is placed to reduce the current peaks from  $V_{CC}$  line. The resistor value selection is critical for proper function of the high side driver. If too small high current peaks are drown from  $V_{CC}$  line, if too high the capacitor will not be charged to appropriate level and the high side driver can be disabled by internal UVLO protection.

First of all keep in mind the capacitor is charged through the external boot strap diode, so it can be charged to a maximum voltage level of  $V_{CC} - V_f$ . The resistor value is calculated using this equation:

$$\begin{split} \mathsf{R}_{\mathsf{boot}} &= \frac{\mathsf{t}_{\mathsf{charge}}}{\mathsf{C}_{\mathsf{boot}} \cdot \mathsf{ln} \left( \frac{\mathsf{V}_{\mathsf{max}} - \mathsf{V}_{\mathsf{Cmin}}}{\mathsf{V}_{\mathsf{max}} - \mathsf{V}_{\mathsf{Cmax}}} \right)} = \frac{5\mu}{330n \cdot \mathsf{ln} \left( \frac{14.4 - 14.2}{14.4 - 14.35} \right)} \cong \\ &\cong 11 \ \Omega \end{split}$$

Where:

$t_{charge}$  – time period the  $C_{boot}$  is being charged, usually the period the low side MOSFET is turned on

Cboot - boot strap capacitor value

$V_{max}$  – maximum voltage the  $C_{boot}$  capacitor can be theoretically charged to. Usually the  $V_{CC}$  –  $V_f$ . The  $V_f$  is forward voltage of used diode.

V<sub>Cmin</sub>-the voltage level the capacitor is charged from

$V_{Cmax}$ —the voltage level the capacitor is charged to. It is necessary to determine the target voltage for charging, because in theory, when a capacitor is charged from a voltage source through a resistor, the capacitor can never reach the voltage of the source. In this particular case a 50 mV difference (between the voltage behind the diode and  $V_{Cmax}$ ) is used.

The resistor value obtained from eq. 4 does not count with the quiescent current  $I_{B2}$  of the high side driver. This current will create another voltage drop of:

$$V_{IB2\_drop} = R_{boot} \cdot I_{B2} = 11 \cdot 65\mu \approx 0.7 \text{ mV}$$

(eq. 5)

The current consumed by high side driver will be higher, because the  $I_{B2}$  is valid when the device is not switching. While switching, losses by charging and discharging internal transistors as well as the level shifters will be added. This current will increase with frequency.

The additional 0.7 mV drop will be added to  $V_{Cmax}$  value. The additional 0.7 mV drop can be either accepted or the

R<sub>boot</sub> value can be recalculated to eliminate this additional drop.

The resistor  $R_{boot}$  calculated in eq. 4 is valid under steady state conditions. During start and/or skip operation the starting point voltage value is different (lower) and it takes more time to charge the boot strap capacitor. More over it is not counted with temperature and voltage variability during normal operation or the dynamic resistance of the boot strap diode (approximately 0.34  $\Omega$  for MURA160). From these reasons the resistor value should be decreased especially with respect to skip operation.

Boot strap resistor losses calculation.

$$P_{Rboot} \cong Q_{tot} \cdot V_{Cmax} \cdot f = 30.3n \cdot 14.4 \cdot 100k \cong 43.6 \text{ mW}$$

(eq. 6)

Boot strap diode losses calculation.

$$\label{eq:p_bbot} \mathsf{P}_{\mathsf{Dboot}} \cong \mathsf{Q}_{\mathsf{tot}} \cdot \mathsf{V}_{\mathsf{f}} \cdot \mathsf{f} = 30.3 \mathsf{n} \cdot 0.6 \cdot 100 \mathsf{k} \cong 1.8 \ \mathsf{mW} \eqno(\mathsf{eq. 7})$$

Please keep in mind the value is temperature and voltage dependent. Especially  $C_{boot}$  voltage can be higher than calculated value. See "Layout recommendation" section for more details.

#### **Total Power Dissipation**

The NCP5183 is suitable to drive high input capacitance MOSFET, from this reason it is equipped with high current capability drivers. Power dissipation on the die, especially at high frequencies can be limiting factor for using this driver. It is important to not exceed maximum junction temperature (listed in absolute maximum ratings table) in any cases. To calculate approximate power losses follow these steps:

1. Power loss of device (except drivers) while switching at appropriate frequency (see Figure 26) is equal to

$$P_{logic} = P_{HS} + P_{LS} = (V_{boot} \cdot I_{B2SW}) + (V_{CC} \cdot I_{CC2SW}) =$$

= (14.4 \cdot 1.6m) + (15 \cdot 0.6m) \approx 32.1 mW (eq. 8)

2. Power loss of drivers

3. Total power losses

$$P_{total} = P_{logic} + P_{drivers} = 32.1m + 88m \cong 120 \text{ mW}$$

(eq. 10)

4. Junction temperature increase for calculated power loss

$$t_{\rm J} = R_{\rm tJa} \cdot P_{\rm total} = 183 \cdot 0.12 \cong 22 \text{ K}$$

(eq. 11)

The temperature calculated in eq. 11 is the value which has to be added to ambient temperature. In case the ambient temperature is  $30^{\circ}$ C, the junction temperature will be  $52^{\circ}$ C.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                  | 98ASB42564B                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                               |                                                       |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|

| DESCRIPTION:                                                                      | SOIC-8 NB                                                                                   |                                                                                                                                                                                                                                                                                                               | PAGE 1 OF 2                                           |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product or<br>ncidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |  |

© Semiconductor Components Industries, LLC, 2019

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR З. 4. EMITTER EMITTER 5. 6. BASE 7 BASE 8. EMITTER STYLE 5: PIN 1. DRAIN 2. DRAIN З. DRAIN DRAIN 4. 5. GATE 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6. BASE, DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. 4. TXE 5. RXE 6. VFF GND 7. 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 З. CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C З. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. EMITTER, #1 BASE, #2 2. З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 З. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: PIN 1. GROUND BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND BIAS 2 INPUT 6. 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. 5. P-DRAIN 6. P-DRAIN N-DRAIN 7. 8. N-DRAIN STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. 8. CATHODE STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC I/O LINE 3 4. 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt ENABLE З. 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: PIN 1. DRAIN 1 DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

| STYLE 3:<br>PIN 1. DRAIN, DIE #1<br>2. DRAIN, #1<br>3. DRAIN, #2<br>4. DRAIN, #2<br>5. GATE, #2<br>6. SOURCE, #2<br>7. GATE, #1<br>8. SOURCE, #1                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 7:<br>PIN 1. INPUT<br>2. EXTERNAL BYPASS<br>3. THIRD STAGE SOURCE<br>4. GROUND<br>5. DRAIN<br>6. GATE 3<br>7. SECOND STAGE Vd<br>8. FIRST STAGE Vd                    |

| STYLE 11:<br>PIN 1. SOURCE 1<br>2. GATE 1<br>3. SOURCE 2<br>4. GATE 2<br>5. DRAIN 2<br>7. DRAIN 1<br>8. DRAIN 1                                                             |

| STYLE 15:<br>PIN 1. ANODE 1<br>2. ANODE 1<br>3. ANODE 1<br>4. ANODE 1<br>5. CATHODE, COMMON<br>6. CATHODE, COMMON<br>7. CATHODE, COMMON<br>8. CATHODE, COMMON               |

| STYLE 19:<br>PIN 1. SOURCE 1<br>2. GATE 1<br>3. SOURCE 2<br>4. GATE 2<br>5. DRAIN 2<br>6. MIRROR 2<br>7. DRAIN 1<br>8. MIRROR 1                                             |

| STYLE 23:<br>PIN 1. LINE 1 IN<br>2. COMMON ANODE/GND<br>3. COMMON ANODE/GND<br>4. LINE 2 IN<br>5. LINE 2 OUT<br>6. COMMON ANODE/GND<br>7. COMMON ANODE/GND<br>8. LINE 1 OUT |

| STYLE 27:<br>PIN 1. ILIMIT<br>2. OVLO<br>3. UVLO<br>4. INPUT+<br>5. SOURCE<br>6. SOURCE<br>7. SOURCE<br>8. DRAIN                                                            |

#### DATE 16 FEB 2011

STYLE 4: ANODE ANODE PIN 1. 2. ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE, #2 З. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE SOURCE 2. 3. 4. GATE 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER З. COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE CATHODE COLLECTOR/ANODE 6. 7. COLLECTOR/ANODE 8. STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8. VIN

| DOCUMENT NUMBER:                                                                  | 98ASB42564B                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                            |                                                       |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|

| DESCRIPTION:                                                                      | SOIC-8 NB                                                                                   |                                                                                                                                                                                                                                                                                                             | PAGE 2 OF 2                                           |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product o<br>cidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

7.

8

rights of others.

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Onsemi: NCP5183DR2G NCV5183DR2G