**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# **3.3 V ECL 8-Bit Synchronous Binary Up Counter**

# Description

The MC100EP016A is a high-speed synchronous, presettable, cascadeable 8-bit binary counter. Architecture and operation are the same as the ECLinPS<sup>™</sup> family MC100E016 with higher operating speed.

The counter features internal feedback to  $\overline{\text{TC}}$  gated by the TCLD (Terminal Count Load) pin. When TCLD is LOW (or left open, in which case it is pulled LOW by the internal pulldowns), the  $\overline{\text{TC}}$  feedback is disabled, and counting proceeds continuously, with  $\overline{\text{TC}}$  going LOW to indicate an all-one state. When TCLD is HIGH, the TC feedback causes the counter to automatically reload upon TC = LOW, thus functioning as a programmable counter. The Qn outputs do not need to be terminated for the count function to operate properly. To minimize noise and power, unused Q outputs should be left unterminated.

COUT and  $\overline{\text{COUT}}$  provide differential outputs from a single, non-cascaded counter or divider application. COUT and  $\overline{\text{COUT}}$  should not be used in cascade configuration. Only  $\overline{\text{TC}}$  should be used for a counter or divider cascade chain output.

A differential clock input has also been added to improve performance.

The 100 Series contains temperature compensation.

#### Features

- 550 ps Typical Propagation Delay

- Operation Frequency > 1.3 GHz is 30% Faster than MC100EP016

- PECL Mode Operating Range: V<sub>CC</sub> = 3.0 V to 3.6 V with V<sub>EE</sub> = 0 V

- NECL Mode Operating Range: V<sub>CC</sub> = 0 V with V<sub>EE</sub> = -3.0 V to -3.6 V

- Open Input Default State

- Safety Clamp on Clock Inputs

- Internal  $\overline{\text{TC}}$  Feedback (Gated)

- Addition of COUT and COUT

- 8-Bit

- Differential Clock Input

- V<sub>BB</sub> Output

- Fully Synchronous Counting and TC Generation

- Asynchronous Master Reset

- Pb-Free Packages are Available

# **ON Semiconductor®**

http://onsemi.com

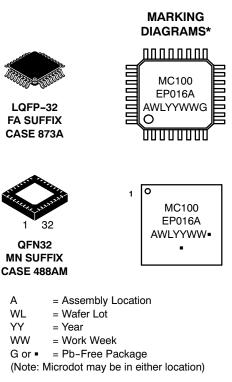

\*For additional marking information, refer to Application Note AND8002/D.

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.

1

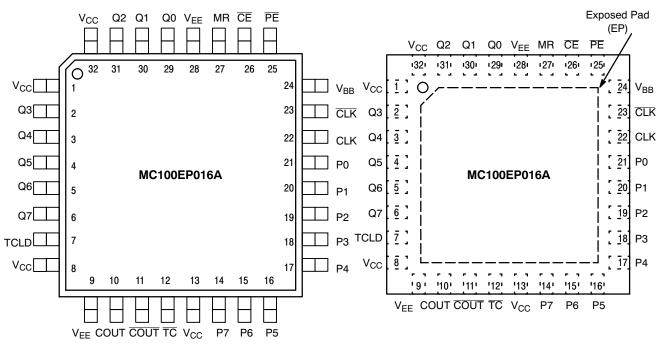

Warning: All  $V_{CC}$  and  $V_{EE}$  pins must be externally connected to Power Supply to guarantee proper operation.

Figure 1. 32-Lead LQFP Pinout (Top View)

Figure 2. 32-Lead QFN Pinout (Top View)

# Table 1. PIN DESCRIPTION

| Pin             | Function                                                                                                                                                                      |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0-P7           | ECL Parallel Data (Preset) Inputs                                                                                                                                             |

| Q0-Q7           | ECL Data Outputs                                                                                                                                                              |

| CE*             | ECL Count Enable Control Input                                                                                                                                                |

| PE*             | ECL Parallel Load Enable Control Input                                                                                                                                        |

| MR*             | ECL Master Reset                                                                                                                                                              |

| CLK*, CLK*      | ECL Differential Clock                                                                                                                                                        |

| TC              | ECL Terminal Count Output                                                                                                                                                     |

| TCLD*           | ECL TC-Load Control Input                                                                                                                                                     |

| COUT, COUT      | ECL Differential Output                                                                                                                                                       |

| V <sub>CC</sub> | Positive Supply                                                                                                                                                               |

| V <sub>EE</sub> | Negative Supply                                                                                                                                                               |

| V <sub>BB</sub> | Reference Voltage Output                                                                                                                                                      |

| EP              | The exposed pad (EP) on the QFN-32 package bottom is thermally connected to the die for improved heat-sinking conduit. The pad is electrically connected to $V_{\text{EE}}$ . |

\*Pins will default LOW when left open.

# Table 2. FUNCTION TABLE

| CE | PE | TCLD | MR | CLK | FUNCTION                                      |

|----|----|------|----|-----|-----------------------------------------------|

| Х  | L  | Х    | L  | Z   | Load Parallel (Pn to Qn)                      |

| L  | Н  | L    | L  | Z   | Continuous Count                              |

| L  | Н  | Н    | L  | Z   | Count; Load Parallel on $\overline{TC}$ = LOW |

| Н  | Н  | Х    | L  | Z   | Hold                                          |

| Х  | Х  | Х    | L  | ZZ  | Masters Respond, Slaves Hold                  |

| х  | х  | Х    | н  | Х   | Reset (Qn : = LOW, TC : = HIGH)               |

ZZ = Clock Pulse (High-to-Low) Z = Clock Pulse (Low-to-High)

# Table 3. FUNCTION TABLE

| Function                     | PE          | CE                    | MR               | TCLD             | CLK                        | P7-P4       | P3                    | P2                    | P1                    | P0                    | Q7-Q4       | Q3          | Q2          | Q1                    | Q0                         | тс          | COUT             | COUT        |

|------------------------------|-------------|-----------------------|------------------|------------------|----------------------------|-------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------|-------------|-------------|-----------------------|----------------------------|-------------|------------------|-------------|

| Load Count                   | LHHHH       | X<br>L<br>L<br>L<br>L | L<br>L<br>L<br>L | X<br>L<br>L<br>L | Z<br>Z<br>Z<br>Z<br>Z      | H X X X X   | H<br>X<br>X<br>X<br>X | H<br>X<br>X<br>X<br>X | L<br>X<br>X<br>X<br>X | L<br>X<br>X<br>X<br>X | H H H H L   | H H H L     | H H H H L   | L<br>L<br>H<br>H<br>L | L<br>H<br>L<br>H<br>L      | ΗΗΗ         | H<br>H<br>L<br>H | LLLL        |

| Load Hold                    | L<br>H<br>H | X<br>H<br>H           | L<br>L<br>L      | X<br>X<br>X      | Z<br>Z<br>Z                | H<br>X<br>X | H<br>X<br>X           | H<br>X<br>X           | L<br>X<br>X           | L<br>X<br>X           | H<br>H<br>H | H<br>H<br>H | H<br>H<br>H | L<br>L<br>L           | L<br>L<br>L                | H<br>H<br>H | H<br>H<br>H      | L<br>L<br>L |

| Load on<br>Terminal<br>Count | ΤΙΤΙΙ       | L<br>L<br>L<br>L      | L<br>L<br>L<br>L | нтттт            | Z<br>Z<br>Z<br>Z<br>Z<br>Z | エエエエエエ      | L<br>L<br>L<br>L      | ΤΤΤΤΤ                 | ΤΤΤΤΤ                 | L<br>L<br>L<br>L      | нтттт       | H H L L H   | H H H H L   | L<br>H<br>H<br>H<br>L | H<br>L<br>H<br>L<br>H<br>L | エエーエエエ      |                  |             |

| Reset                        | Х           | Х                     | Н                | Х                | Х                          | Х           | Х                     | Х                     | Х                     | Х                     | L           | L           | L           | L                     | L                          | Н           | Н                | L           |

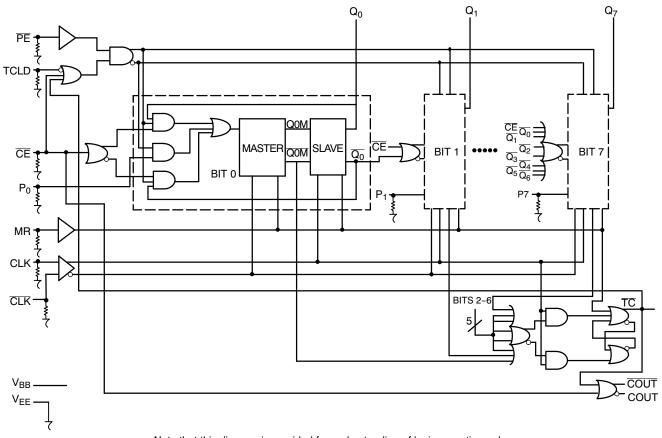

Note that this diagram is provided for understanding of logic operation only.

It should not be used for propagation delays as many gate functions are achieved internally without incurring a full gate delay.

Figure 3. 8-BIT Binary Counter Logic Diagram

# Table 4. ATTRIBUTES

| Characte                             | ristics                     | Value              |  |  |  |

|--------------------------------------|-----------------------------|--------------------|--|--|--|

| Internal Input Pulldown Resistor     | 75 kΩ                       |                    |  |  |  |

| Internal Input Pullup Resistor       | N/A                         |                    |  |  |  |

| ESD Protection                       | > 2 kV<br>> 100 V<br>> 2 kV |                    |  |  |  |

| Moisture Sensitivity, Indefinite Til | Pb Pkg                      | Pb-Free Pkg        |  |  |  |

|                                      | Level 2<br>N/A              | Level 2<br>Level 1 |  |  |  |

| Flammability Rating Oxygen Inde      | UL 94 V-0 @ 0.125 in        |                    |  |  |  |

| Transistor Count                     | 1226 Devices                |                    |  |  |  |

| Meets or exceeds JEDEC Spec          | EIA/JESD78 IC Latchup Test  |                    |  |  |  |

1. For additional information, see Application Note AND8003/D.

# Table 5. MAXIMUM RATINGS

| Symbol           | Parameter                                          | Condition 1                                    | Condition 2                                                           | Rating      | Unit         |

|------------------|----------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------|-------------|--------------|

| V <sub>CC</sub>  | PECL Mode Power Supply                             | V <sub>EE</sub> = 0 V                          |                                                                       | 6           | V            |

| $V_{EE}$         | NECL Mode Power Supply                             | V <sub>CC</sub> = 0 V                          |                                                                       | -6          | V            |

| VI               | PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | $\begin{array}{c} V_{I} \leq V_{CC} \\ V_{I} \geq V_{EE} \end{array}$ | 6<br>-6     | V<br>V       |

| l <sub>out</sub> | Output Current                                     | Continuous<br>Surge                            |                                                                       | 50<br>100   | mA<br>mA     |

| I <sub>BB</sub>  | V <sub>BB</sub> Sink/Source                        |                                                |                                                                       | ± 0.5       | mA           |

| T <sub>A</sub>   | Operating Temperature Range                        |                                                |                                                                       | -40 to +70  | °C           |

| T <sub>stg</sub> | Storage Temperature Range                          |                                                |                                                                       | -65 to +150 | °C           |

| $\theta_{JA}$    | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | 32 LQFP<br>32 LQFP                                                    | 74<br>61    | °C/W<br>°C/W |

| $\theta_{JC}$    | Thermal Resistance (Junction-to-Case)              | Standard Board                                 | 32 LQFP                                                               | 12 to 17    | °C/W         |

| $\theta_{JA}$    | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | QFN-32<br>QFN-32                                                      | 31<br>27    | °C/W<br>°C/W |

| $\theta_{JC}$    | Thermal Resistance (Junction-to-Case)              | (Junction-to-Case) 2S2P QFN-32                 |                                                                       |             |              |

| T <sub>sol</sub> | Wave Solder Pb<br>Pb-Free                          |                                                |                                                                       | 265<br>265  | °C           |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

|                 |                                                                                  |      | –40°C |      |      | 25°C |      |      | 70°C |      |      |

|-----------------|----------------------------------------------------------------------------------|------|-------|------|------|------|------|------|------|------|------|

| Symbol          | Characteristic                                                                   | Min  | Тур   | Мах  | Min  | Тур  | Max  | Min  | Тур  | Max  | Unit |

| I <sub>EE</sub> | Power Supply Current                                                             | 130  | 170   | 210  | 130  | 177  | 210  | 130  | 180  | 210  | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 3)                                                     | 2155 | 2280  | 2405 | 2155 | 2280 | 2405 | 2155 | 2280 | 2405 | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 3)                                                      | 1355 | 1480  | 1605 | 1355 | 1480 | 1605 | 1355 | 1480 | 1605 | mV   |

| VIH             | Input HIGH Voltage (Single-Ended)                                                | 2075 |       | 2420 | 2075 |      | 2420 | 2075 |      | 2420 | mV   |

| V <sub>IL</sub> | Input LOW Voltage (Single-Ended)                                                 | 1355 |       | 1675 | 1355 |      | 1675 | 1355 |      | 1675 | mV   |

| $V_{BB}$        | Output Voltage Reference                                                         | 1775 | 1875  | 1975 | 1775 | 1875 | 1975 | 1775 | 1875 | 1975 | mV   |

| VIHCMR          | Input HIGH Voltage Common Mode<br>Range (Differential Configuration)<br>(Note 4) | 2.0  |       | 3.3  | 2.0  |      | 3.3  | 2.0  |      | 3.3  | V    |

| Ι <sub>ΙΗ</sub> | Input HIGH Current                                                               |      |       | 150  |      |      | 150  |      |      | 150  | μA   |

| I <sub>IL</sub> | Input LOW Current                                                                | 0.5  |       |      | 0.5  |      |      | 0.5  |      |      | μA   |

# Table 6. 100EP DC CHARACTERISTICS, PECL V<sub>CC</sub> = 3.3 V, V<sub>EE</sub> = 0 V (Note 2)

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

2. Input and output parameters vary 1:1 with V<sub>CC</sub>. V<sub>EE</sub> can vary +0.3 V to -0.3 V.

3. All loading with 50 ohms to  $V_{CC}$ -2.0 volts.

4. V<sub>IHCMR</sub> min varies 1:1 with V<sub>EE</sub>, V<sub>IHCMR</sub> max varies 1:1 with V<sub>CC</sub>. The V<sub>IHCMR</sub> range is referenced to the most positive side of the differential input signal.

|                    |                                                                                  |                      | -40°C |       |                      | 25°C  |       |                      | 70°C  |       |      |

|--------------------|----------------------------------------------------------------------------------|----------------------|-------|-------|----------------------|-------|-------|----------------------|-------|-------|------|

| Symbol             | Characteristic                                                                   | Min                  | Тур   | Max   | Min                  | Тур   | Max   | Min                  | Тур   | Max   | Unit |

| I <sub>EE</sub>    | Power Supply Current                                                             | 130                  | 170   | 210   | 130                  | 177   | 210   | 130                  | 180   | 210   | mA   |

| V <sub>OH</sub>    | Output HIGH Voltage (Note 6)                                                     | -1145                | -1020 | -895  | -1145                | -1020 | -895  | -1145                | -1020 | -895  | mV   |

| V <sub>OL</sub>    | Output LOW Voltage (Note 6)                                                      | -1945                | -1820 | -1695 | -1945                | -1820 | -1695 | -1945                | -1820 | -1695 | mV   |

| VIH                | Input HIGH Voltage (Single-Ended)                                                | -1225                |       | -880  | -1225                |       | -880  | -1225                |       | -880  | mV   |

| VIL                | Input LOW Voltage (Single-Ended)                                                 | -1945                |       | -1625 | -1945                |       | -1625 | -1945                |       | -1625 | mV   |

| V <sub>BB</sub>    | Output Voltage Reference                                                         | -1525                | -1425 | -1325 | -1525                | -1425 | -1325 | -1525                | -1425 | -1325 | mV   |

| V <sub>IHCMR</sub> | Input HIGH Voltage Common Mode<br>Range (Differential Configuration)<br>(Note 7) | V <sub>EE</sub> +2.0 |       | 0.0   | V <sub>EE</sub> +2.0 |       | 0.0   | V <sub>EE</sub> +2.0 |       | 0.0   | V    |

| I <sub>IH</sub>    | Input HIGH Current                                                               |                      |       |       |                      |       | 150   |                      |       | 150   | μA   |

| IIL                | Input LOW Current                                                                | 0.5                  |       |       | 0.5                  |       |       | 0.5                  |       |       | μA   |

# Table 7. 100EP DC CHARACTERISTICS, NECL V<sub>CC</sub> = 0 V, V<sub>EE</sub> = -3.6 V to -3.0 V (Note 5)

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

5. Input and output parameters vary 1:1 with  $V_{CC}$ .

6. All loading with 50 ohms to  $V_{CC}$ -2.0 volts.

7. VIHCMR min varies 1:1 with VEE, VIHCMR max varies 1:1 with VCC. The VIHCMR range is referenced to the most positive side of the differential input signal.

|                                      |                                                                                                          |                                        | -40°C                                     |                                        |                                        | 25°C                                      |                                        |                                        | 70°C                                      |                                         |      |

|--------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------------|-----------------------------------------|------|

| Symbol                               | Characteristic                                                                                           | Min                                    | Тур                                       | Max                                    | Min                                    | Тур                                       | Max                                    | Min                                    | Тур                                       | Max                                     | Unit |

| fcount                               | Maximum Frequency<br>Count & Division Modes<br>Q, TC, COUT/COUT                                          | 1.3                                    | 1.5                                       |                                        | 1.2                                    | 1.4                                       |                                        | 1.2                                    | 1.3                                       |                                         | GHz  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>MR to Q<br>CLK to TC<br>MR to TC<br>MR to TC<br>CLK to COUT/COUT<br>MR to COUT/COUT | 350<br>400<br>350<br>400<br>475<br>450 | 511<br>550<br>511<br>555<br>705<br>720    | 650<br>700<br>650<br>700<br>850<br>850 | 400<br>400<br>400<br>400<br>500<br>500 | 550<br>570<br>550<br>570<br>745<br>760    | 700<br>750<br>700<br>750<br>900<br>900 | 480<br>450<br>480<br>520<br>550<br>570 | 610<br>630<br>610<br>635<br>825<br>830    | 780<br>820<br>780<br>820<br>1000<br>950 | ps   |

| ts                                   | Setup Time P0<br>P1 to P4<br>P5 to P7<br>CE<br>PE<br>TCLD                                                | 400<br>300<br>250<br>500<br>500<br>550 | 240<br>140<br>80<br>320<br>315<br>355     |                                        | 400<br>300<br>250<br>500<br>500<br>550 | 240<br>135<br>65<br>330<br>320<br>365     |                                        | 400<br>300<br>250<br>500<br>500<br>550 | 245<br>125<br>55<br>340<br>325<br>380     |                                         | ps   |

| tн                                   | Hold Time P0<br>P1 to P4<br>P5 to P7<br>CE<br>PE<br>TCLD                                                 | 100<br>50<br>150<br>600<br>625<br>525  | -145<br>-160<br>-105<br>380<br>465<br>320 |                                        | 100<br>50<br>150<br>600<br>625<br>525  | -155<br>-170<br>-110<br>410<br>500<br>325 |                                        | 100<br>50<br>150<br>600<br>625<br>525  | -170<br>-180<br>-115<br>450<br>535<br>340 |                                         | ps   |

| <b>ţ</b> JITTER                      | Clock Random Jitter<br>(RMS, 1000 Waveforms)                                                             |                                        | 2.6                                       | 8.5                                    |                                        | 2.5                                       | 8.0                                    |                                        | 2.5                                       | 8.0                                     | ps   |

| t <sub>RR</sub>                      | Reset Recovery Time                                                                                      | 400                                    | 195                                       |                                        | 400                                    | 205                                       |                                        | 400                                    | 220                                       |                                         | ps   |

| t <sub>PW</sub>                      | Minimum Pulse Width CLK<br>Minimum Pulse Width MR                                                        | 385<br>550                             | 334<br>380                                |                                        | 416<br>550                             | 357<br>380                                |                                        | 416<br>550                             | 385<br>380                                |                                         | ps   |

| t <sub>r</sub> , t <sub>f</sub>      | Output Rise/Fall Times<br>20% - 80%                                                                      | 90                                     | 180                                       | 320                                    | 100                                    | 190                                       | 320                                    | 125                                    | 215                                       | 450                                     | ps   |

| Table 8. AC CHARACTERISTICS V <sub>EE</sub> = -3.0 V to -3.6 V; V <sub>CC</sub> = 0 V or V <sub>CC</sub> = 3.0 V to 3.6 V; V <sub>EE</sub> = 0 V (Note 8) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

8. Measured using a 750 mV source, 50% duty cycle clock source. All loading with 50 ohms to  $V_{CC}$ -2.0 V.

# **APPLICATIONS INFORMATION**

#### **Cascading Multiple EP016A Devices**

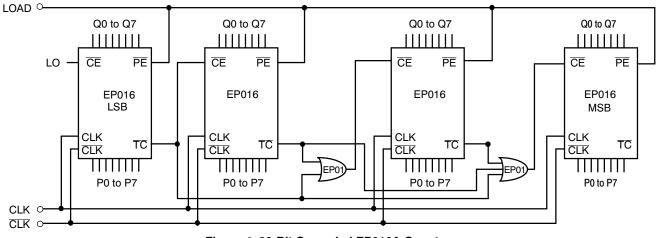

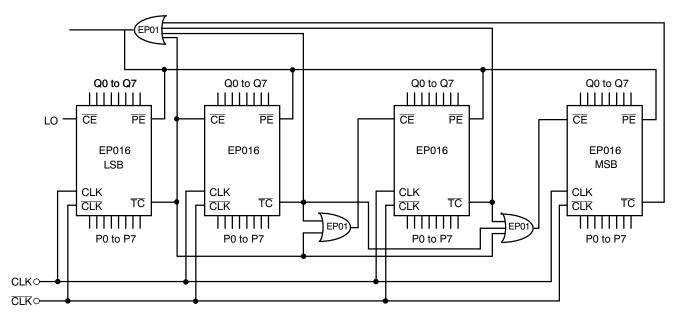

For applications which call for larger than 8-bit counters multiple EP016As can be tied together to achieve very wide bit width counters. The active low terminal count ( $\overline{\text{TC}}$ ) output and count enable input ( $\overline{\text{CE}}$ ) greatly facilitate the cascading of EP016A devices. Two EP016As can be cascaded without the need for external gating, however for counters wider than 16 bits external OR gates are necessary for cascade implementations.

Figure 4 below pictorially illustrates the cascading of 4 EP016As to build a 32-bit high frequency counter. Note the EP01 gates used to OR the terminal count outputs of the lower order EP016As to control the counting operation of the higher order bits. When the terminal count of the preceding device (or devices) goes low (the counter reaches an all 1s state) the more significant EP016A is set in its count mode and will count one binary digit upon the next positive clock transition. In addition, the preceding devices will also

count one bit thus sending their terminal count outputs back to a high state disabling the count operation of the more significant counters and placing them back into hold modes. Therefore, for an EP016A in the chain to count, all of the lower order terminal count outputs must be in the low state. The bit width of the counter can be increased or decreased by simply adding or subtracting EP016A devices from Figure 4 and maintaining the logic pattern illustrated in the same figure.

The maximum frequency of operation for a cascaded counter chain is set by the propagation delay of the  $\overline{\text{TC}}$  output, the necessary setup time of the  $\overline{\text{CE}}$  input, and the propagation delay through the OR gate controlling it (for 16-bit counters the limitation is only the  $\overline{\text{TC}}$  propagation delay and the  $\overline{\text{CE}}$  setup time). Figure 4 shows EP01 gates used to control the count enable inputs, however, if the frequency of operation is slow enough, a LVECL OR gate can be used. Using the worst case guarantees for these parameters.

Figure 4. 32-Bit Cascaded EP016A Counter

Note that this assumes the trace delay between the  $\overline{\text{TC}}$  outputs and the  $\overline{\text{CE}}$  inputs are negligible. If this is not the case estimates of these delays need to be added to the calculations.

#### **Programmable Divider**

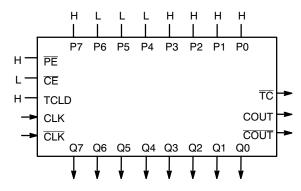

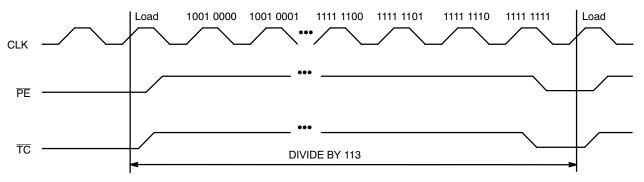

The EP016A has been designed with a control pin which makes it ideal for use as an 8-bit programmable divider. The TCLD pin (load on terminal count) when asserted reloads the data present at the parallel input pin (Pn's) upon reaching terminal count (an all 1s state on the outputs). Because this feedback is built internal to the chip, the programmable division operation will run at very nearly the same frequency as the maximum counting frequency of the device. Figure 5 below illustrates the input conditions necessary for utilizing the EP016A as a programmable divider set up to divide by 113.

# **APPLICATIONS INFORMATION** (continued)

Figure 5. Mod 2 to 256 Programmable Divider

To determine what value to load into the device to accomplish the desired division, the designer simply subtracts the binary equivalent of the desired divide ratio from the binary value for 256. As an example for a divide ratio of 113:

Pn's =  $256 - 113 = 8F_{16} = 1000 1111$ where:

P0 = LSB and P7 = MSB

Forcing this input condition as per the setup in Figure 5 will result in the waveforms of Figure 6. Note that the  $\overline{\text{TC}}$  output is used as the divide output and the pulse duration is equal to a full clock period. For even divide ratios, twice the desired divide ratio can be loaded into the EP016A and the  $\overline{\text{TC}}$  output can feed the clock input of a toggle flip flop to create a signal divided as desired with a 50% duty cycle.

| Table 9. Preset | Values for | Various Divide Ratios |  |

|-----------------|------------|-----------------------|--|

|-----------------|------------|-----------------------|--|

| Divide |    |    | Pr | eset D | ata Inp | outs |    |    |

|--------|----|----|----|--------|---------|------|----|----|

| Ratio  | P7 | P6 | P5 | P4     | P3      | P2   | P1 | P0 |

| 2      | Н  | Н  | Н  | Н      | Н       | Н    | Н  | L  |

| 3      | н  | Н  | н  | н      | н       | н    | L  | Н  |

| 4      | н  | н  | н  | н      | н       | н    | L  | L  |

| 5      | н  | н  | н  | н      | н       | L    | н  | н  |

| •      | •  | •  | •  | •      | •       | •    | •  | •  |

| •      | •  | •  | •  | •      | •       | •    | •  | •  |

| 112    | н  | L  | L  | н      | L       | L    | L  | L  |

| 113    | н  | L  | L  | L      | н       | н    | н  | н  |

| 114    | н  | L  | L  | L      | н       | н    | н  | L  |

| •      | •  | •  | •  | •      | •       | •    | •  | •  |

| •      | •  | •  | •  | •      | •       | •    | •  | •  |

| 254    | L  | L  | L  | L      | L       | L    | н  | L  |

| 255    | L  | L  | L  | L      | L       | L    | L  | н  |

| 256    | L  | L  | L  | L      | L       | L    | L  | L  |

A single EP016A can be used to divide by any ratio from 2 to 256 inclusive. If divide ratios of greater than 256 are needed multiple EP016As can be cascaded in a manner similar to that already discussed. When EP016As are cascaded to build larger dividers the TCLD pin will no longer provide a means for loading on terminal count. Because one does not want to reload the counters until all of the devices in the chain have reached terminal count, external gating of the  $\overline{TC}$  pins must be used for multiple EP016A divider chains.

Figure 6. Divide by 113 EP016A Programmable Divider Waveforms

#### **APPLICATIONS INFORMATION** (continued)

Figure 7. 32-Bit Cascaded EP016A Programmable Divider

Figure 7 shows a typical block diagram of a 32-bit divider chain. Once again to maximize the frequency of operation EP01 OR gates were used. For lower frequency applications a slower OR gate could replace the EP01. Note that for a 16-bit divider the OR function feeding the  $\overline{PE}$  (program enable) input CANNOT be replaced by a wire OR tie as the  $\overline{TC}$  output of the least significant EP016A must also feed the  $\overline{CE}$  input of the most significant EP016A. If the two  $\overline{TC}$ outputs were OR tied the cascaded count operation would not operate properly. Because in the cascaded form the  $\overline{PE}$ feedback is external and requires external gating, the maximum frequency of operation will be significantly less than the same operation in a single device.

#### **Maximizing EP016A Count Frequency**

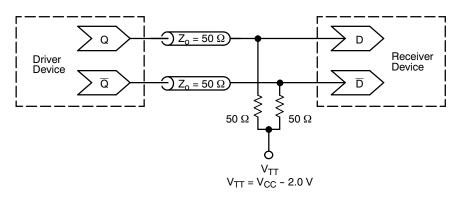

The EP016A device produces 9 fast transitioning single ended outputs, thus V<sub>CC</sub> noise can become significant in situations where all of the outputs switch simultaneously in the same direction. This V<sub>CC</sub> noise can negatively impact the maximum frequency of operation of the device. Since the device does not need to have the Q outputs terminated to count properly, it is recommended that if the outputs are not going to be used in the rest of the system they should be left unterminated. In addition, if only a subset of the Q outputs are used in the system only those outputs should be terminated. Not terminating the unused outputs will not only cut down the V<sub>CC</sub> noise generated but will also save in total system power dissipation. Following these guidelines will allow designers to either be more aggressive in their designs or provide them with an extra margin to the published data book specifications.

Figure 8. Typical Termination for Output Driver and Device Evaluation (See Application Note AND8020/D – Termination of ECL Logic Devices.)

# **ORDERING INFORMATION**

| Device           | Package              | Shipping <sup>†</sup> |  |  |  |

|------------------|----------------------|-----------------------|--|--|--|

| MC100EP016AFA    | LQFP-32              | 250 Units / Tray      |  |  |  |

| MC100EP016AFAG   | LQFP-32<br>(Pb-Free) | 250 Units / Tray      |  |  |  |

| MC100EP016AFAR2  | LQFP-32              | 2000 / Tape & Reel    |  |  |  |

| MC100EP016AFAR2G | LQFP-32<br>(Pb-Free) | 2000 / Tape & Reel    |  |  |  |

| MC100EP016AMNG   | QFN-32<br>(Pb-Free)  | 74 Units / Rail       |  |  |  |

| MC100EP016AMNR4G | QFN-32<br>(Pb-Free)  | 1000 / Tape & Reel    |  |  |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

| Resource | Reference | of A | oplication | Notes |

|----------|-----------|------|------------|-------|

|          |           |      | phoadon    |       |

| AN1405/D  | - | ECL Clock Distribution Techniques           |  |

|-----------|---|---------------------------------------------|--|

| AN1406/D  | - | Designing with PECL (ECL at +5.0 V)         |  |

| AN1503/D  | - | ECLinPS <sup>™</sup> I/O SPiCE Modeling Kit |  |

| AN1504/D  | - | Metastability and the ECLinPS Family        |  |

| AN1568/D  | - | Interfacing Between LVDS and ECL            |  |

| AN1672/D  | - | The ECL Translator Guide                    |  |

| AND8001/D | - | Odd Number Counters Design                  |  |

| AND8002/D | - | Marking and Date Codes                      |  |

| AND8020/D | - | Termination of ECL Logic Devices            |  |

| AND8066/D | - | Interfacing with ECLinPS                    |  |

| AND8090/D | - | AC Characteristics of ECL Devices           |  |

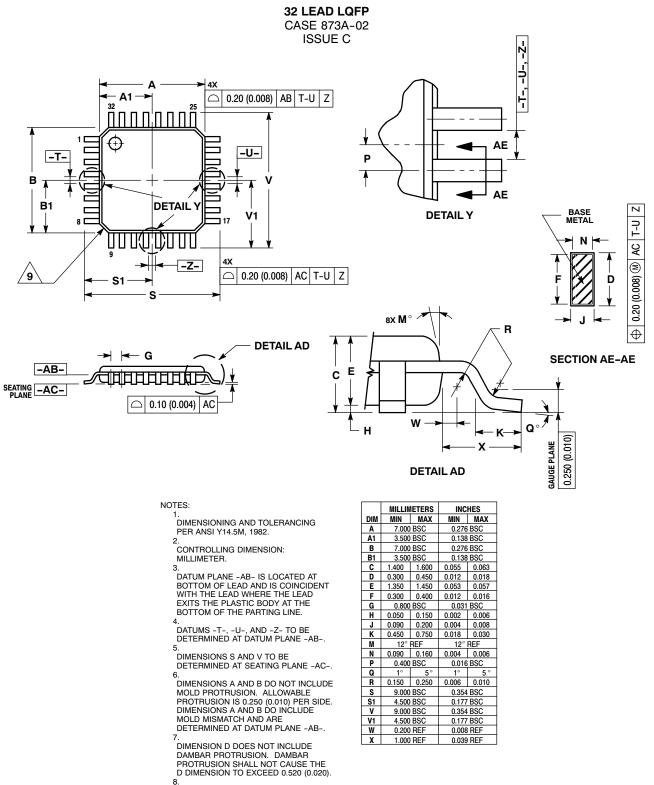

#### PACKAGE DIMENSIONS

o. MINIMUM SOLDER PLATE THICKNESS SHALL BE 0.0076 (0.0003).

9. EXACT SHAPE OF EACH CORNER MAY VARY FROM DEPICTION.

> http://onsemi.com 12

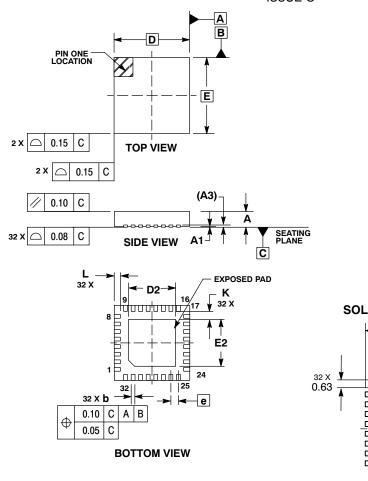

#### PACKAGE DIMENSIONS

QFN32 5\*5\*1 0.5 P CASE 488AM-01 ISSUE O

NOTES

- DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM TERMINAL 4

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |       |       |  |  |

|-----|-------------|-------|-------|--|--|

| DIM | MIN         | NOM   | MAX   |  |  |

| Α   | 0.800       | 0.900 | 1.000 |  |  |

| A1  | 0.000       | 0.025 | 0.050 |  |  |

| A3  | 0.200 REF   |       |       |  |  |

| b   | 0.180       | 0.250 | 0.300 |  |  |

| D   | 5.00 BSC    |       |       |  |  |

| D2  | 2.950       | 3.100 | 3.250 |  |  |

| Е   | 5.00 BSC    |       |       |  |  |

| E2  | 2.950       | 3.100 | 3.250 |  |  |

| е   | 0.500 BSC   |       |       |  |  |

| К   | 0.200       |       |       |  |  |

| L   | 0.300       | 0.400 | 0.500 |  |  |

**SOLDERING FOOTPRINT\*** 5.30 3.20 000000000 3.20 5.30 32 X 0.28 28 X 0.50 PITCH

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ECLinPS is a trademark of Semiconductor Components INdustries, LLC (SCILLC).

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILIC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILIC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILIC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILIC does not convey any license under its patent rights or the rights of others. SCILIC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

onsemi:

MC100EP016AFA MC100EP016AFAG MC100EP016AFAR2 MC100EP016AFAR2G MC100EP016AMNG MC100EP016AMNR4G