Sample &

Buy

#### **OPA541**

SBOS153B-SEPTEMBER 2000-REVISED JANUARY 2016

# **OPA541 High Power Monolithic Operational Amplifier**

Technical

Documents

### 1 Features

- Power Supplies to ±40 V

- Output Current to 10-A Peak

- Programmable Current Limit

- Industry-Standard Pinout

- FET Input

- TO-3 and Low-Cost Power Plastic Packages

### 2 Applications

- Motor Drivers

- Servo Amplifiers

- Synchro Excitation

- Audio Amplifiers

- Programmable Power Supplies

### 3 Description

The OPA541 device is a power-operational amplifier capable of operation from power supplies up to  $\pm 40$  V, and delivering continuous output currents up to 5 A. Internal current-limit circuitry can be user-programmed with a single external resistor, protecting the amplifier and load from fault conditions. The OPA541 devices fabricated are using a proprietary bipolar and FET process.

The OPA541 uses a single current-limit resistor to set both the positive and negative current limits. Applications currently using hybrid power amplifiers requiring two current-limit resistors do need not to be modified.

The OPA541 is available in an 11-pin power plastic package and an industry-standard 8-pin TO-3 hermetic package. The power plastic pachage has a copper-lead frame to maximize heat transfer. The TO-3 package is isolated from all circuitry, allowing it to be mounted directly to a heat sink without special insulators.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)     |

|-------------|-------------|---------------------|

| OPA541      | TO-220 (11) | 10.70 mm × 20.02 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

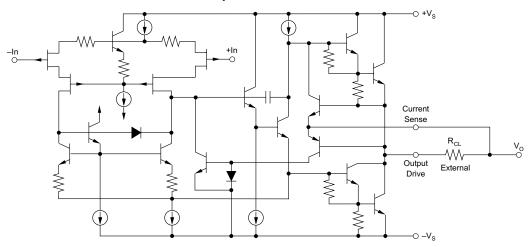

#### Simplified Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

2

# **Table of Contents**

| 1 | Fea  | tures 1                            |  |

|---|------|------------------------------------|--|

| 2 | Арр  | lications 1                        |  |

| 3 | Des  | cription1                          |  |

| 4 | Rev  | ision History 2                    |  |

| 5 | Pin  | Configuration and Functions        |  |

| 6 | Spe  | cifications                        |  |

|   | 6.1  | Absolute Maximum Ratings 4         |  |

|   | 6.2  | ESD Ratings 4                      |  |

|   | 6.3  | Recommended Operating Conditions 4 |  |

|   | 6.4  | Thermal Information 4              |  |

|   | 6.5  | Electrical Characteristics5        |  |

|   | 6.6  | Typical Characteristics 6          |  |

| 7 | Deta | ailed Description8                 |  |

|   | 7.1  | Overview                           |  |

|   | 7.2  | Functional Block Diagram 8         |  |

|   | 7.3  | Feature Description8               |  |

|   |      |                                    |  |

|    | 7.4  | Device Functional Modes                  |    |

|----|------|------------------------------------------|----|

| 8  | Appl | ication and Implementation               | 9  |

|    |      | Application Information                  |    |

|    | 8.2  | Typical Applications                     | 11 |

| 9  | Pow  | er Supply Recommendations                | 15 |

| 10 | Layo | out                                      | 15 |

|    |      | Layout Guidelines                        |    |

|    |      | Layout Example                           |    |

| 11 | Devi | ce and Documentation Support             | 16 |

|    | 11.1 | Documentation Support                    | 16 |

|    | 11.2 | Community Resources                      | 16 |

|    |      | Trademarks                               |    |

|    | 11.4 | Electrostatic Discharge Caution          | 16 |

|    | 11.5 | Glossary                                 | 16 |

| 12 |      | hanical, Packaging, and Orderable mation | 16 |

## 4 Revision History

.

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision A (August 2006) to Revision B

Page

| • | Added ESD Ratings table, Thermal Information tables, Feature Description section, Device Functional Modes, |

|---|------------------------------------------------------------------------------------------------------------|

|   | Application and Implementation section, Power Supply Recommendations section, Layout section, Device and   |

|   | Documentation Support section, and Mechanical, Packaging, and Orderable Information section 1              |

| • | Deleted THERMAL RESISTANCE section from <i>Electrical Characteristics</i>                                  |

#### EXAS **NSTRUMENTS**

www.ti.com

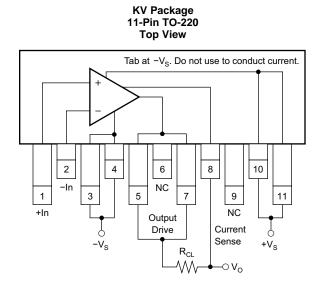

## 5 Pin Configuration and Functions

### **Pin Functions**

|     | PIN           |     | DESCRIPTION               |  |  |  |  |  |

|-----|---------------|-----|---------------------------|--|--|--|--|--|

| NO. | NAME          | I/O | DESCRIPTION               |  |  |  |  |  |

| 1   | +In           | I   | +Input                    |  |  |  |  |  |

| 2   | –In           | I   | -Input                    |  |  |  |  |  |

| 3   | –Vs           | -   | egative power supply      |  |  |  |  |  |

| 4   | –Vs           | -   | legative power supply     |  |  |  |  |  |

| 5   | Output        | 0   | Output                    |  |  |  |  |  |

| 6   | NC            | -   | No internal connection    |  |  |  |  |  |

| 7   | Output        | 0   | Output                    |  |  |  |  |  |

| 8   | Current Sense | I   | Current sensing input pin |  |  |  |  |  |

| 9   | NC            | -   | No internal connection    |  |  |  |  |  |

| 10  | +Vs           | -   | Positive power supply     |  |  |  |  |  |

| 11  | +Vs           | -   | Positive power supply     |  |  |  |  |  |

### 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                            |                             | MIN MA         | AX UNIT |  |  |  |

|--------------------------------------------|-----------------------------|----------------|---------|--|--|--|

| Supply voltage, +V <sub>S</sub> to $-V_S$  |                             | 8              | 0 V     |  |  |  |

| Output current                             | Output current              |                |         |  |  |  |

| Power dissipation, Internal <sup>(2)</sup> | 12                          | 25 W           |         |  |  |  |

| Input voltage, differential                | Input voltage, differential |                |         |  |  |  |

| Input voltage, common-mode                 | +/                          | / <sub>S</sub> |         |  |  |  |

| Temperature, pin solder, 10 s              | 30                          | 00 °C          |         |  |  |  |

| Junction temperature <sup>(2)</sup>        |                             | 15             | 50 °C   |  |  |  |

|                                            | AP                          | -40 8          | 5       |  |  |  |

| Operating temperature (case)               | AM, BM, SM                  | -55 12         | 25 °C   |  |  |  |

|                                            | AP                          | -25 8          | 5       |  |  |  |

| Storage temperature, T <sub>stg</sub>      | AM, BM, SM                  | -65 15         | 50 °C   |  |  |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTTF.

### 6.2 ESD Ratings

|      |        |                         |                                                                                | VALUE | UNIT |

|------|--------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V    | F      | lastrastatia diasharaa  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V (I | ESD) E | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                          | MIN     | MAX      | UNIT |

|--------------------------|---------|----------|------|

| Supply Voltage (V+ - V-) | 10 (±5) | 80 (±40) | V    |

| Specified temperature    | -40     | 125      | °C   |

### 6.4 Thermal Information

|                       |                                              | OPA         |            |      |

|-----------------------|----------------------------------------------|-------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | KV (TO-220) | LMF (TO-3) | UNIT |

|                       |                                              | 11 PINS     | 8 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 21.5        | —          | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 17.4        | —          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.2         | —          | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.5         | —          | °C/W |

| $\psi_{JB}$           | Junction-to-board characterization parameter | 9.2         | —          | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.1         | 3          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

At T<sub>C</sub>= 25°C and V<sub>S</sub> =  $\pm$ 35 VDC, unless otherwise noted.

|                   | PARAMETER                 | TEST                               | CONDITIONS                     | MIN                        | TYP                        | MAX                | UNIT  |

|-------------------|---------------------------|------------------------------------|--------------------------------|----------------------------|----------------------------|--------------------|-------|

| INPUT OF          | FSET VOLTAGE              | ·                                  |                                |                            |                            |                    |       |

|                   | land offerstandling       |                                    | OPA541AM/AP                    |                            | ±2                         | ±10                |       |

|                   | Input offset voltage      | Specified                          | OPA541BM/SM                    |                            | ±0.1                       | ±1                 | mV    |

| .,                |                           | temperature                        | OPA541AM/AP                    |                            | ±20                        | ±40                |       |

| V <sub>OS</sub>   | vs temperature            | range<br>V <sub>S</sub> = ±10 V to | OPA541BM/SM                    |                            | ±15                        | ±30                | µV/°C |

|                   | vs supply voltage         | ±V <sub>MAX</sub>                  | OPA541AM/AP,                   |                            | ±2.5                       | ±10                | μV/V  |

|                   | vs power                  |                                    | OPA541BM/SM                    |                            | ±20                        | ±60                | μV/W  |

| I <sub>B</sub>    | Input bias current        |                                    |                                |                            | 4                          | 50                 | pА    |

|                   | lanut offerst summert     |                                    |                                |                            | ±1                         | ±30                | pА    |

| l <sub>os</sub>   | Input offset current      | Specified temper                   | ature range                    |                            |                            | 5                  | nA    |

| INPUT CH          | IARACTERISTICS            |                                    |                                |                            |                            |                    |       |

|                   | Common-mode voltage range | Specified temper                   | ature range                    | $\pm ( V_{\rm S}  - 6)$    | $\pm ( V_{S}  - 3)$        |                    | V     |

|                   | Common-mode rejection     | $V_{CM} = ( \pm V_S  - 6$          | V)                             | 95                         | 113                        |                    | dB    |

|                   | Input capacitance         |                                    |                                |                            | 5                          |                    | pF    |

|                   | Input impedance, DC       |                                    |                                |                            | 1                          |                    | ТΩ    |

| GAIN CH           | ARACTERISTICS             |                                    |                                |                            |                            |                    |       |

|                   | Open-loop gain at 10 Hz   | $R_L = 6 \Omega$                   |                                | 90                         | 97                         |                    | dB    |

|                   | Gain-bandwidth product    |                                    |                                |                            | 1.6                        |                    | MHz   |

| OUTPUT            |                           |                                    |                                |                            |                            |                    |       |

|                   |                           | $I_0 = 5 A$ , continu              | ous                            | $\pm ( V_{S}  - 5.5)$      | $\pm ( V_{S}  - 4.5)$      |                    |       |

|                   | Voltage swing             | I <sub>O</sub> = 2 A               |                                | ±( V <sub>S</sub>   - 4.5) | ±( V <sub>S</sub>   - 3.6) |                    | V     |

|                   |                           | I <sub>O</sub> = 0.5 A             |                                | $\pm( V_S -4)$             | $\pm ( V_S  - 3.2)$        |                    |       |

|                   | Peak current              |                                    |                                | 9                          | 10                         |                    | А     |

| AC PERF           | ORMANCE                   |                                    |                                |                            |                            |                    |       |

|                   | Slew rate                 |                                    |                                | 6                          | 10                         |                    | V/µs  |

|                   | Power bandwidth           | $R_{L} = 8 \Omega, V_{O} = 2$      | 0 Vrms                         | 45                         | 55                         |                    | kHz   |

|                   | Settling time to 0.1%     | 2-V Step                           |                                |                            | 2                          |                    | μs    |

|                   | Capacitive load           | Specified temper                   | ature range, G = 1             | 3.3                        |                            |                    | nF    |

|                   |                           | Specified temper                   | ature range, G > 10            |                            |                            | SOA <sup>(1)</sup> | IIF   |

|                   | Phase margin              | Specified temper                   | rature range, $R_L = 8 \Omega$ |                            | 40                         |                    | °C    |

| $\pm V_S$         | Power supply voltage      | Specified temper                   | ature range                    | ±10                        | ±30                        | ±35                | V     |

|                   | Quiescent current         |                                    |                                |                            | 20                         | 25                 | mA    |

| т                 | Tomporaturo rango         | AM, BM, AP                         |                                | -25                        |                            | 85                 | °C    |

| T <sub>CASE</sub> | Temperature range         | OPA541BM/SM                        |                                | -55                        |                            | 125                | U     |

(1) SOA is the Safe Operating Area shown in Figure 11.

# OPA541

SBOS153B-SEPTEMBER 2000-REVISED JANUARY 2016

www.ti.com

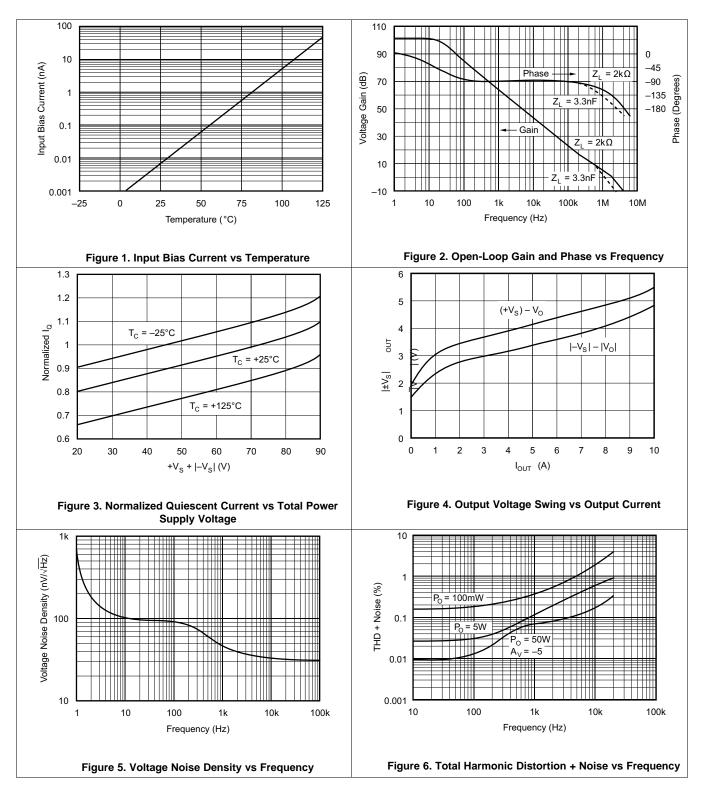

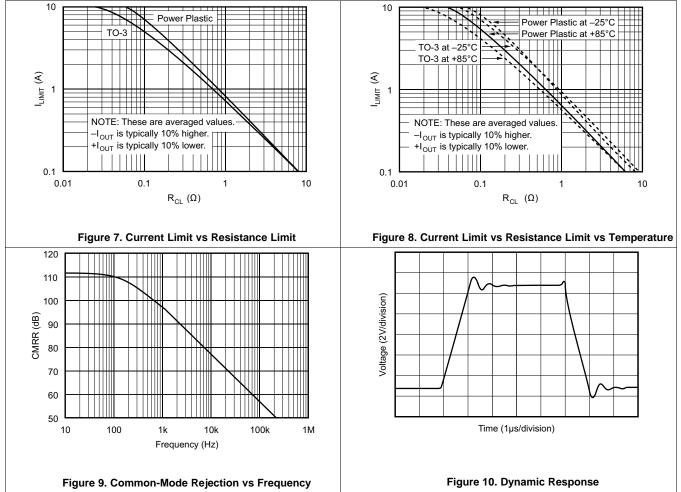

### 6.6 Typical Characteristics

At  $T_A = 25^{\circ}C$ ,  $V_S = \pm 35$  VDC, unless otherwise noted.

### **Typical Characteristics (continued)**

OPA541 SBOS153B-SEPTEMBER 2000-REVISED JANUARY 2016

www.ti.com

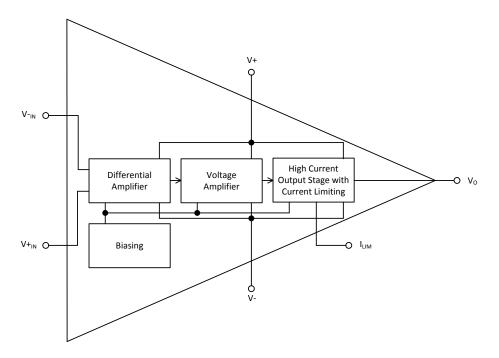

### 7 Detailed Description

### 7.1 Overview

The OPA541 uses a JFET input stage, followed by a main voltage gain stage, and a class A/B high current output stage.

### 7.2 Functional Block Diagram

### 7.3 Feature Description

The OPA541 JFET input stage reduces circuit loading and input bias currents. The class A/B high current output stage incorporates temperature compensated biasing to reduce crossover distortion. The output stage also includes a user settable current limit for amplifier and circuit protection.

### 7.4 Device Functional Modes

The OPA541 has a single functional mode. The OPA541 is operational when the power supply voltage exceeds 10 V ( $\pm$ 5 V) and less than 80 V ( $\pm$ 40 V).

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The OPA541 is specified for operation from 8 V to 80 V ( $\pm$ 4 V to  $\pm$ 40 V). Specifications apply over the –40°C to 85°C temperature range while the device operates from –40°C to 125°C. Parameters that can exhibit significant variance with regard to operating voltage or temperature are presented in *Typical Characteristics*.

#### 8.1.1 Current Limit

Internal current limit circuitry is controlled by a single external resistor,  $R_{CL}$ . Output load current flows through this external resistor. The current limit is activated when the voltage across this resistor is approximately a base-emitter turnon voltage. The value of the current limit resistor is calculated by Equation 1.

(AM, BM, SM)

$$R_{CL} = \frac{0.809}{|I_{LIM}|} - 0.057$$

(AP)  $R_{CL} = \frac{0.813}{|I_{LIM}|} - 0.02$  (1)

Because of the internal structure of the OPA541, the actual current limit depends on whether current is positive or negative. The above  $R_{CL}$  gives an average value. For a given  $R_{CL}$ ,  $+I_{OUT}$  will actually be limited at approximately 10% below the expected level, while  $-I_{OUT}$  will be limited approximately 10% above the expected level.

The current limit value decreases with increasing temperature due to the temperature coefficient of a baseemitter junction voltage. Similarly, the current limit value increases at low temperatures. Current limit versus resistor value and temperature effects are shown in *Typical Characteristics*. Approximate values for  $R_{CL}$  at other temperatures may be calculated by adjusting  $R_{CL}$  shown in Equation 2.

$$\Delta R_{CL} = \frac{-2mV}{|I_{LIM}|} \times (T - 25)$$

<sup>(2)</sup>

The adjustable current limit can be set to provide protection from short circuits. The safe short-circuit current depends on power supply voltage. See the discussion on safe operating area in *Safe Operating Area* to determine the proper current limit value.

Because the full load current flows through  $R_{CL}$ , it must be selected for sufficient power dissipation. For a 5-A current limit on the TO-3 package, the formula yields an  $R_{CL}$  of 0.105  $\Omega$  (0.143  $\Omega$  on the power plastic package due to different internal resistances). A continuous 5 A through 0.105  $\Omega$  would require an  $R_{CL}$  that can dissipate 2.625 W.

Sinusoidal outputs create dissipation according to RMS load current. For the same  $R_{CL}$ , AC peaks would still be limited to 5 A, but RMS current would be 3.5 A, and a current-limiting resistor with a lower power rating could be used. Some applications (such as voice amplification) are assured of signals with much lower duty cycles, allowing a current resistor with a low power rating. Wire-wound resistors may be used for  $R_{CL}$ . Some wire-wound resistors, however, have excessive inductance and may cause loop-stability problems. Evaluate circuit performance with the resistor type planned for production to assure proper circuit operation.

#### 8.1.2 Heat Sinking

Power amplifiers are rated by case temperature, not ambient temperature as with signal operational amplifiers. Sufficient heat sinking must be provided to keep the case temperature within rated limits for the maximum ambient temperature and power dissipation. The thermal resistance of the heat sink required may be calculated by Equation 3.

Copyright © 2000–2016, Texas Instruments Incorporated

(3)

NSTRUMENTS

**EXAS**

### **Application Information (continued)**

$$\theta_{\rm HS} = \frac{T_{\rm CASE} - T_{\rm AMBIENT}}{P_{\rm D} (\rm max)}$$

Commercially available heat sinks often specify their thermal resistance. These ratings are often suspect, however, because they depend greatly on the mounting environment and air flow conditions. Actual thermal performance should be verified by measuring the case temperature under the required load and environmental conditions.

No insulating hardware is required when using the TO-3 package. Because mica and other similar insulators typically add approximately  $0.7^{\circ}$ C/W thermal resistance, their elimination significantly improves thermal performance. See *Related Documentation* for further details on heat sinking. On the power plastic package, the metal tab may have a high or low impedance connection to  $-V_s$ . The case must be allowed to float, and likely assumes the potential of  $-V_s$ . Current must not be conducted through the case.

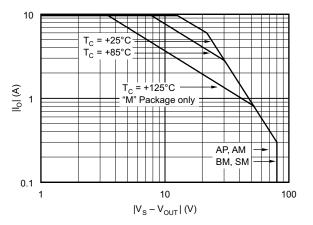

#### 8.1.3 Safe Operating Area

The safe operating area (SOA) plot provides comprehensive information on the power-handling abilities of the OPA541. The SOA shows the allowable output current as a function of the voltage across the conducting output transistor (see Figure 11). This voltage is equal to the power supply voltage minus the output voltage. For example, as the amplifier output swings near the positive power supply voltage, the voltage across the output transistor decreases and the device can safely provide large output currents demanded by the load. Short circuit protection requires evaluation of the SOA. When the amplifier output is shorted to ground, the full power supply voltage is impressed across the conducting output transistor. The current limit must be set to a value which is safe for the power supply voltage used. For instance, with  $V_{s} \pm 35$  V, a short to ground would force 35 V across the conducting power transistor. A current limit of 1.8 A would be safe.

Figure 11. Safe Operating Area

Reactive or EMF-generating loads such as DC motors can present difficult SOA requirements. With a purely reactive load, output voltage and load current are 90° out of phase. Thus, peak output current occurs when the output voltage is zero and the voltage across the conducting transistor is equal to the full power supply voltage. See *Related Documentation* for further information on evaluating SOA.

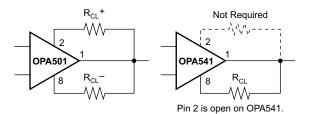

### 8.1.4 Replacing Hybrid Power Amplifiers

The OPA541 can be used in applications currently using various hybrid power amplifiers, including the OPA501, OPA511, OPA512, and 3573. Of course, the application must be evaluated to assure that the output capability and other performance attributes of the OPA541 meet the necessary requirements. These hybrid power amplifiers use two current limit resistors to independently set the positive and negative current limit value. Because the OPA541 uses only one current limit resistor to set both the positive and negative current limit, only one resistor such as Figure 12 need be installed. If installed, the resistor connected to pin 2 (TO-3 package) is superfluous, but is does no harm.

## **Application Information (continued)**

Figure 12. Isolating Capacitive Loads

Because one resistor carries the current previously carried by two, the resistor may require a high power rating. Minor adjustments may be required in the resistor value to achieve the same current limit value. Often, however, the change in current limit value when changing models is small compared to its variation over temperature. Many applications can use the same current limit resistor.

### 8.2 Typical Applications

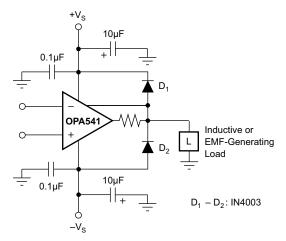

#### 8.2.1 Clamping Output for EMF-Generating Loads

Figure 13. Clamping Output for EMF-Generating Loads

#### 8.2.1.1 Design Requirements

- Motor drive with reversal requiring output clamping

- 20-V motor

- 1-Ω DC resistance

- 10-µH inductance

- 40°C maximum ambient temperature

### 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 Power Supply Requirements

Select the power supply based on the requirement to achieve a  $\pm 20$ -V output with up to a 5-A load. The maximum value for output voltage swing at 5-A is approximately within 4 V of either rail and  $\pm 25$ . These supplies provide sufficient output swing.

#### 8.2.1.2.2 Current Limit and SOA (Safe Operating Area)

Set the current limit to the highest possible value for the application which generally corresponds to a short circuit on the output. In this application this corresponds to 25-V stress on the output device and examination of the SOA (Safe Operating Area) graph in Figure 11 indicates that a 5-A current limit is within the 25°C SOA.

### Typical Applications (continued)

#### 8.2.1.2.3 Heat Sinking

Short circuit conditions at 5 A and 25 V must support 125 W of dissipation up to the 40°C ambient requirements of the application. This indicates the need for a heatsink with a  $R_{\theta HA}$  < 0.68°C/W, such as an Waekfield-Vette 345 series.

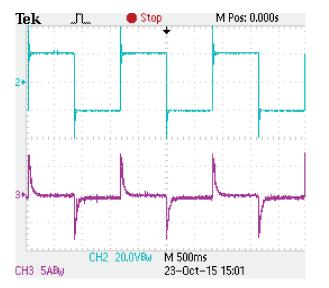

#### 8.2.1.3 Application Curve

The scope trace in Figure 14 depicts a motor reversal of a 20-V motor being driven by an OPA541 powered by  $\pm 25$  V. This motor has 1  $\Omega$  of DC resistance and 10  $\mu$ H of inductance.

#### NOTE

At the beginning of the reversal the motor inductance results in an overshoot up to the supply rail. This overshoot is clamped by the external fast recovery diodes. While the current shown exceeds the 5-A current limit, this current is actually flowing in the flyback diodes.

Figure 14. Transient Response

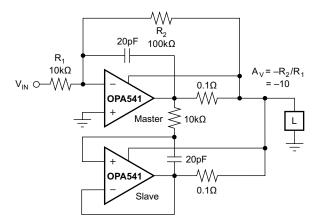

### 8.2.2 Paralleled Operation, Extended SOA

Parallel operation is often used to increase output current or wattage. However, due to their low output impedance, power operational amplifiers cannot be connected in parallel without modifying the circuits. Figure 15 shows one method of doing this. The upper amplifier is a master, configured as required to satisfy the circuit function, has a small sense resistor inside its feedback loop. The slave amplifier is a unity gain buffer. Thus, the output voltages of the two amplifiers are equal. If the two sense resistors connected to the load are equal, the amplifiers share current equally. More slaves may be added as desired. The additional resistor and capacitor on the slave enhance stability.

### **Typical Applications (continued)**

Figure 15. Paralleled Operation, Extended SOA

### 8.2.2.1 Design Requirements

Design requirements for the parallel connection in Figure 15 are shown here. The maximum current available from a single OPA541 cannot exceed 10 A:

- Gain from input to output of -10

- Current capability of > 15 A

- Short to ground on ±15-V supply rails at 25°C case temperature

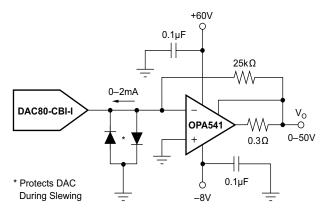

#### 8.2.3 Programmable Voltage Source

The programmable voltage source of Figure 16 uses the OPA541 as a current-to-voltage converter for a current output DAC (digital-to-analog converter). The diodes clamp any differential input voltages to safe levels for the OPA541. The OPA541 provides the gain to produce the desired output.

Figure 16. Programmable Voltage Source

#### 8.2.3.1 Design Requirements

Design requirements for Figure 16:

- Convert 0 to -2-mA current input to 0-V to 50-V output voltage

- Current capability of > 2.5 A

- Protection of current output DAC during fast slew

## **Typical Applications (continued)**

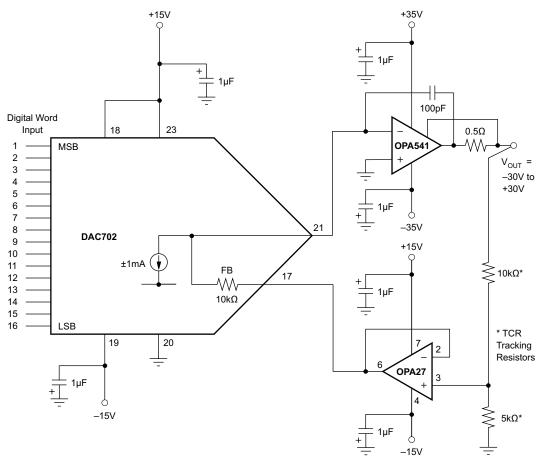

### 8.2.4 16-Bit Programmable Voltage Source

The 16-bit voltage source achieves its precision by using an OPA27 along with precision resistors in a feedback path that provides high overall accuracy.

Figure 17. 16-Bit Programmable Voltage Source

### 8.2.4.1 Design Requirements

Design requirements for the programmable voltage source shown in Figure 17:

- ±30-V output programmable to 16-bit resolution

- > ±1.5-A current capability

- < 500-µV offset at zero output</p>

- linearity error less than ±0.0015%

- differential linearity error less than ±0.003%

Texas

### 9 Power Supply Recommendations

The OPA541 is specified for operation from power supplies up to  $\pm 40$  V. The OPA541 can also be operated from unbalanced power supplies or a single power supply, as long as the total power supply voltage does not exceed 80 V. The power supplies should be bypassed with low series-impedance capacitors such as ceramic or tantalum. These must be located as near as practical to the power supply pins of the amplifier. Good power amplifier circuit layout is, in general, similar to good high-frequency layout: consider the path of the large power supply and output currents and avoid routing these connections near low-level input circuitry to avoid waveform distortion and oscillations.

### 10 Layout

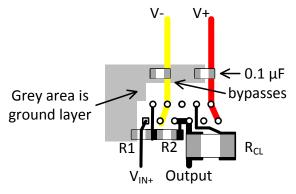

#### 10.1 Layout Guidelines

Figure 18 provides the recommended solder footprint for the TO-220 power package. The tab is electrically connected to the negative supply, V–. It may be desirable to isolate the tab of the TO-220 package from its mounting surface with a mica (or other film) insulator. For lowest overall thermal resistance, it is best to isolate the entire heat sink or OPA541 structure from the mounting surface rather than to use an insulator between the semiconductor and heat sink.

#### **10.2 Layout Example**

Figure 18. Recommended Layout

TEXAS INSTRUMENTS

www.ti.com

### **11** Device and Documentation Support

### **11.1 Documentation Support**

#### 11.1.1 Related Documentation

For related documentation see the following:

- Heat Sinking TO-3 Thermal Model, SBOA021.

- Power Amplifier Stress and Power Handling Limitations, SBOA022.

### 11.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.3 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### **11.4 Electrostatic Discharge Caution**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

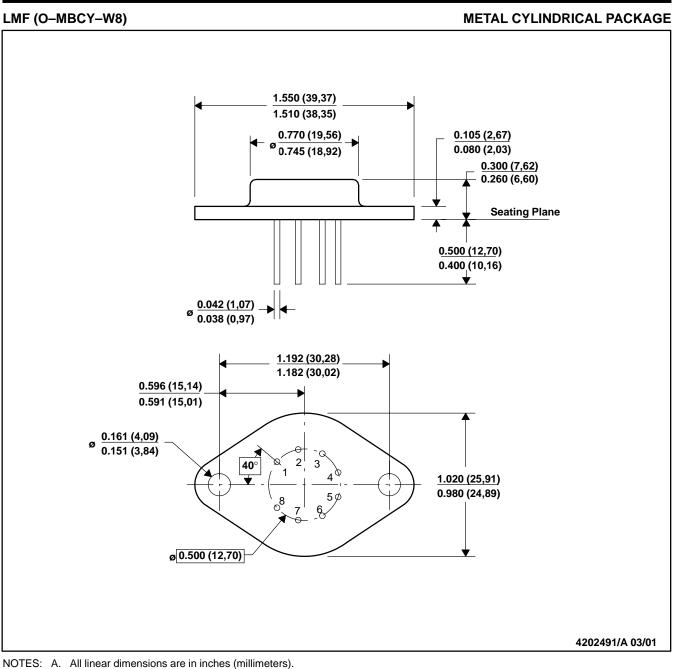

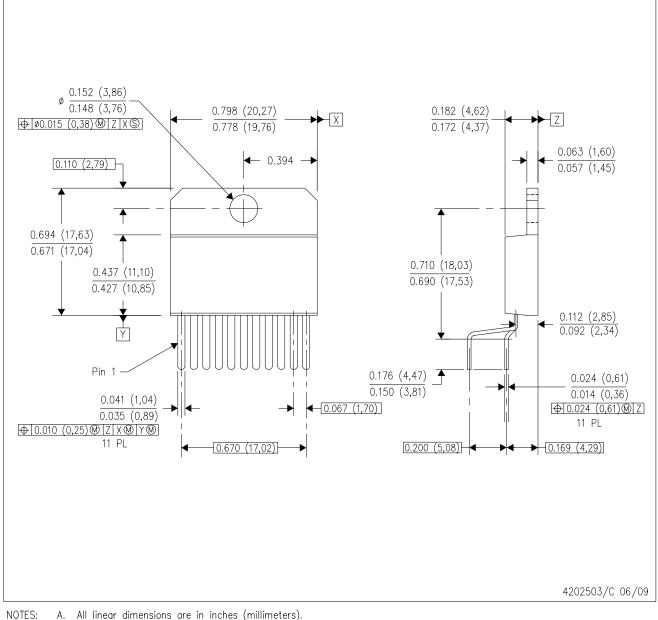

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

### **PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)            | Lead/Ball Finish<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|----------------------------|-------------------------|----------------------|--------------|-------------------------|---------|

| OPA541AM         | NRND          | TO-3         | LMF                | 8    | 1              | Pb-Free (RoHS<br>Exempt)   | NI                      | N / A for Pkg Type   |              | OPA541AM                |         |

| OPA541AP         | ACTIVE        | TO-220       | KV                 | 11   | 25             | Green (RoHS<br>& no Sb/Br) | SN                      | N / A for Pkg Type   | -25 to 85    | OPA541AP                | Samples |

| OPA541APG3       | ACTIVE        | TO-220       | KV                 | 11   | 25             | Green (RoHS<br>& no Sb/Br) | SN                      | N / A for Pkg Type   | -25 to 85    | OPA541AP                | Samples |

| OPA541BM         | NRND          | TO-3         | LMF                | 8    | 18             | Pb-Free (RoHS<br>Exempt)   | NI                      | N / A for Pkg Type   |              | OPA541BM                |         |

| OPA541SM         | NRND          | TO-3         | LMF                | 8    | 18             | Pb-Free (RoHS<br>Exempt)   | NI                      | N / A for Pkg Type   |              | OPA541<br>OPA541SM      |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

6-Feb-2020

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **MECHANICAL DATA**

MMBC005 - APRIL 2001

- - B. This drawing is subject to change without notice.

- C. Leads in true position within 0.010 (0,25) R @ MMC at seating plane.

- D. Pin numbers shown for reference only. Numbers may not be marked on package.

KV (R-PZFM-T11)

PLASTIC FLANGE-MOUNT

- A. An integr dimensions are in incres (minimeters).B. This drawing is subject to change without notice.

- C. Controlling dimension: inch.

- D. All lead dimensions apply before solder dip.

- E. Falls within JEDEC MO-48-AA.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated