# SPI Serial EEPROM 512 Kbits (65,536 x 8)

### **Features**

- · Serial Peripheral Interface (SPI) Compatible

- Supports SPI Modes 0 (0,0) and 3 (1,1):

- Data sheet describes mode 0 operation

- · Low-Voltage Operation:

- 1.8V (V<sub>CC</sub> = 1.8V to 5.5V)

- Industrial Temperature Range: -40°C to +85°C

- 20 MHz Clock Rate (5V)

- 128-Byte Page Mode

- · Block Write Protection:

- Protect 1/4, 1/2 or entire array

- Write-Protect (WP) Pin and Write Disable Instructions for Both Hardware and Software Data Protection

- · Self-Timed Write Cycle within 5 ms Maximum

- ESD Protection > 4,000V

- · High Reliability:

- Endurance: 1,000,000 write cycles

- Data retention: 100 years

- · Green (Lead-free/Halide-free/RoHS Compliant) Package Options

- Die Sale Options: Wafer Form and Bumped Wafers

## **Packages**

8-Lead SOIC and 8-Lead TSSOP

## **Table of Contents**

| Fea | eatures                        |                        | 1  |

|-----|--------------------------------|------------------------|----|

| Pad | ackages                        |                        | 1  |

| 1.  | Package Types (not to scale)   |                        | 4  |

| 2.  | Pin Description                |                        | 5  |

|     | 2.1. Chip Select (CS)          |                        | 5  |

|     | 2.2. Serial Data Output (SO)   | )                      | 5  |

|     | 2.3. Write-Protect (WP)        |                        | 5  |

|     | 2.4. Ground                    |                        | 5  |

|     | 2.5. Serial Data Input (SI)    |                        | 5  |

|     | 2.6. Serial Data Clock (SCK)   | )                      | 6  |

|     | 2.7. Device Power Supply (V    | /cc)                   | 6  |

| 3.  | Description                    |                        | 7  |

|     | 3.1. SPI Bus Host Connection   | ons to Serial EEPROMs  | 7  |

|     | 3.2. Block Diagram             |                        | 8  |

| 4.  | Electrical Characteristics     |                        | 9  |

|     | 4.1. Absolute Maximum Rati     | ings                   | 9  |

|     | 4.2. DC and AC Operating R     | Range                  | 9  |

|     | 4.3. DC Characteristics        |                        | 9  |

|     | 4.4. AC Characteristics        |                        | 10 |

|     | 4.5. SPI Synchronous Data      | Timing                 | 12 |

|     | 4.6. Electrical Specifications |                        | 12 |

| 5.  | Device Operation               |                        | 15 |

|     | •                              | on the SPI Bus         |    |

|     | 5.2. Device Opcodes            |                        | 16 |

|     |                                |                        |    |

|     | 5.4. Write Protection          |                        | 17 |

| 6.  | Device Commands and Addres     | ssing                  | 18 |

|     | 6.1. STATUS Register Bit De    | efinition and Function | 18 |

|     | 6.2. Read STATUS Register      | (RDSR)                 | 19 |

|     | 6.3. Write Enable (WREN) and   | d Write Disable (WRDI) | 19 |

|     | 6.4. Write STATUS Register     | (WRSR)                 | 20 |

| 7.  | Read Sequence                  |                        | 23 |

| 8.  | Write Sequence                 |                        | 24 |

|     | 8.1. Byte Write                |                        | 24 |

|     | 8.2. Page Write                |                        | 24 |

|     | 8.3. Polling Routine           |                        | 25 |

| 9.  | Packaging Information          |                        | 26 |

|     | 9.1. Package Marking Inform    | nation                 | 26 |

|     |                                |                        |    |

| 10. Revision History                      | 33 |

|-------------------------------------------|----|

| The Microchip Website                     | 34 |

| Product Change Notification Service       | 34 |

| Customer Support                          | 34 |

| Product Identification System             | 35 |

| Microchip Devices Code Protection Feature | 35 |

| Legal Notice                              | 36 |

| Trademarks                                | 36 |

| Quality Management System                 | 37 |

| Worldwide Sales and Service               | 38 |

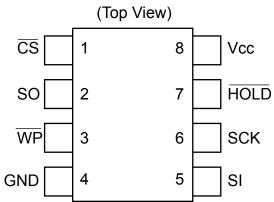

# 1. Package Types (not to scale)

## 8-Lead SOIC/TSSOP

## 2. Pin Description

The descriptions of the pins are listed in Table 2-1.

Table 2-1. Pin Function Table

| Name                | 8-Lead SOIC | 8-Lead TSSOP | Function              |

|---------------------|-------------|--------------|-----------------------|

| CS                  | 1           | 1            | Chip Select           |

| SO                  | 2           | 2            | Serial Data Output    |

| WP <sup>(1)</sup>   | 3           | 3            | Write-Protect         |

| GND                 | 4           | 4            | Ground                |

| SI                  | 5           | 5            | Serial Data Input     |

| SCK                 | 6           | 6            | Serial Data Clock     |

| HOLD <sup>(1)</sup> | 7           | 7            | Suspends Serial Input |

| V <sub>CC</sub>     | 8           | 8            | Device Power Supply   |

#### Note:

1. The Write-Protect (WP) and Hold (HOLD) pins should be driven high or low as appropriate.

### 2.1 Chip Select (CS)

The AT25512 is selected when the Chip Select ( $\overline{CS}$ ) pin is low. When the device is not selected, data will not be accepted via the Serial Data Input (SI) pin, and the Serial Output (SO) pin will remain in a high-impedance state.

To ensure robust operation, the  $\overline{CS}$  pin should follow  $V_{CC}$  upon power-up. It is therefore recommended to connect  $\overline{CS}$  to  $V_{CC}$  using a pull-up resistor (less than or equal to 10 k $\Omega$ ). After power-up, a low level on  $\overline{CS}$  is required prior to any sequence being initiated.

## 2.2 Serial Data Output (SO)

The Serial Data Output (SO) pin is used to transfer data out of the AT25512. During a read sequence, data is shifted out on this pin after the falling edge of the Serial Data Clock (SCK).

## 2.3 Write-Protect (WP)

The Write-Protect ( $\overline{WP}$ ) pin will allow normal read/write operations when held high. When the  $\overline{WP}$  pin is brought low and the WPEN bit is set to a logic '1', all write operations to the STATUS register are inhibited.  $\overline{WP}$  going low while  $\overline{CS}$  is still low will interrupt a write operation to the STATUS register. If the internal write cycle has already been initiated,  $\overline{WP}$  going low will have no effect on any write operation to the STATUS register. The  $\overline{WP}$  pin function is blocked when the WPEN bit in the STATUS register is set to a logic '0'. This will allow the user to install the AT25512 in a system with the  $\overline{WP}$  pin tied to ground and still be able to write to the STATUS register. All  $\overline{WP}$  pin functions are enabled when the WPEN bit is set to a logic '1'.

### 2.4 Ground

The ground reference for the power supply. GND should be connected to the system ground.

## 2.5 Serial Data Input (SI)

The Serial Data Input (SI) pin is used to transfer data into the device. It receives instructions, addresses and data. Data is latched on the rising edge of the Serial Data Clock (SCK).

## 2.6 Serial Data Clock (SCK)

The Serial Data Clock (SCK) pin is used to synchronize the communication between a host and the AT25512. Instructions, addresses or data present on the Serial Data Input (SI) pin is latched in on the rising edge of SCK, while output on the Serial Data Output (SO) pin is clocked out on the falling edge of SCK.

## 2.7 Device Power Supply (V<sub>CC</sub>)

The Device Power Supply ( $V_{CC}$ ) pin is used to supply the source voltage to the device. Operations at invalid  $V_{CC}$  voltages may produce spurious results and should not be attempted.

## 3. Description

The AT25512 provides 524,288 bits of Serial Electrically Erasable and Programmable Read-Only Memory (EEPROM) organized as 65,536 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The device is available in space-saving 8-lead SOIC and 8-lead TSSOP. All packages operate from 1.8V to 5.5V.

### 3.1 SPI Bus Host Connections to Serial EEPROMs

#### SPI Host: Microcontroller Data Clock (SCK) Data Output (SO) Data Input (SI) SO SCK SO SCK SO SCK SO SCK Client 0 Client 1 Client 2 Client 3 AT25XXX AT25XXX AT25XXX AT25XXX $\overline{\mathsf{CS}}$ $\overline{\mathsf{CS}}$ CS3 CS2 CS1 CS0 CS $\overline{\mathsf{CS}}$

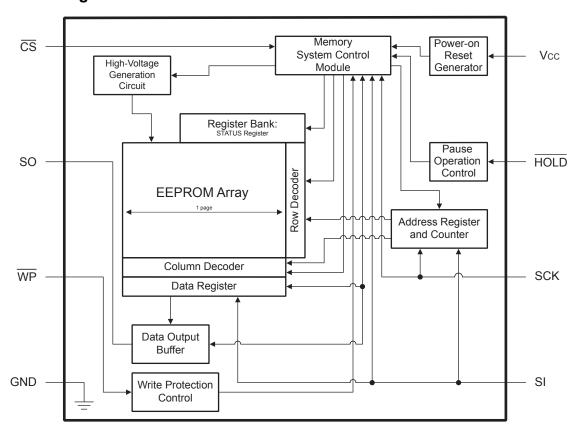

## 3.2 Block Diagram

#### 4. **Electrical Characteristics**

#### 4.1 **Absolute Maximum Ratings**

Operating temperature -55°C to +125°C -65°C to +150°C Storage temperature Voltage on any pin with respect to ground -1.0V to +7.0V  $V_{CC}$ 6.25V DC output current 5.0 mA > 4 kV

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 4.2 DC and AC Operating Range

**ESD** protection

Table 4-1. DC and AC Operating Range

| AT25512                      |                              |                |

|------------------------------|------------------------------|----------------|

| Operating Temperature (Case) | Industrial Temperature Range | -40°C to +85°C |

| V <sub>CC</sub> Power Supply | Low-Voltage Grade            | 1.8V to 5.5V   |

#### 4.3 **DC Characteristics**

Table 4-2. DC Characteristics(1)

| Parameter       | Symbol           | Minimum | Typical | Maximum | Units | Conditions                                                  |

|-----------------|------------------|---------|---------|---------|-------|-------------------------------------------------------------|

| Supply Voltage  | V <sub>CC1</sub> | 1.8     | _       | 5.5     | V     |                                                             |

| Supply Voltage  | V <sub>CC2</sub> | 2.7     | _       | 5.5     | V     |                                                             |

| Supply Voltage  | V <sub>CC3</sub> | 4.5     | _       | 5.5     | V     |                                                             |

| Supply Current  | I <sub>CC1</sub> | _       | 9.0     | 10.0    | mA    | V <sub>CC</sub> = 5.0V at 20 MHz,<br>SO = Open, Read        |

| Supply Current  | I <sub>CC2</sub> | _       | 5.0     | 7.0     | mA    | V <sub>CC</sub> = 5.0V at 10 MHz,<br>SO = Open, Read, Write |

| Supply Current  | I <sub>CC3</sub> | _       | 2.2     | 3.5     | mA    | V <sub>CC</sub> = 5.0V at 1 MHz,<br>SO = Open, Read, Write  |

| Standby Current | I <sub>SB1</sub> | _       | 0.2     | 3.0     | μA    | $V_{CC} = 1.8V, \overline{CS} = V_{CC}$                     |

| Standby Current | I <sub>SB2</sub> | _       | 0.5     | 3.0     | μA    | $V_{CC} = 2.7V, \overline{CS} = V_{CC}$                     |

| Standby Current | I <sub>SB3</sub> | _       | 2.0     | 5.0     | μA    | $V_{CC} = 5.0V$ , $\overline{CS} = V_{CC}$                  |

| Input Leakage   | I <sub>IL</sub>  | -3.0    | _       | 3.0     | μA    | $V_{IN} = 0V$ to $V_{CC}$                                   |

| continued              |                                |                       |         |                       |       |                                                                                        |                           |  |

|------------------------|--------------------------------|-----------------------|---------|-----------------------|-------|----------------------------------------------------------------------------------------|---------------------------|--|

| Parameter              | Symbol                         | Minimum               | Typical | Maximum               | Units | Conditions                                                                             |                           |  |

| Output Leakage         | I <sub>OL</sub>                | -3.0                  | _       | 3.0                   | μA    | $V_{IN} = 0V \text{ to } V_{CC},$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ |                           |  |

| Input<br>Low-Voltage   | V <sub>IL</sub> <sup>(2)</sup> | -1.0                  | _       | V <sub>CC</sub> x 0.3 | V     |                                                                                        |                           |  |

| Input<br>High-Voltage  | V <sub>IH</sub> <sup>(2)</sup> | V <sub>CC</sub> x 0.7 | _       | V <sub>CC</sub> + 0.5 | V     |                                                                                        |                           |  |

| Output<br>Low-Voltage  | V <sub>OL1</sub>               | _                     | _       | 0.4                   | V     | 3.6V ≤ V <sub>CC</sub> ≤ 5.5V                                                          | I <sub>OL</sub> = 3.0 mA  |  |

| Output<br>High-Voltage | V <sub>OH1</sub>               | V <sub>CC</sub> - 0.8 | _       | _                     | V     | 3.6V ≤ V <sub>CC</sub> ≤ 5.5V                                                          | I <sub>OH</sub> = -1.6 mA |  |

| Output<br>Low-Voltage  | V <sub>OL2</sub>               | _                     | _       | 0.2                   | V     | 1.8V ≤ V <sub>CC</sub> ≤ 3.6V                                                          | I <sub>OL</sub> = 0.15 mA |  |

| Output<br>High-Voltage | V <sub>OH2</sub>               | V <sub>CC</sub> - 0.2 | _       | _                     | V     | 1.8V ≤ V <sub>CC</sub> ≤ 3.6V                                                          | I <sub>OH</sub> = -100 μA |  |

#### Notes:

- 1. Applicable over recommended operating range from:  $T_A = -40^{\circ}\text{C}$  to +85°C,  $V_{CC} = 1.8\text{V}$  to 5.5V (unless otherwise noted).

- 2.  $V_{IL}$  min. and  $V_{IH}$  max. are reference only and are not tested.

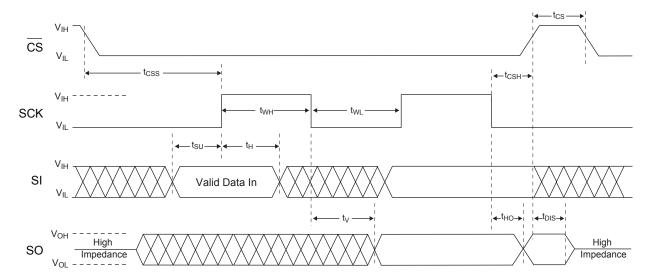

### 4.4 AC Characteristics

Table 4-3. AC Characteristics<sup>(1)</sup>

| Parameter           | Symbol           | Minimum | Maximum | Units | Conditions                     |

|---------------------|------------------|---------|---------|-------|--------------------------------|

|                     |                  | 0       | 20      | MHz   | V <sub>CC</sub> = 4.5V to 5.5V |

| SCK Clock Frequency | f <sub>SCK</sub> | 0       | 10      | MHz   | V <sub>CC</sub> = 2.7V to 5.5V |

|                     |                  | 0       | 5       | MHz   | V <sub>CC</sub> = 1.8V to 5.5V |

|                     |                  | _       | 2000    | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| Input Rise Time     | t <sub>RI</sub>  | _       | 2000    | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                     |                  | _       | 2000    | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                     |                  | _       | 2000    | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| Input Fall Time     | t <sub>FI</sub>  | _       | 2000    | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                     |                  | _       | 2000    | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                     |                  | 20      | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| SCK High Time       | t <sub>WH</sub>  | 40      | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                     |                  | 80      | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                     |                  | 20      | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| SCK Low Time        | t <sub>WL</sub>  | 40      | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                     |                  | 80      | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

| continued             |                  |         |         |       |                                |

|-----------------------|------------------|---------|---------|-------|--------------------------------|

| Parameter             | Symbol           | Minimum | Maximum | Units | Conditions                     |

|                       |                  | 100     | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| CS High Time          | t <sub>CS</sub>  | 100     | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 200     | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | 100     | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| CS Setup Time         | t <sub>CSS</sub> | 100     | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 200     | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | 100     | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| CS Hold Time          | t <sub>CSH</sub> | 100     | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 200     | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | 5       | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| Data In Setup Time    | t <sub>SU</sub>  | 10      | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 20      | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | 5       | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| Data In Hold Time     | t <sub>H</sub>   | 10      | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 20      | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | 5       | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

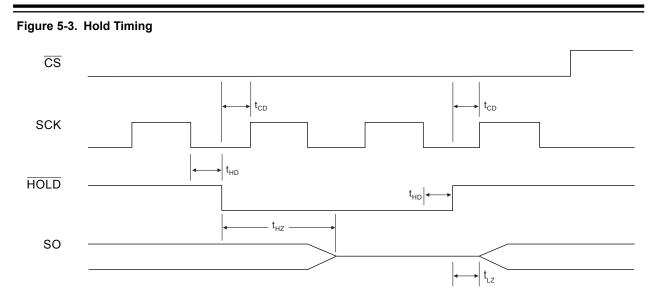

| HOLD Setup Time       | t <sub>HD</sub>  | 10      | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 20      | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       | t <sub>CD</sub>  | 5       | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| HOLD Hold Time        |                  | 10      | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 20      | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | 0       | 20      | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| Output Valid          | t <sub>V</sub>   | 0       | 40      | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 0       | 80      | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | 0       | _       | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| Output Hold Time      | t <sub>HO</sub>  | 0       | _       | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 0       | _       | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | 0       | 25      | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| HOLD to Output Low Z  | t <sub>LZ</sub>  | 0       | 50      | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | 0       | 100     | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

|                       |                  | _       | 25      | ns    | V <sub>CC</sub> = 4.5V to 5.5V |

| HOLD to Output High Z | t <sub>HZ</sub>  | _       | 50      | ns    | V <sub>CC</sub> = 2.7V to 5.5V |

|                       |                  | _       | 100     | ns    | V <sub>CC</sub> = 1.8V to 5.5V |

| continued           |                  |         |         |       |                                |  |

|---------------------|------------------|---------|---------|-------|--------------------------------|--|

| Parameter           | Symbol           | Minimum | Maximum | Units | Conditions                     |  |

|                     | t <sub>DIS</sub> | _       | 25      | ns    | V <sub>CC</sub> = 4.5V to 5.5V |  |

| Output Disable Time |                  | _       | 50      | ns    | V <sub>CC</sub> = 2.7V to 5.5V |  |

|                     |                  | _       | 100     | ns    | V <sub>CC</sub> = 1.8V to 5.5V |  |

|                     | t <sub>WC</sub>  | _       | 5       | ms    | V <sub>CC</sub> = 4.5V to 5.5V |  |

| Write Cycle Time    |                  | _       | 5       | ms    | V <sub>CC</sub> = 2.7V to 5.5V |  |

|                     |                  | _       | 5       | ms    | V <sub>CC</sub> = 1.8V to 5.5V |  |

#### Note:

1. Applicable over recommended operating range from  $T_A$  = -40°C to +85°C,  $V_{CC}$  = As Specified,  $C_L$  = 1 TTL Gate and 30 pF (unless otherwise noted).

### 4.5 SPI Synchronous Data Timing

### 4.6 Electrical Specifications

### 4.6.1 Power-Up Requirements and Reset Behavior

During a power-up sequence, the  $V_{CC}$  supplied to the AT25512 should monotonically rise from GND to the minimum  $V_{CC}$  level (as specified in Table 4-1), with a slew rate no faster than 0.1 V/ $\mu$ s.

### 4.6.1.1 Device Reset

To prevent inadvertent write operations or any other spurious events from occurring during a power-up sequence, the AT25512 includes a Power-on Reset (POR) circuit. Upon power-up, the device will not respond to any instructions until the  $V_{CC}$  level crosses the internal voltage threshold ( $V_{POR}$ ) that brings the device out of Reset and into Standby mode.

The system designer must ensure the instructions are not sent to the device until the  $V_{CC}$  supply has reached a stable value greater than or equal to the minimum  $V_{CC}$  level. Additionally, once the  $V_{CC}$  is greater than or equal to the minimum  $V_{CC}$  level, the bus host must wait at least  $t_{PUP}$  before sending the first instruction to the device. See Table 4-4 for the values associated with these power-up parameters.

Table 4-4. Power-Up Conditions<sup>(1)</sup>

| Symbol            | Parameter                                                                               | Min. | Max. | Units |

|-------------------|-----------------------------------------------------------------------------------------|------|------|-------|

| t <sub>PUP</sub>  | Time required after V <sub>CC</sub> is stable before the device can accept instructions | 100  | _    | μs    |

| V <sub>POR</sub>  | Power-on Reset Threshold Voltage                                                        | _    | 1.5  | V     |

| t <sub>POFF</sub> | Minimum time at V <sub>CC</sub> = 0V between power cycles                               | 500  | _    | ms    |

#### Note:

1. These parameters are characterized but they are not 100% tested in production.

If an event occurs in the system where the  $V_{CC}$  level supplied to the AT25512 drops below the maximum  $V_{POR}$  level specified, it is recommended that a full-power cycle sequence be performed by first driving the  $V_{CC}$  pin to GND in less than 1 ms, waiting at least the minimum  $t_{POFF}$  time and then performing a new power-up sequence in compliance with the requirements defined in this section.

### 4.6.2 Pin Capacitance

Table 4-5. Pin Capacitance<sup>(1,2)</sup>

| Symbol           | Test Condition                            | Max. | Units | Conditions            |

|------------------|-------------------------------------------|------|-------|-----------------------|

| C <sub>OUT</sub> | Output Capacitance (SO)                   | 8    | pF    | V <sub>OUT</sub> = 0V |

| C <sub>IN</sub>  | Input Capacitance (CS, SCK, SI, WP, HOLD) |      | pF    | V <sub>IN</sub> = 0V  |

#### Notes:

- 1. This parameter is characterized but is not 100% tested in production.

- Applicable over recommended operating range from: T<sub>A</sub> = 25°C, f<sub>SCK</sub> = 1.0 MHz, V<sub>CC</sub> = 5.0V (unless otherwise noted).

#### 4.6.3 EEPROM Cell Performance Characteristics

Table 4-6. EEPROM Cell Performance Characteristics

| Operation                      | Test Condition                                   | Min.      | Max. | Units        |

|--------------------------------|--------------------------------------------------|-----------|------|--------------|

| Write Endurance <sup>(1)</sup> | $T_A = 25$ °C, $V_{CC} = 5.0$ V, Page Write mode | 1,000,000 | _    | Write Cycles |

| Data Retention <sup>(1)</sup>  | T <sub>A</sub> = 55°C                            | 100       | _    | Years        |

#### Note:

1. Performance is determined through characterization and the qualification process.

#### 4.6.4 Software Reset

The SPI interface of the AT25512 can be reset by toggling the  $\overline{CS}$  input. If the  $\overline{CS}$  line is already in the Active state, it must complete a transition from the Inactive state ( $\geq V_{IH}$ ) to the Active state ( $\leq V_{IL}$ ) and then back to the Inactive state ( $\geq V_{IH}$ ) without sending clocks on the SCK line. Upon completion of this sequence, the device will be ready to receive a new opcode on the SI line.

### 4.6.5 Device Default State at Power-Up

The AT25512 default state upon power-up consists of:

- · Standby Power mode

- A high-to-low-level transition on  $\overline{\text{CS}}$  is required to enter Active state

- Write Enable Latch (WEL) bit in the STATUS register = 0

- Ready/Busy bit in the STATUS register = 0, indicating the device is ready to accept a new command

- · Device is not selected

- · Not in Hold condition

- WPEN, BP1 and BP0 bits in the STATUS register are unchanged from their previous state due to the fact that they are nonvolatile values

### 4.6.6 Device Default Condition

The AT25512 is shipped from Microchip to the customer with the EEPROM array set to an all FFh data pattern (logic '1' state). The Write-Protect Enable bit in the STATUS register is set to logic '0' and the Block Write-Protect bits in the STATUS register are set to logic '0'.

## 5. Device Operation

The AT25512 is controlled by a set of instructions that are sent from a host controller, commonly referred to as the SPI Host. The SPI Host communicates with the AT25512 via the SPI bus which is comprised of four signal lines: Chip Select ( $\overline{CS}$ ), Serial Data Clock (SCK), Serial Data Input (SI) and Serial Data Output (SO).

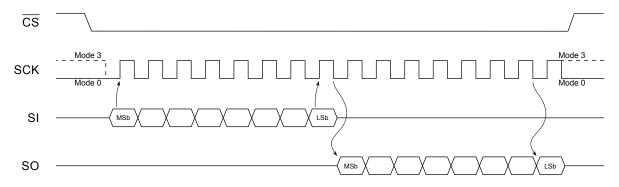

The SPI protocol defines a total of four modes of operation (Mode 0, 1, 2 or 3) with each mode differing in respect to the SCK polarity and phase and how the polarity and phase control the flow of data on the SPI bus. The AT25512 supports the two most common modes, SPI Modes 0 and 3. With SPI Modes 0 and 3, data is always latched in on the rising edge of SCK and always output on the falling edge of SCK. The only difference between SPI Modes 0 and 3 is the polarity of the SCK signal when in the Inactive state (when the SPI Host is in Standby mode and not transferring any data). SPI Mode 0 is defined as a low SCK while  $\overline{\text{CS}}$  is not asserted (at  $V_{\text{CC}}$ ) and SPI Mode 3 has SCK high in the Inactive state. The SCK Idle state must match when the  $\overline{\text{CS}}$  is deasserted both before and after the communication sequence in SPI Mode 0 and 3. The figures in this document depict Mode 0 with a solid line on SCK while  $\overline{\text{CS}}$  is inactive and Mode 3 with a dotted line.

Figure 5-1. SPI Mode 0 and Mode 3

## 5.1 Interfacing the AT25512 on the SPI Bus

Communication to and from the AT25512 must be initiated by the SPI Host device, such as a microcontroller. The SPI Host device must generate the serial clock for the AT25512 on the Serial Data Clock (SCK) pin. The AT25512 always operates as a client due to the fact that the SCK is always an input.

#### 5.1.1 Selecting the Device

The AT25512 is selected when the Chip Select ( $\overline{\text{CS}}$ ) pin is low. When the device is not selected, data will not be accepted via the Serial Data Input (SI) pin, and the Serial Data Output (SO) pin will remain in a high-impedance state.

### 5.1.2 Sending Data to the Device

The AT25512 uses the SI pin to receive information. All instructions, addresses and data input bytes are clocked into the device with the Most Significant bit (MSb) first. The SI pin samples on the first rising edge of the SCK line after the  $\overline{CS}$  has been asserted.

### 5.1.3 Receiving Data from the Device

Data output from the device is transmitted on the SO pin, with the MSb output first. The SO data is latched on the first falling edge of SCK after the instruction has been clocked into the device, such as the Read from Memory Array (READ) and Read STATUS Register (RDSR) instructions. See Read Sequence for more details.

### 5.2 Device Opcodes

### 5.2.1 Serial Opcode

After the device is selected by driving  $\overline{CS}$  low, the first byte will be received on the SI pin. This byte contains the opcode that defines the operation to be performed. Refer to Table 6-1 for a list of all opcodes that the AT25512 will respond to.

### 5.2.2 Invalid Opcode

If an invalid opcode is received, no data will be shifted into AT25512 and the SO pin will remain in a high-impedance state until the falling edge of  $\overline{CS}$  is detected again. This will reinitialize the serial communication.

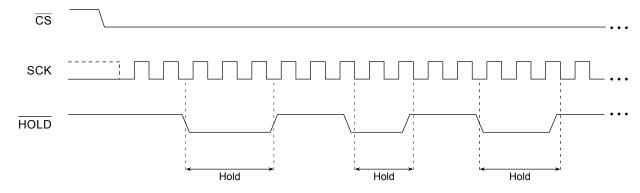

### 5.3 Hold Function

The Suspend Serial Input  $(\overline{HOLD})$  pin is used to pause the serial communication with the device without having to stop or reset the clock sequence. The Hold mode, however, does not have an effect on the internal write cycle. Therefore, if a write cycle is in progress, asserting the  $\overline{HOLD}$  pin will not pause the operation and the write cycle will continue to completion.

The Hold mode can only be entered while the  $\overline{CS}$  pin is asserted. The Hold mode is activated by asserting the  $\overline{HOLD}$  pin during the SCK low pulse. If the  $\overline{HOLD}$  pin is asserted during the SCK high pulse, then the Hold mode will not be started until the beginning of the next SCK low pulse. The device will remain in the Hold mode as long as the  $\overline{HOLD}$  pin and  $\overline{CS}$  pin are asserted.

While in Hold mode, the SO pin will be in a high-impedance state. In addition, both the SI pin and the SCK pin will be ignored. The Write-Protect (WP) pin, however, can still be asserted or deasserted while in the Hold mode.

To end the Hold mode and resume serial communication, the  $\overline{HOLD}$  pin must be deasserted during the SCK low pulse. If the  $\overline{HOLD}$  pin is deasserted during the SCK high pulse, then the Hold mode will not end until the beginning of the next SCK low pulse.

If the  $\overline{\text{CS}}$  pin is deasserted while the  $\overline{\text{HOLD}}$  pin is still asserted, then any operation that may have been started will be aborted and the device will reset the WEL bit in the STATUS register back to the logic '0' state.

Figure 5-2. Hold Mode

### 5.4 Write Protection

The Write-Protect  $(\overline{WP})$  pin will allow normal read and write operations when held high. When the  $\overline{WP}$  pin is brought low and WPEN bit is a logic '1', all write operations to the STATUS register are inhibited. The  $\overline{WP}$  pin going low while  $\overline{CS}$  is still low will interrupt a Write STATUS Register (WRSR). If the internal write cycle has already been initiated,  $\overline{WP}$  going low will have no effect on any write operation to the STATUS register. The  $\overline{WP}$  pin function is blocked when the WPEN bit in the STATUS register is a logic '0'. This will allow the user to install the AT25512 device in a system with the  $\overline{WP}$  pin tied to ground and still be able to write to the STATUS register. All  $\overline{WP}$  pin functions are enabled when the WPEN bit is set to a logic '1'.

## 6. Device Commands and Addressing

The AT25512 is designed to interface directly with the synchronous Serial Peripheral Interface (SPI). The AT25512 utilizes an 8-bit instruction register. The list of instructions and their operation codes are contained in Table 6-1. All instructions, addresses and data are transferred with the MSb first and start with a high-to-low  $\overline{CS}$  transition.

Table 6-1. Instruction Set for the AT25512

| Instruction Name | Instruction Format | Operates On     | Operation Description          |

|------------------|--------------------|-----------------|--------------------------------|

| WREN             | 0000 X110          | STATUS Register | Set Write Enable Latch (WEL)   |

| WRDI             | 0000 X100          | STATUS Register | Reset Write Enable Latch (WEL) |

| RDSR             | 0000 X101          | STATUS Register | Read STATUS Register           |

| WRSR             | 0000 X001          | STATUS Register | Write STATUS Register          |

| READ             | 0000 X011          | Memory Array    | Read from Memory Array         |

| WRITE            | 0000 X010          | Memory Array    | Write to Memory Array          |

## 6.1 STATUS Register Bit Definition and Function

The AT25512 includes an 8-bit STATUS register. The STATUS register bits modulate various features of the device as shown in Table 6-2 and Table 6-3. These bits can be changed by specific instructions that are detailed in the following sections.

Table 6-2. STATUS Register Format

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0   |

|-------|-------|-------|-------|-------|-------|-------|---------|

| WPEN  | Х     | Х     | Χ     | BP1   | BP0   | WEL   | RDY/BSY |

Table 6-3. STATUS Register Bit Definition

| Bit |                            | Name                    | Туре  |                                             | Description                                            |

|-----|----------------------------|-------------------------|-------|---------------------------------------------|--------------------------------------------------------|

| 7   | WPEN                       | Write-Protect Enable    | R/W   | 0                                           | See Table 6-5 (Factory Default)                        |

| ,   | VVFEIN                     | Wille-Flotect Ellable   | IX/VV | 1                                           | See Table 6-5 (Factory Default)                        |

| 6:4 | RFU                        | Reserved for Future Use | R     | 0                                           | Reads as zeros when the device is not in a write cycle |

| 0.4 | KFU                        | Reserved for Future Ose | K     | 1                                           | Reads as ones when the device is in a write cycle      |

|     |                            |                         |       | 00                                          | No array write protection (Factory Default)            |

| 2.2 | BP1 Block Write Protection | Plack Write Protection  | R/W   | 01                                          | Quarter array write protection (see Table 6-4)         |

| 3.2 |                            | 17/77                   | 10    | Half array write protection (see Table 6-4) |                                                        |

|     |                            |                         |       | 11                                          | Entire array write protection (see Table 6-4)          |

| 1   | WEL                        | Write Enable Lateb      | R     | 0                                           | Device is not write enabled (Power-up Default)         |

| •   | VVEL                       | /EL Write Enable Latch  |       | 1                                           | Device is write enabled                                |

| 0   | DDV/DCV Doods/Duos Chatris |                         | R     | 0                                           | Device is ready for a new sequence                     |

| U   | RDY/BSY                    | Ready/Busy Status       | K     | 1                                           | Device is busy with an internal operation              |

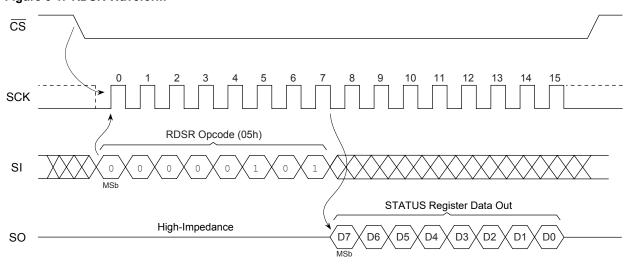

### 6.2 Read STATUS Register (RDSR)

The Read STATUS Register (RDSR) instruction provides access to the STATUS register. The ready/busy and write enable status of the device can be determined by the RDSR instruction. Similarly, the Block Write-Protect (BP1, BP0) bits indicate the extent of memory array protection employed. The STATUS register is read by asserting the  $\overline{\text{CS}}$  pin, followed by sending in a 05h opcode on the SI pin. Upon completion of the opcode, the device will return the 8-bit STATUS register value on the SO pin.

Figure 6-1. RDSR Waveform

### 6.3 Write Enable (WREN) and Write Disable (WRDI)

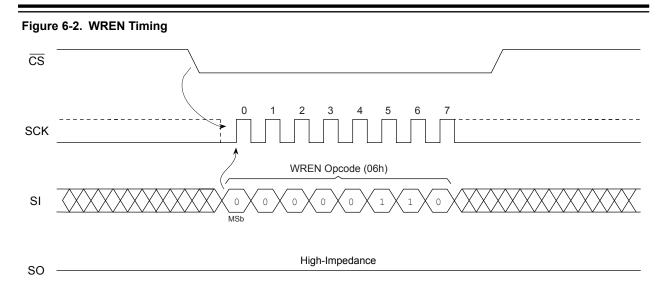

Enabling and disabling writing to the STATUS register and EEPROM array is accomplished through the Write Enable (WREN) instruction and the Write Disable (WRDI) instruction. These functions change the status of the WEL bit in the STATUS register.

### 6.3.1 Write Enable Instruction (WREN)

The Write Enable Latch (WEL) bit of the STATUS register must be set to a logic '1' prior to each Write STATUS Register (WRSR) and Write to Memory Array (WRITE) instructions. This is accomplished by sending a WREN (06h) instruction to the AT25512. First, the  $\overline{CS}$  pin is driven low to select the device and then a WREN instruction is clocked in on the SI pin. Then the  $\overline{CS}$  pin can be driven high and the WEL bit will be updated in the STATUS register to a logic '1'. The device will power-up in the Write Disable state (WEL = 0).

### 6.3.2 Write Disable Instruction (WRDI)

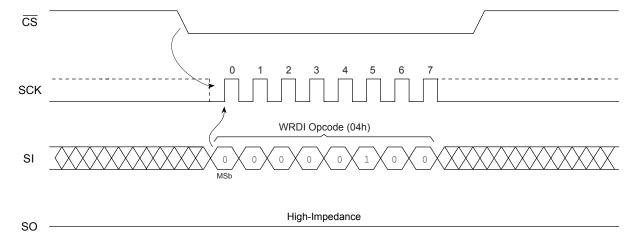

To protect the device against inadvertent writes, the Write Disable (WRDI) instruction (opcode 04h) disables all programming modes by setting the WEL bit to a logic '0'. The WRDI instruction is independent of the status of the  $\overline{\text{WP}}$  pin.

Figure 6-3. WRDI Timing

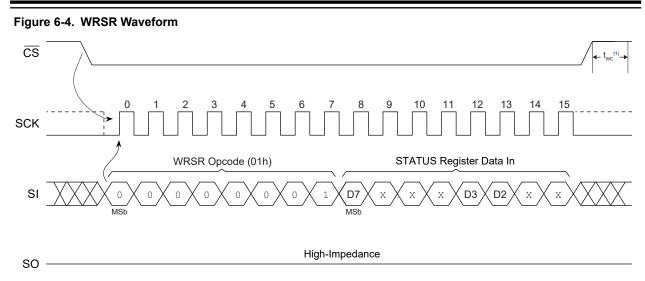

## 6.4 Write STATUS Register (WRSR)

The Write STATUS Register (WRSR) instruction enables the SPI Host to change selected bits of the STATUS register. Before a WRSR instruction can be initiated, a WREN instruction must be executed to set the WEL bit to logic '1'. Upon completion of a WREN instruction, a WRSR instruction can be executed.

**Note:** The WRSR instruction has no effect on bit 6, bit 5, bit 4, bit 1 and bit 0 of the STATUS register. Only bit 7, bit 3 and bit 2 can be changed via the WRSR instruction. These modifiable bits are the Write-Protect Enable (WPEN) and Block Protect (BP1, BP0) bits. These three bits are nonvolatile bits that have the same properties and functions as regular EEPROM cells. Their values are retained while power is removed from the device.

The AT25512 will not respond to commands other than a RDSR after a WRSR instruction until the self-timed internal write cycle has completed. When the write cycle is completed, the WEL bit in the STATUS register is reset to logic '0'.

#### Note:

1. This instruction initiates a self-timed internal write cycle (t<sub>WC</sub>) on the rising edge of  $\overline{CS}$  after a valid sequence.

#### 6.4.1 Block Write-Protect Function

The WRSR instruction allows the user to select one of four possible combinations as to how the memory array will be inhibited from writing through changing the Block Write-Protect bits (BP1, BP0). The four levels of array protection are:

- · None of the memory array is protected.

- Upper quarter (1/4) address range is write-protected meaning the highest order address bits are read-only.

- Upper half (½) address range is write-protected meaning the highest order address bits are read-only.

- · All of the memory array is write-protected meaning all address bits are read-only.

The Block Write Protection levels and corresponding STATUS register control bits are shown in Table 6-4.

Table 6-4. Block Write-Protect Bits

| Level  | STATUS Register Bits |     | Write-Protected/Read-Only Address Range |  |  |

|--------|----------------------|-----|-----------------------------------------|--|--|

|        | BP1                  | BP0 | AT25512                                 |  |  |

| 0      | 0                    | 0   | None                                    |  |  |

| 1(1/4) | 0                    | 1   | C000h-FFFFh                             |  |  |

| 2(1/2) | 1                    | 0   | 8000h-FFFFh                             |  |  |

| 3(All) | 1                    | 1   | 0000h-FFFFh                             |  |  |

#### 6.4.2 Write-Protect Enable Function

The WRSR instruction also allows the user to enable or disable the Write-Protect ( $\overline{\text{WP}}$ ) pin through the use of the Write-Protect Enable (WPEN) bit. When the WPEN bit is set to logic '0', the ability to write the EEPROM array is dictated by the values of the Block Write-Protect (BP1, BP0) bits. The ability to write the STATUS register is controlled by the WEL bit. When the WPEN bit is set to logic '1', the STATUS register is read-only.

Hardware Write Protection is enabled when both the  $\overline{\text{WP}}$  pin is low and the WPEN bit has been set to a logic '1'. When the device is Hardware Write-Protected, writes to the STATUS register, including the Block Write-Protect, WEL and WPEN bits and to the sections in the memory array selected by the Block Write-Protect bits are disabled. When Hardware Write Protection is enabled, writes are only allowed to sections of the memory that are not block-protected.

Hardware Write Protection is disabled when either the  $\overline{\text{WP}}$  pin is high or the WPEN bit is a logic '0'. When Hardware Write Protection is disabled, writes are only allowed to sections of the memory that are not block-protected. Refer to Table 6-5 for additional information.

**Note:** When the WPEN bit is Hardware Write-Protected, it cannot be set back to a logic '0' as long as the  $\overline{\text{WP}}$  pin is held low.

Table 6-5. WPEN Operation

| WPEN | WP Pin | WEL | Protected Blocks | Unprotected Blocks | STATUS Register |

|------|--------|-----|------------------|--------------------|-----------------|

| 0    | Х      | 0   | Protected        | Protected          | Protected       |

| 0    | Х      | 1   | Protected        | Writable           | Writable        |

| 1    | Low    | 0   | Protected        | Protected          | Protected       |

| 1    | Low    | 1   | Protected        | Writable           | Protected       |

| Х    | High   | 0   | Protected        | Protected          | Protected       |

| Х    | High   | 1   | Protected        | Writable           | Writable        |

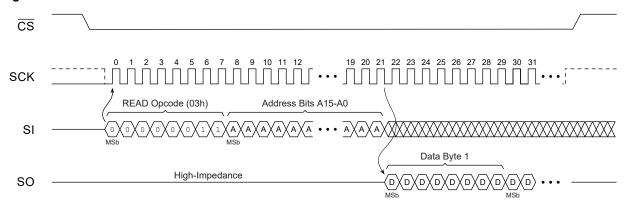

## 7. Read Sequence

Reading the AT25512 via the SO pin requires the following sequence. After the  $\overline{CS}$  line is pulled low to select a device, the READ (03h) instruction is transmitted via the SI line followed by the 16-bit address to be read. Refer to Table 7-1 for the address bits for AT25512.

Table 7-1. AT25512 Address Bits

| Address        | AT25512                         |

|----------------|---------------------------------|

| A <sub>N</sub> | A <sub>15</sub> —A <sub>0</sub> |

Upon completion of the 16-bit address, any data on the SI line will be ignored. The data (D7-D0) at the specified address is then shifted out onto the SO line. If only one byte is to be read, the  $\overline{CS}$  line should be driven high after the data comes out. The read sequence can be continued since the byte address is automatically incremented and data will continue to be shifted out. When the highest-order address bit is reached, the address counter will rollover to the lowest-order address bit allowing the entire memory to be read in one continuous read cycle regardless of the starting address.

Figure 7-1. Read Waveform

## 8. Write Sequence

In order to program the AT25512, two separate instructions must be executed. First, the device *must be write* enabled via the Write Enable (WREN) instruction. Then, one of the two possible write sequences described in this section may be executed.

**Note:** If the device is not Write Enabled (WREN), the device will ignore the WRITE instruction and will return to the standby state when  $\overline{CS}$  is brought high. A new  $\overline{CS}$  assertion is required to re-initiate communication.

The address of the memory location(s) to be programmed must be outside the protected address field location selected by the block write protection level. During an internal write cycle, all commands will be ignored except the RDSR instruction. Refer to Table 8-1 for the address bits for AT25512.

Table 8-1. AT25512 Address Bits

| Address        | AT25512                         |

|----------------|---------------------------------|

| A <sub>N</sub> | A <sub>15</sub> —A <sub>0</sub> |

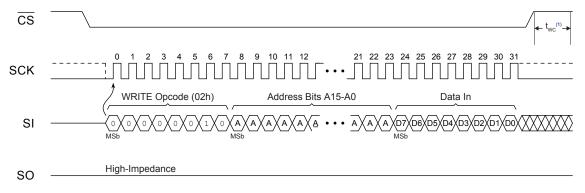

### 8.1 Byte Write

A byte write requires the following sequence and is depicted in Figure 8-1. After the  $\overline{CS}$  line is pulled low to select the device, the WRITE (02h) instruction is transmitted via the SI line followed by the 16-bit address and the data (D7-D0) to be programmed. Programming will start after the  $\overline{CS}$  pin is brought high. The low-to-high transition of the  $\overline{CS}$  pin must occur during the SCK low time (Mode 0) and SCK high time (Mode 3) immediately after clocking in the D0 (LSB) data bit. The AT25512 is automatically returned to the Write Disable state (STATUS register bit WEL = 0) at the completion of a write cycle.

Figure 8-1. Byte Write

#### Note:

This instruction initiates a self-timed internal write cycle (t<sub>WC</sub>) on the rising edge of CS after a valid sequence.

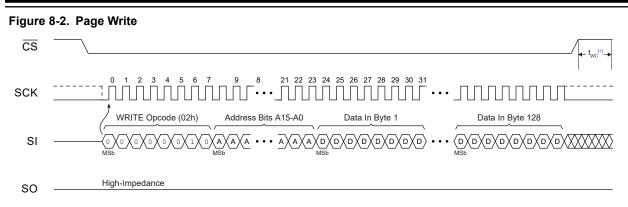

### 8.2 Page Write

A page write sequence allows up to 128 bytes to be written in the same write cycle, provided that all bytes are in the same row of the memory array. Partial page writes of less than 128 bytes are allowed. After each byte of data is received, the seven lowest order address bits are internally incremented following the receipt of each data byte. The higher order address bits are not incremented and retain the memory array page location. If more bytes of data are transmitted that what will fit to the end of that memory row, the address counter will rollover to the beginning of the same row. Nevertheless, creating a rollover event should be avoided as previously loaded data in the page could become unintentionally altered. The AT25512 is automatically returned to the Write Disable state (WEL = 0) at the completion of a write cycle.

#### Note:

1. This instruction initiates a self-timed internal write cycle ( $t_{WC}$ ) on the rising edge of  $\overline{CS}$  after a valid sequence.

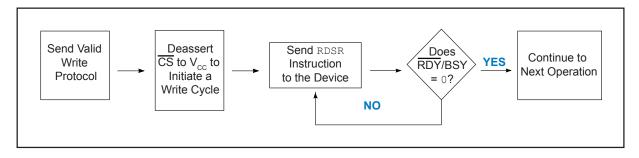

### 8.3 Polling Routine

A polling routine can be implemented to optimize time-sensitive applications that would not prefer to wait the fixed maximum write cycle time (t<sub>WC</sub>). This method allows the application to know immediately when the write cycle has completed to start a subsequent operation.

Once the internally-timed write cycle has started, a polling routine can be initiated. This involves repeatedly sending a Read STATUS Register (RDSR) instruction to determine if the device has completed its self-timed internal write cycle. If the  $\overline{RDY}/BSY$  bit (bit 0 of STATUS register) = 1, the write cycle is still in progress. If bit 0 = 0, the write cycle has ended. If the  $\overline{RDY}/BSY$  bit = 1, repeated RDSR commands can be executed until the  $\overline{RDY}/BSY$  bit = 0, signaling that the device is ready to execute a new instruction. Only the Read STATUS Register (RDSR) instruction is enabled during the write cycle.

Figure 8-3. Polling Flowchart

# 9. Packaging Information

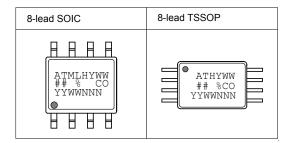

# 9.1 Package Marking Information

## AT25512: Package Marking Information

Note 1: designates pin 1

Note 2: Package drawings are not to scale

| Catalog Nu | Catalog Number Truncation |               |                    |                            |                                        |  |  |  |

|------------|---------------------------|---------------|--------------------|----------------------------|----------------------------------------|--|--|--|

| AT25512    |                           |               | cation Code ##: 5F |                            |                                        |  |  |  |

|            |                           |               |                    |                            |                                        |  |  |  |

| Date Codes | 5                         |               |                    |                            | Voltages                               |  |  |  |

| YY = Year  |                           | Y = Year      |                    | WW = Work Week of Assembly | % = Minimum Voltage                    |  |  |  |

| 16: 2016   | 20: 2020                  | 6: 2016       | 0: 2020            | 02: Week 2                 | L or M: 1.8V min                       |  |  |  |

| 17: 2017   | 21: 2021                  | 7: 2017       | 1: 2021            | 04: Week 4                 |                                        |  |  |  |

| 18: 2018   | 22: 2022                  | 8: 2018       | 2: 2022            |                            |                                        |  |  |  |

| 19: 2019   | 23: 2023                  | 9: 2019       | 3: 2023            | 52: Week 52                |                                        |  |  |  |

| Country of | Origin                    |               | Device             | Grade                      | Atmel Truncation                       |  |  |  |

| CO = Count | ry of Origin              |               | H or U:            | Industrial Grade           | AT: Atmel<br>ATM: Atmel<br>ATML: Atmel |  |  |  |

| Lot Numbe  | Lot Number or Trace Code  |               |                    |                            |                                        |  |  |  |

| NNN = Alph | anumeric Tra              | ice Code (2 C | haracters fo       | or Small Packages)         |                                        |  |  |  |

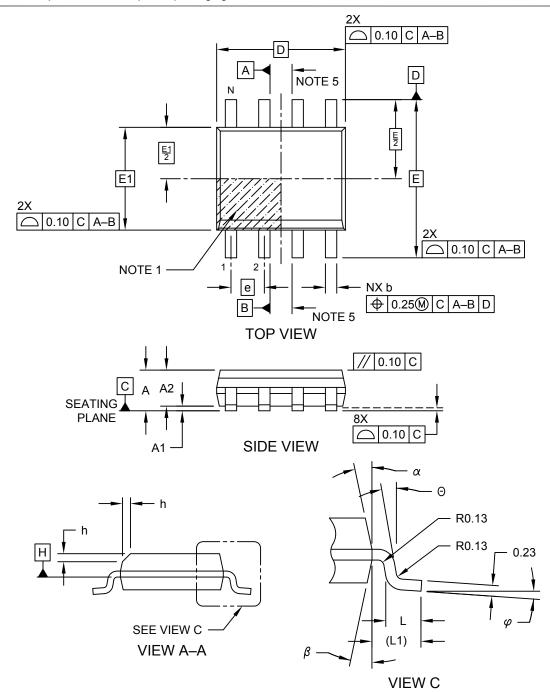

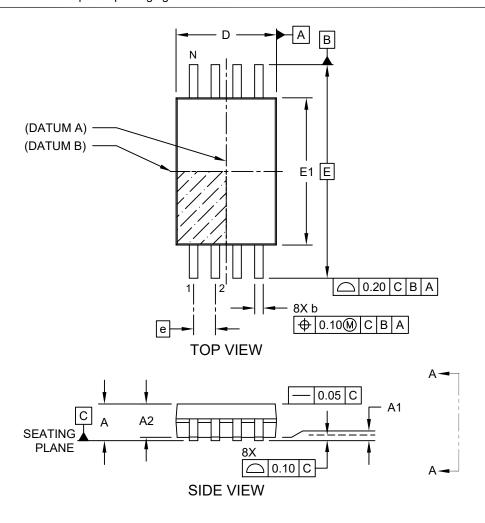

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-057-SN Rev F Sheet 1 of 2

### 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |  |

|--------------------------|-------------|----------|----------|------|--|

| Dimension                | MIN         | NOM      | MAX      |      |  |

| Number of Pins           | N           |          | 8        |      |  |

| Pitch                    | е           |          | 1.27 BSC |      |  |

| Overall Height           | Α           | ı        | ı        | 1.75 |  |

| Molded Package Thickness | A2          | 1.25     | ı        | -    |  |

| Standoff §               | A1          | 0.10     | ı        | 0.25 |  |

| Overall Width            | Е           | 6.00 BSC |          |      |  |

| Molded Package Width     | E1          | 3.90 BSC |          |      |  |

| Overall Length           | D           | 4.90 BSC |          |      |  |

| Chamfer (Optional)       | h           | 0.25     | ı        | 0.50 |  |

| Foot Length              | L           | 0.40     | ı        | 1.27 |  |

| Footprint                | L1          |          | 1.04 REF |      |  |

| Foot Angle               | φ           | 0°       | ı        | 8°   |  |

| Lead Thickness           | С           | 0.17     | ı        | 0.25 |  |

| Lead Width               | b           | 0.31     | -        | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°       | -        | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -        | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-057-SN Rev F Sheet 2 of 2

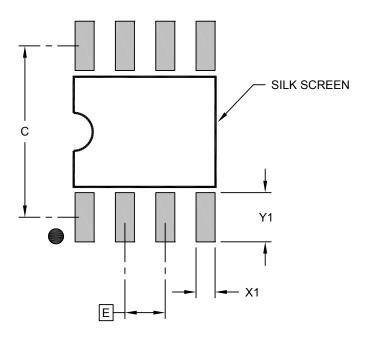

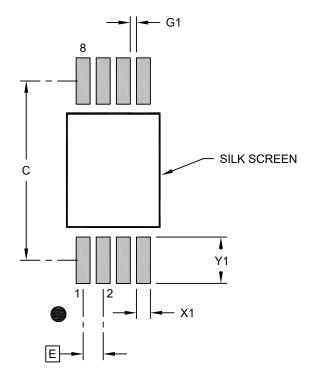

## 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                         | MILLIMETERS |          |      |      |

|-------------------------|-------------|----------|------|------|

| Dimension               | MIN         | NOM      | MAX  |      |

| Contact Pitch E         |             | 1.27 BSC |      |      |

| Contact Pad Spacing     | С           |          | 5.40 |      |

| Contact Pad Width (X8)  | X1          |          |      | 0.60 |

| Contact Pad Length (X8) | Y1          |          |      | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M  $\,$

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2057-SN Rev F

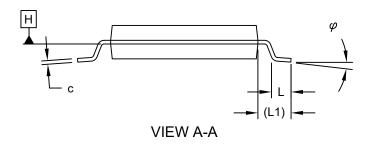

## 8-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-086 Rev C Sheet 1 of 2

### 8-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |

|--------------------------|-------------|----------|----------|------|

| Dimension                | MIN         | NOM      | MAX      |      |

| Number of Pins           | N           |          | 8        |      |

| Pitch                    | е           |          | 0.65 BSC |      |

| Overall Height           | Α           | ı        | -        | 1.20 |

| Molded Package Thickness | A2          | 0.80     | 1.00     | 1.05 |

| Standoff                 | A1          | 0.05     | -        | ı    |

| Overall Width            | Е           |          | 6.40 BSC |      |

| Molded Package Width     | E1          | 4.30     | 4.40     | 4.50 |

| Overall Length           | D           | 2.90     | 3.00     | 3.10 |

| Foot Length              | L           | 0.45     | 0.60     | 0.75 |

| Footprint L1             |             | 1.00 REF |          |      |

| Lead Thickness           | С           | 0.09     | _        | 0.25 |

| Foot Angle               | $\varphi$   | 0°       | 4°       | 8°   |

| Lead Width               | b           | 0.19     | -        | 0.30 |

### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-086 Rev C Sheet 2 of 2

## 8-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                                | MILLIMETERS |          |      |      |

|--------------------------------|-------------|----------|------|------|

| Dimension                      | MIN         | NOM      | MAX  |      |

| Contact Pitch                  |             | 0.65 BSC |      |      |

| Contact Pad Spacing            | С           |          | 5.80 |      |

| Contact Pad Width (X8)         | X1          |          |      | 0.45 |

| Contact Pad Length (X8)        | Y1          |          |      | 1.50 |

| Contact Pad to Center Pad (X6) | G1          | 0.20     |      |      |

#### Notes:

Note:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2086 Rev B

## 10. Revision History

#### Revision B (June 2021)

Replaced "Master" and "Slave" terminology with "Host" and "Client", respectively. Removed UDFN package option. Updated SOIC and TSSOP package drawings.

#### Revision A (June 2019)

Updated to the Microchip template. Microchip DS20006218 replaces Atmel document 5165. Updated Part Marking Information. Added ESD rating. Removed lead finish designation. Added POR recommendations section. Changed Data Retention spec to 100 year. Updated trace code format in package markings. Updated section content throughout for clarification. Updated the SOIC, TSSOP and UDFN package drawings to the Microchip equivalents.

#### Atmel Document 5165 Revision K (January 2017)

Removed waffle pack die sale option. Changed wafer sales note.

#### **Atmel Document 5165 Revision J (January 2015)**

Updated the 8X package outline drawing and the ordering information section.

### Atmel Document 5165 Revision I (July 2013)

Correct ordering code table from 8A2 to 8X package option. Updated footers and disclaimer page.

#### Atmel Document 5165 Revision H (August 2012)

Updated part markings and package drawings. Updated template.

#### Atmel Document 5165 Revision G (September 2009)

Updated Part Marking Scheme.

### Atmel Document 5165 Revision F (March 2009)

Changed Maximum Operating Voltage from 4.3V to 6.25V in the Absolute Maximum Table on page 2.

### Atmel Document 5165 Revision E (August 2008)

Updated for 1.8V - 5.5V operation.

### Atmel Document 5165 Revision D (May 2008)

Added part marking diagram information.

### Atmel Document 5165 Revision C (August 2007)

Changed address bit number to seven on page 9. Removed Preliminary status.

### Atmel Document 5165 Revision B (March 2007)

Changed spacing on table notes. Reworked Figure 4-8. Updated to new template. Change status to Preliminary.

### Atmel Document 5165 Revision A (January 2007)

Initial document release.

## The Microchip Website

Microchip provides online support via our website at <a href="www.microchip.com/">www.microchip.com/</a>. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

quides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

## **Customer Support**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Embedded Solutions Engineer (ESE)

- · Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

llogy Inc Datasheet DS20006218B-page 34

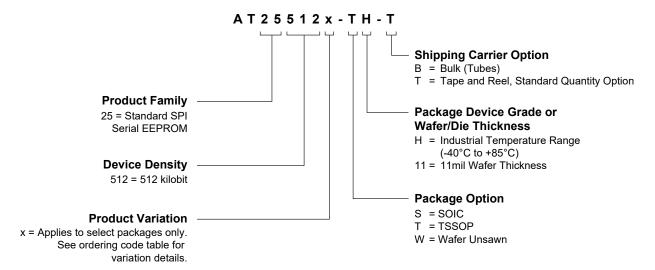

## **Product Identification System**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

### Examples:

| Device        | Package | Package<br>Drawing<br>Code | Package<br>Option | Shipping Carrier<br>Option | Device Grade                   |  |

|---------------|---------|----------------------------|-------------------|----------------------------|--------------------------------|--|

| AT25512N-SH-B | SOIC    | SN                         | S                 | Bulk (Tubes)               |                                |  |

| AT25512N-SH-T | SOIC    | SN                         | S                 | Tape and Reel              | Industrial                     |  |

| AT25512-TH-B  | TSSOP   | ST                         | Т                 | Bulk (Tubes)               | Temperature<br>(-40°C to 85°C) |  |

| AT25512-TH-T  | TSSOP   | ST                         | Т                 | Tape and Reel              |                                |  |

## Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

DS20006218B-page 35 **Datasheet**

## **Legal Notice**

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2019-2021, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-8276-5

© 2019-2021 Microchip Technology Inc. Datasheet DS20006218B-page 36

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

## **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAC                  | 4014/0401510          | 4014/0401510            | FUDORE                |

|---------------------------|-----------------------|-------------------------|-----------------------|

| AMERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                |

| Corporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels        |

| 2355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39  |

| Chandler, AZ 85224-6199   | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393 |

| Tel: 480-792-7200         | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen  |

| Fax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910     |

| Technical Support:        | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829     |

| www.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo       |

| Web Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820   |

| www.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris        |

| Atlanta                   | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20 |

| Duluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79 |

| Tel: 678-957-9614         | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching    |

| Fax: 678-957-1455         | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700     |

| Austin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan        |

| Tel: 512-257-3370         | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400  |

| Boston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn   |

| Westborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400    |

| Tel: 774-760-0087         | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe   |

| Fax: 774-760-0088         | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370    |

| Chicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich      |

| Itasca, IL                | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0  |

| Tel: 630-285-0071         | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44 |

| Fax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim   |

| Dallas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560  |

| Addison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana     |

| Tel: 972-818-7423         | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705   |

| Fax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan         |

| Detroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611   |

| Novi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781   |

| Tel: 248-848-4000         | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova        |

| Houston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286   |

| Tel: 281-894-5983         | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen  |

| Indianapolis              | China - Xiamen        |                         | Tel: 31-416-690399    |

| Noblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340    |

| Tel: 317-773-8323         | China - Zhuhai        |                         | Norway - Trondheim    |

| Fax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388      |

| Tel: 317-536-2380         |                       |                         | Poland - Warsaw       |

| Los Angeles               |                       |                         | Tel: 48-22-3325737    |

| Mission Viejo, CA         |                       |                         | Romania - Bucharest   |

| Tel: 949-462-9523         |                       |                         | Tel: 40-21-407-87-50  |

| Fax: 949-462-9608         |                       |                         | Spain - Madrid        |

| Tel: 951-273-7800         |                       |                         | Tel: 34-91-708-08-90  |

| Raleigh, NC               |                       |                         | Fax: 34-91-708-08-91  |

| Tel: 919-844-7510         |                       |                         | Sweden - Gothenberg   |

| New York, NY              |                       |                         | Tel: 46-31-704-60-40  |

| Tel: 631-435-6000         |                       |                         | Sweden - Stockholm    |

| San Jose, CA              |                       |                         | Tel: 46-8-5090-4654   |

| Tel: 408-735-9110         |                       |                         | UK - Wokingham        |

| Tel: 408-436-4270         |                       |                         | Tel: 44-118-921-5800  |

| Canada - Toronto          |                       |                         | Fax: 44-118-921-5820  |

| Tel: 905-695-1980         |                       |                         | 1 un. 77-110-321-3020 |

| Fax: 905-695-2078         |                       |                         |                       |

| I an. 300-030-2010        |                       |                         |                       |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Microchip:

AT25512N-SH-B AT25512N-SH-T AT25512-TH-T AT25512Y7-YH-T AT25512-TH-B