11 CLAMP GATE

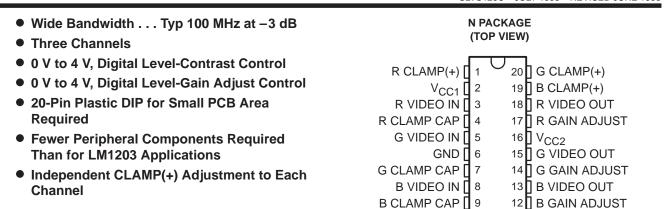

#### description

The TLS1233 is a 100-MHz wide-band video preamplifier system intended for mid-to-high-resolution RGB (red-green-blue) color monitors. Each video amplifier (R, G, and B) contains a gain set for adjusting maximum system gain ( $A_V = 7.8 \text{ V/V}$ ). The TLS1233 provides digital level-operated contrast, brightness, and gain adjustment control. All the control inputs offer high input impedance and an operation range from 0 V to 4 V for easy interface to the serial digital buses. Provided in a 20-pin plastic dual-in-line package (DIP), the TLS1233 integrates most of the external components required to accommodate the video system.

CONTRAST [

The TLS1233 operates from a 12-V supply and contains an internal input bias voltage. Also, the TLS1233 contains the feedback resistor required between output and CLAMP(–) for dc level holding. The device is characterized for operation from 0°C to 70°C.

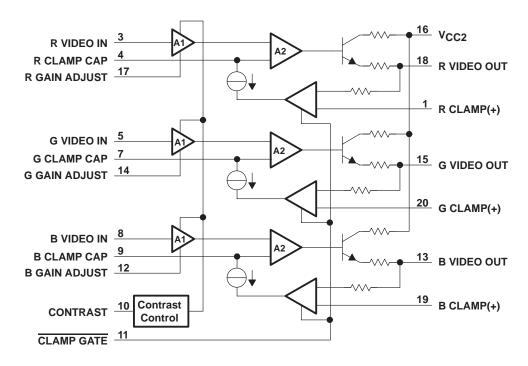

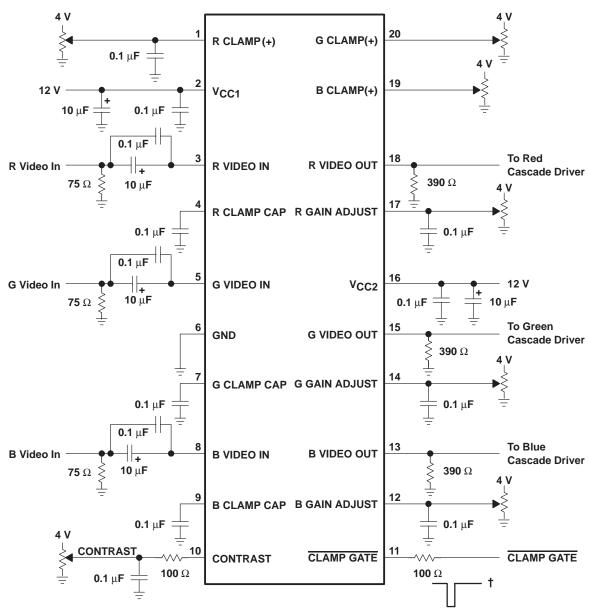

### functional block diagram

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLVS126C - JULY 1995 - REVISED JUNE 1996

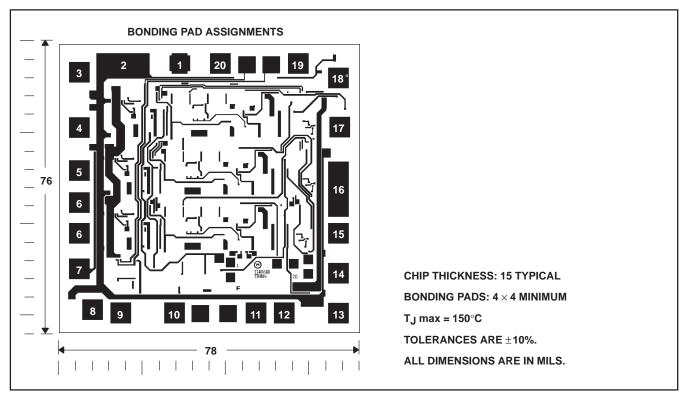

#### TLS1233Y chip information

This chip, when properly assembled, displays characteristics similar to the TLS1233. Thermal compression or ultrasonic bonding may be used on the doped-aluminum bonding pads. The chips may be mounted with conductive epoxy or a gold-silicon preform.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub>                                              | V  |

|------------------------------------------------------------------------------|----|

| Input voltage range, V <sub>I</sub> (see Note 1) 0 V to V <sub>C</sub>       | C  |

| Video output current, I <sub>O</sub> (per channel)                           | ıA |

| Total power dissipation at (or below) 25°C free-air temperature (see Note 2) | W  |

| Operating virtual junction temperature range, T <sub>J</sub>                 | ,C |

| Operating free-air temperature range, T <sub>A</sub>                         | ,C |

| Storage temperature range, T <sub>stq</sub> –65°C to 150°                    | ,C |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                 | ,C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All V<sub>CC</sub> terminals must be externally wired together to prevent internal damage during V<sub>CC</sub> power-on/-off cycles.

- 2. For operation above 25°C free-air temperature, derate linearly from 1.87 W (T<sub>A</sub> = 25°C) to 1.2 W (T<sub>A</sub> = 70°C). This equates to a derating factor of 15 mW/°C.

### recommended operating conditions

|                                                            |                       |     | NOM | MAX | UNIT |

|------------------------------------------------------------|-----------------------|-----|-----|-----|------|

| Supply voltage, V <sub>CC1</sub> and V <sub>CC2</sub>      |                       |     | 12  | 13  | V    |

| High-level input voltage range, CLAMP GATE, VIH            | Clamp comparators off | 2.4 |     | 5   | V    |

| Low-level input voltage range, CLAMP GATE, V <sub>IL</sub> | Clamp comparators on  | 0   |     | 0.8 | V    |

| Operating free-air temperature, T <sub>A</sub>             |                       |     |     | 70  | °C   |

# electrical characteristics at 25°C free-air temperature range, $\overline{\text{CLAMP GATE}} = 0 \text{ V}$ , $\overline{\text{CLAMP(+)}} = 2 \text{ V}$ , $\overline{\text{CONTRAST}} = R$ ,G,B GAIN ADJUST = 4 V, $\overline{\text{V}}_{\text{CC1}} = \overline{\text{V}}_{\text{CC2}} = 12 \text{ V}$ (see Figure 2) (unless otherwise noted)

| PARAMETER        |                                              | ALTERNATE<br>SYMBOL   | TEST CONDITIONS                        | MIN | TYP   | MAX  | UNIT |

|------------------|----------------------------------------------|-----------------------|----------------------------------------|-----|-------|------|------|

| Icc              | Supply current                               |                       | VCC1 + VCC2                            |     | 84    | 94   | mA   |

| V <sub>ref</sub> | Video input reference voltage                |                       | Measure R/G/B video input              | 2.1 | 2.3   | 2.5  | V    |

| Ц                | Contrast and R,G,B GAIN ADJUST input current |                       | Measure CONTRAST,<br>R/G/B GAIN ADJUST |     | -0.5  | -10  | μА   |

| I <sub>IL</sub>  | Clamp gate low input current                 |                       | CLAMP GATE = 0 V                       |     | -0.5  | -2.4 | μΑ   |

| lН               | Clamp gate high input current                |                       | CLAMP GATE = 12 V                      |     | 0.005 | 1    | μΑ   |

|                  | Clamp capacitor charge current               | I <sub>K(chg)</sub>   | R,G,B CLAMP CAP = 0 V                  |     | 1     |      | mA   |

|                  | Clamp capacitor discharge current            | I <sub>K(dschg)</sub> | R,G,B CLAMP CAP = 5 V                  |     | -1    |      | mA   |

| VOL              | Low-level output voltage                     |                       | R,G,B CLAMP CAP = 0 V                  |     | 0.3   |      | V    |

| Vон              | High-level output voltage                    |                       | R,G,B CLAMP CAP = 5 V                  |     | 7.8   |      | V    |

| VO(diff)         | Output voltage difference                    | VO(diff)              | Between any two channels               |     | ±0.5  | ±50  | mV   |

# operating characteristics at 25°C free-air temperature, $\overline{\text{CLAMP GATE}} = 0 \text{ V}$ , $\overline{\text{CLAMP(+)}} = 4 \text{ V}$ , $\overline{\text{CONTRAST}} = R$ , $\overline{\text{G,B GAIN ADJUST}} = 4 \text{ V}$ , $\overline{\text{f_I}} = 10 \text{ kHz}$ , $\overline{\text{V_{CC1}}} = \overline{\text{V_{CC2}}} = 12 \text{ V}$ (unless otherwise noted)

|                     | PARAMETER                                  | ALTERNATE<br>SYMBOL | TEST CONDITI                                        | TIONS MI       | N TYP | MAX | UNIT |

|---------------------|--------------------------------------------|---------------------|-----------------------------------------------------|----------------|-------|-----|------|

| A <sub>V(max)</sub> | Maximum voltage amplification              | A <sub>VMAX</sub>   | CONTRAST = 4 V, V <sub>IPF</sub>                    | P = 700 mV     | 7.8   |     | V/V  |

| AV(mid)             | Midrange voltage amplification             | AVMID               | CONTRAST = 2 V, VIPF                                | P = 700 mV     | 2     |     | V/V  |

|                     | Contrast voltage for minimum amplification | VCONT-LOW           | V <sub>I(PP)</sub> = 1 V, See                       | e Note 3       | 1     |     | V    |

|                     | Amplification match at A <sub>V(max)</sub> | AVmax(diff)         | CONTRAST = 4 V, See                                 | Note 4         | ±0.2  |     | dB   |

|                     | Amplification match at A <sub>V(mid)</sub> | AVmid(diff)         | CONTRAST = 2 V, See                                 | Note 3         | ±0.2  |     | dB   |

|                     | Amplification match at A <sub>V(low)</sub> | AVlow(diff)         | CONTRAST = V <sub>CONT-LC</sub><br>See Note 3 and 4 | OW,            | ±0.2  |     | dB   |

| THD                 | Total harmonic distortion                  |                     | CONTRAST = 1 V, VIPF                                | P = 1 V        | 0.5   |     | %    |

| BW                  | Amplifier bandwidth                        | BW(-3 dB)           | CONTRAST = 4 V,<br>See Notes 5 And 7                |                | 100   |     | MHz  |

|                     | Crosstalk attenuation                      | a <sub>X</sub>      | CONTRAST = 4 V, f = 1<br>See Note 6                 | 10 kHz,        | 60    |     | dB   |

|                     |                                            |                     | CONTRAST = 4 V, See f = 10 MHz,                     | e Notes 6 or 7 | 40    |     | dB   |

|                     | Pulse test for rise time                   | t <sub>r</sub>      |                                                     | AMP(+) = 2 V,  | 3     |     | ns   |

|                     | Pulse test for fall time                   | t <sub>f</sub>      | $I_{O(PP)} = 4 V$ See Note                          | Notes 5 and 7  | 4     |     | ns   |

NOTES: 3. Determine V<sub>CONT-LOW</sub> for -40 dB attenuation of output. Reference to A<sub>V(max)</sub>.

- 4. Measure gain difference between any two amplifiers, V<sub>I(PP)</sub> = 1 V.

- 5. Adjust input frequency from 10 kHz (A<sub>V(max)</sub> reference level) to the -3-dB corner frequency (f -3 dB). V<sub>I(PP)</sub> = 700 mV.

- 6. V<sub>I(PP)</sub> = 700 mV at f = 10 kHz to any amplifier. Measure output levels of the other two undriven amplifiers relative to driven amplifier.

- 7. A special text fixture without a socket and a double-sided full-ground-plane PC board are required.

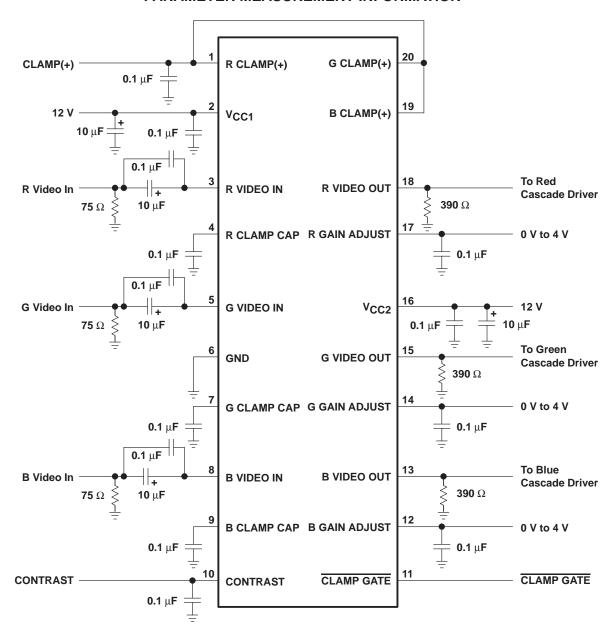

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Test Circuit

#### **APPLICATION INFORMATION**

† Minimum pulse width: 300 ns

Figure 2. Application Circuit

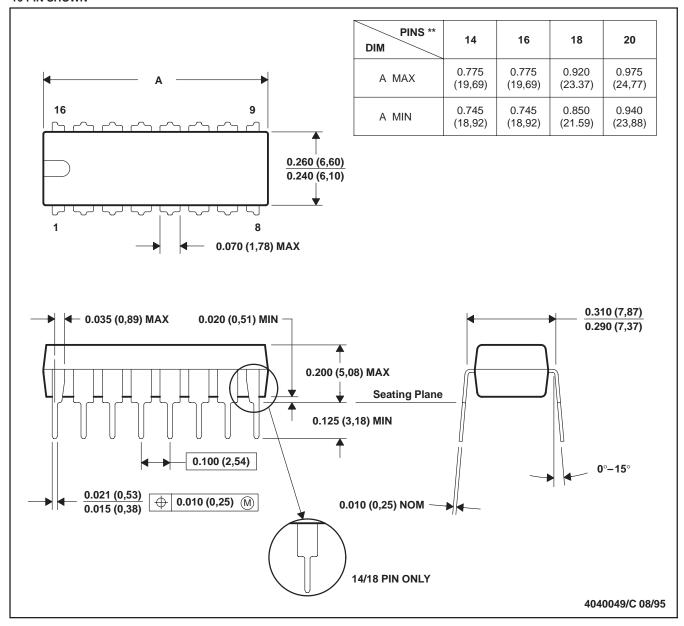

#### **MECHANICAL DATA**

## N (R-PDIP-T\*\*)

#### **16 PIN SHOWN**

#### PLASTIC DUAL-IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-001 (20 pin package is shorter then MS-001.)

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated