# L-ASC10 In-System Programmable Hardware Management Expander Data Sheet

**Data Sheet**

FPGA-DS-02038-2.5

August 2023

#### Disclaimers

Lattice makes no warranty, representation, or guarantee regarding the accuracy of information contained in this document or the suitability of its products for any particular purpose. All information herein is provided AS IS, with all faults and associated risk the responsibility entirely of the Buyer. Buyer shall not rely on any data and performance specifications or parameters provided herein. Products sold by Lattice have been subject to limited testing and it is the Buyer's responsibility to independently determine the suitability of any products and to test and verify the same. No Lattice products should be used in conjunction with mission- or safety-critical or any other application in which the failure of Lattice's product could create a situation where personal injury, death, severe property or environmental damage may occur. The information provided in this document is proprietary to Lattice Semiconductor, and Lattice reserves the right to make any changes to the information in this document or to any products at any time without notice.

## Contents

| 1. | Featu          | ıres                                                                                              |   |

|----|----------------|---------------------------------------------------------------------------------------------------|---|

|    | 1.1.           | Ten Rail Voltage Monitoring and Measurement                                                       | 9 |

|    | 1.2.           | Two Channel Wide-Range Current Monitoring and Measurement                                         | 9 |

|    | 1.3.           | Three Temperature Monitoring and Measurement Channels                                             | 9 |

|    | 1.4.           | Four High-Side MOSFET Drivers                                                                     | 9 |

|    | 1.5.           | Four Precision Trim and Margin Channels                                                           | 9 |

|    | 1.6.           | Nine General Purpose Input / Output                                                               | 9 |

|    | 1.7.           | Non-Volatile Fault Logging                                                                        | 9 |

|    | 1.8.           | In-system Programmable Through I <sup>2</sup> C                                                   |   |

|    | 1.9.           | System Level Support                                                                              |   |

|    | 1.10.          | Applications                                                                                      |   |

| 2. |                | cation Diagram                                                                                    |   |

| 3. |                | ription                                                                                           |   |

| 4. |                | Block Diagram                                                                                     |   |

| 5. |                | nd Switching Characteristics                                                                      |   |

|    | 5.1.           | Absolute Maximum Ratings                                                                          |   |

|    | 5.2.           | Recommended Operating Conditions                                                                  |   |

|    | 5.3.           | Analog Specifications                                                                             |   |

|    | 5.4.           | ESD Performance                                                                                   |   |

|    | 5.5.           | Power-On Reset                                                                                    |   |

|    | 5.6.           | Voltage Monitors                                                                                  |   |

|    | 5.7.           | Current Monitors                                                                                  |   |

|    | 5.8.           | ADC Characteristics                                                                               |   |

|    | 5.9.           | ADC Error Budget Across Entire Operating Temperature Range                                        |   |

|    | 5.10.          | Temperature Monitors                                                                              |   |

|    | 5.11.          | Digital Specifications                                                                            |   |

|    | 5.12.          | High Voltage FET Drivers                                                                          |   |

|    | 5.13.          | Margin/Trim DAC Output Characteristics                                                            |   |

|    | 5.14.          | Fault Log                                                                                         |   |

|    | 5.15.          | Oscillator                                                                                        |   |

|    | 5.16.          | Propagation Delays                                                                                |   |

|    | 5.17.          | FPGA Section sysI/O Single-Ended DC Electrical Characteristics                                    |   |

|    | 5.18.          | ASC Interface (ASC-I/F) Timing Specifications                                                     |   |

| ~  | 5.19.          | I <sup>2</sup> C Port Timing Specifications                                                       |   |

| 6. |                | ry of Operation                                                                                   |   |

|    | 6.1.           | Hardware Management System                                                                        |   |

|    | 6.2.           | Voltage Monitor Inputs                                                                            |   |

|    | 6.3.           | Current Monitor Inputs                                                                            |   |

|    | 6.4.           | High Voltage Monitor                                                                              |   |

|    | 6.5.           | VMON and IMON Measurement with the On-Chip Analog to Digital Converter (ADC)                      |   |

|    | 6.6.           | Calculation                                                                                       |   |

|    | 6.7.           | Temperature Monitor Inputs                                                                        |   |

|    | 6.8.           | Digital Inputs/Outputs                                                                            |   |

|    | 6.9.           | Output Control Block                                                                              |   |

|    | 6.10.<br>6.11  | High Voltage Outputs                                                                              |   |

|    | 6.11.<br>6.12. | Safe State of Digital Outputs                                                                     |   |

|    | 6.12.<br>6.13. | Controlling Power Supply Output Voltage by Trim and Margin Block<br>Digital Closed Loop Trim Mode |   |

|    |                |                                                                                                   |   |

|    | 6.14.<br>6.15  | Details of the Digital to Analog Converter (DAC)                                                  |   |

|    | 6.15.<br>6.16. | Fault Logging and User Tag Memory<br>System Connections                                           |   |

|    |                | Clock Requirements                                                                                |   |

|    | 6.17.          |                                                                                                   |   |

| 60 |

|----|

|    |

| 61 |

| 64 |

|    |

|    |

| 72 |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

|    |

## Figures

| Figure 2.1. Hardware Management Application Block Diagram                                                  |    |

|------------------------------------------------------------------------------------------------------------|----|

| Figure 4.1. ASC Block Diagram                                                                              |    |

| Figure 5.1. ASC Power-On Reset                                                                             |    |

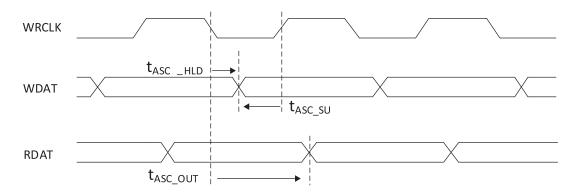

| Figure 5.2. ASC Interface (ASC-I/F) Timing Diagram                                                         | 25 |

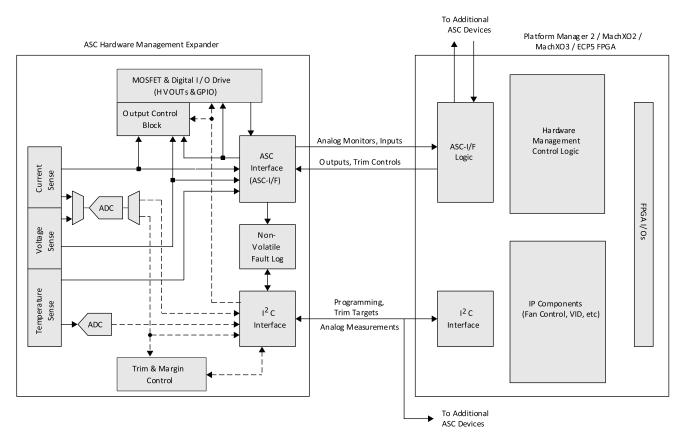

| Figure 6.1. Hardware Management System with ASC Hardware Management Expander                               | 26 |

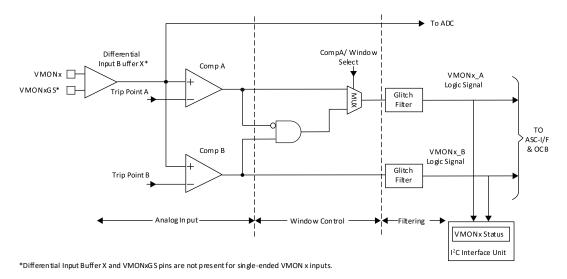

| Figure 6.2. ASC Voltage Monitors                                                                           | 27 |

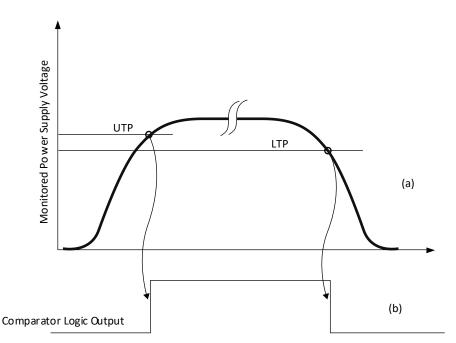

| Figure 6.3. Power Supply Voltage Ramp-up and Ramp-down Waveform and the Resulting Comparator Output (a) ar | ۱d |

| Corresponding to Upper and Lower Trip Points (b)                                                           | 28 |

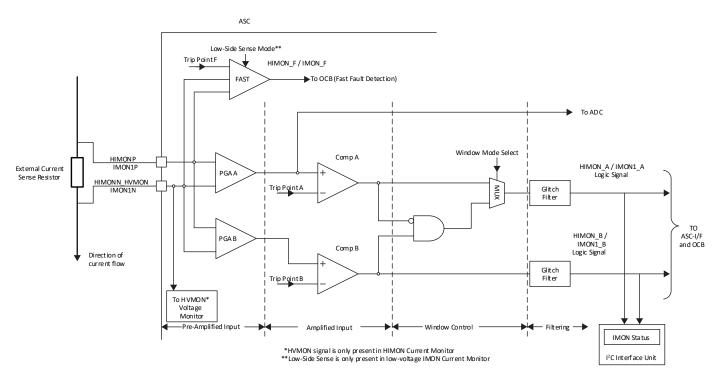

| Figure 6.4. ASC Current Monitor                                                                            | 30 |

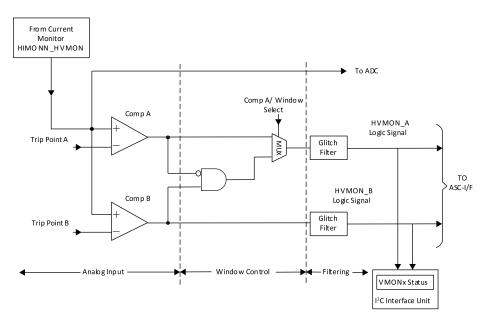

| Figure 6.5. HVMON Monitor Circuit                                                                          |    |

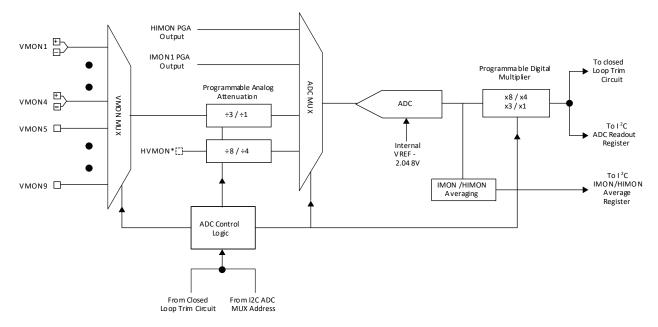

| Figure 6.6. ADC Monitoring VMON and IMON                                                                   | 33 |

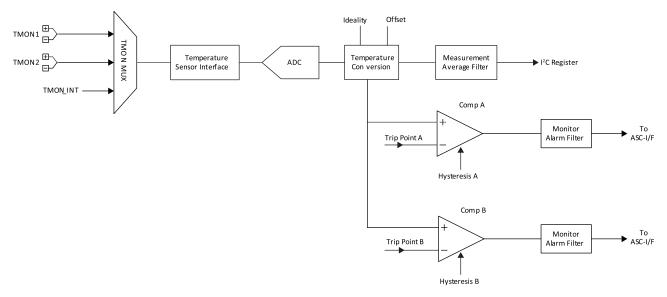

| Figure 6.7. Temperature Monitor                                                                            | 35 |

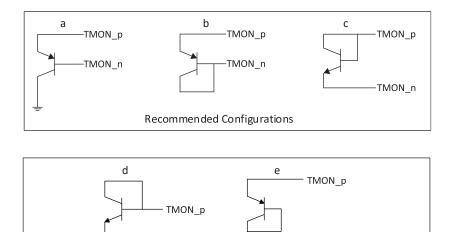

| Figure 6.8. Remote TMON Diode Configurations                                                               | 35 |

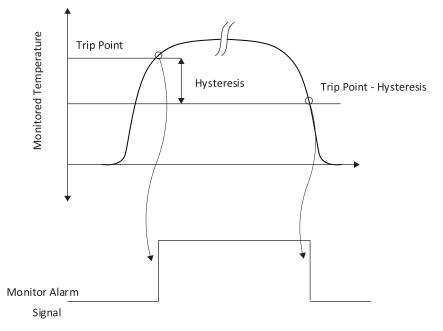

| Figure 6.9. Monitor Alarm Signal Behavior - Overtemperature (OT) Setting                                   | 38 |

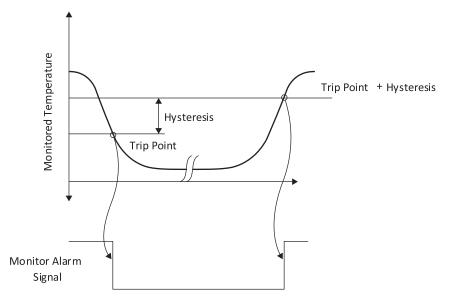

| Figure 6.10. Monitor Alarm Signal Behavior - Undertemperature (UT) Setting                                 |    |

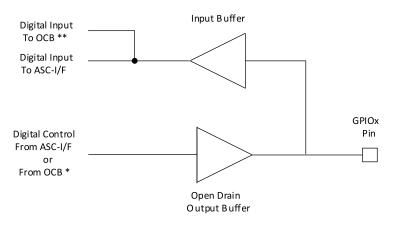

| Figure 6.11. GPIO Block Diagram                                                                            |    |

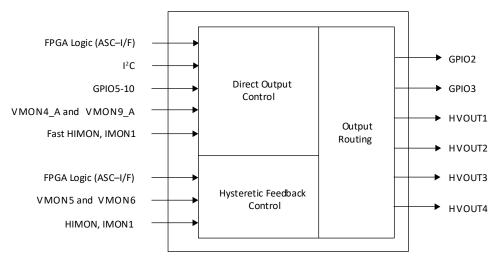

| Figure 6.12. Output Control Block – Simplified Diagram                                                     | 40 |

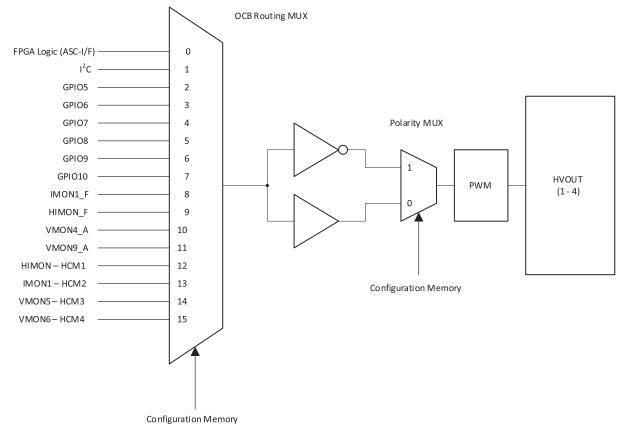

| Figure 6.13. HVOUT Output Routing MUX Block Diagram                                                        |    |

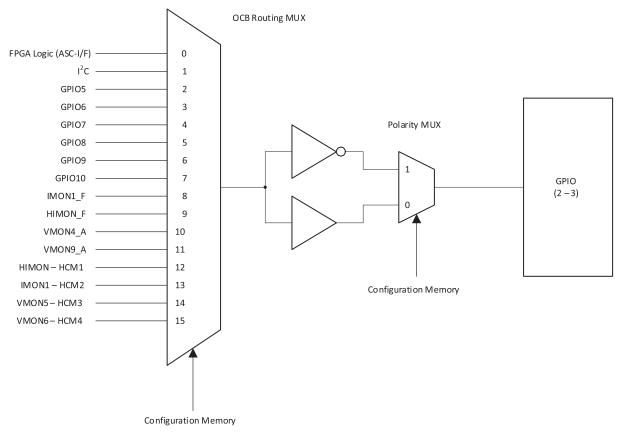

| Figure 6.14. GPIO Output Routing MUX Block Diagram                                                         | 42 |

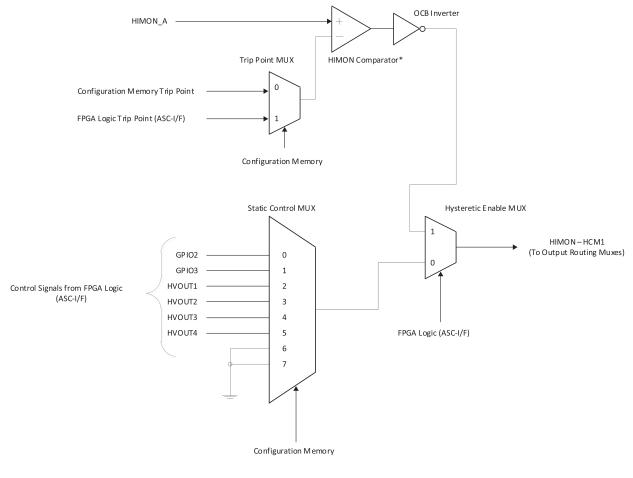

| Figure 6.15. OCB HIMON HCM1 Block Diagram                                                                  |    |

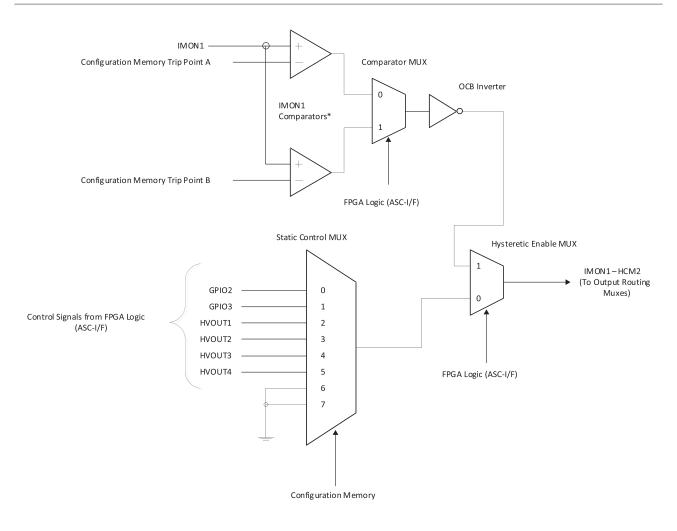

| Figure 6.16. OCB IMON1 HCM2 Block Diagram                                                                  | 44 |

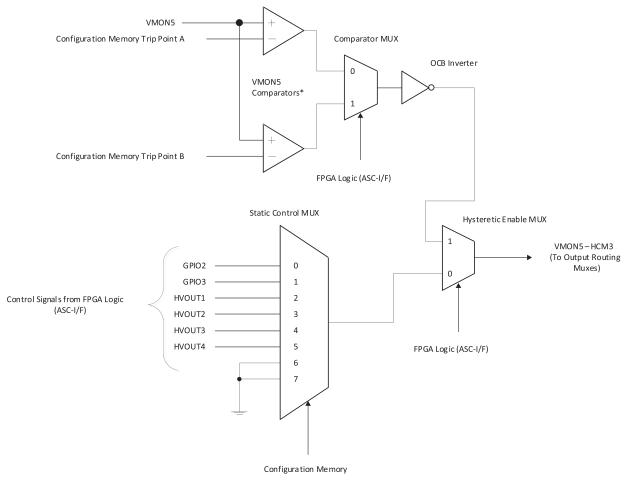

| Figure 6.17. OCB VMON5 HCM3 Block Diagram                                                                  | 45 |

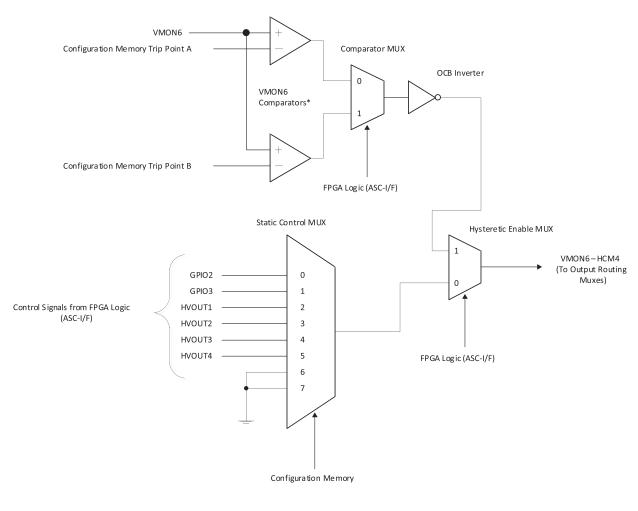

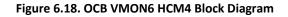

| Figure 6.18. OCB VMON6 HCM4 Block Diagram                                                                  |    |

| Figure 6.19. HVOUT Block Diagram                                                                           | 47 |

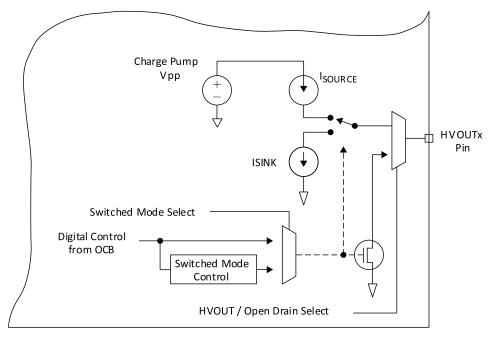

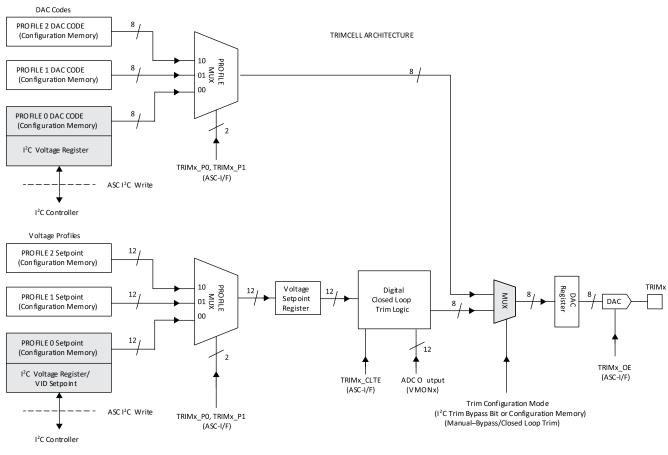

| Figure 6.20. ASC Margin/Trim Block                                                                         | 50 |

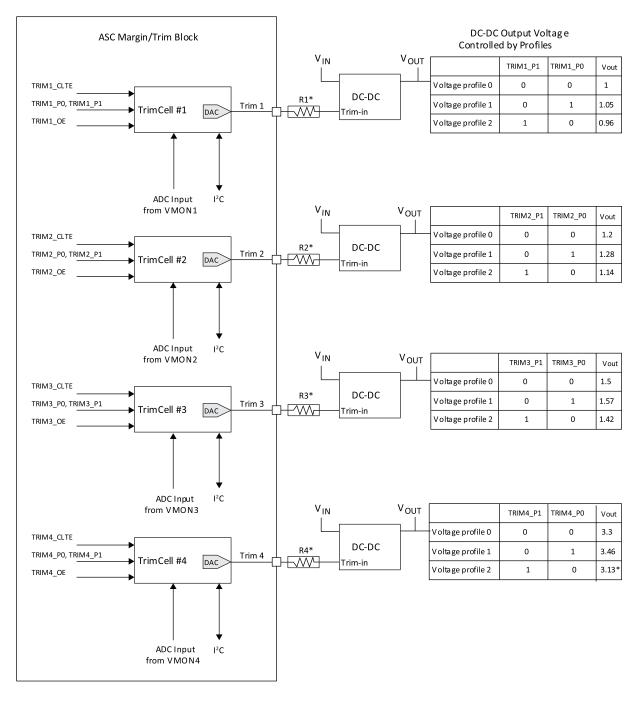

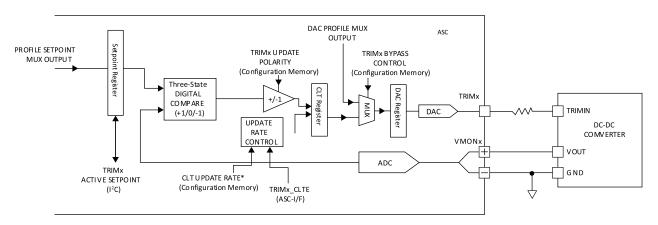

| Figure 6.21. TrimCell Driving a Typical DC-DC Converter                                                    |    |

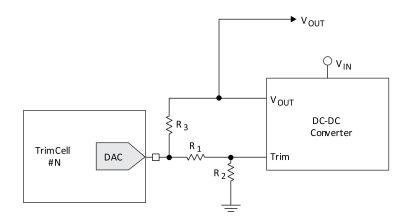

| Figure 6.22. TrimCell Architecture                                                                         | 52 |

| Figure 6.23. Digital Closed Loop Trim Operation                                                            |    |

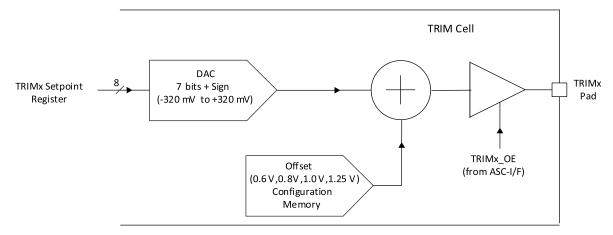

| Figure 6.24. Offset Voltage is Added to DAC Output Voltage to Derive Trim Pad Voltage                      |    |

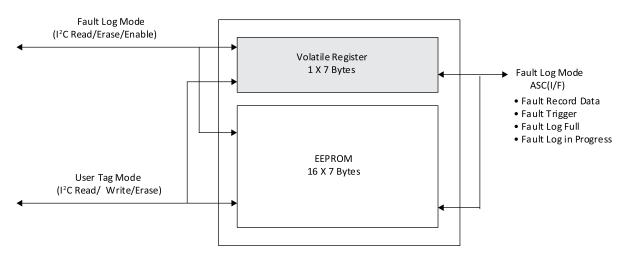

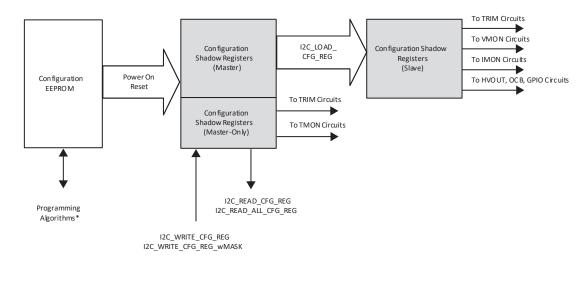

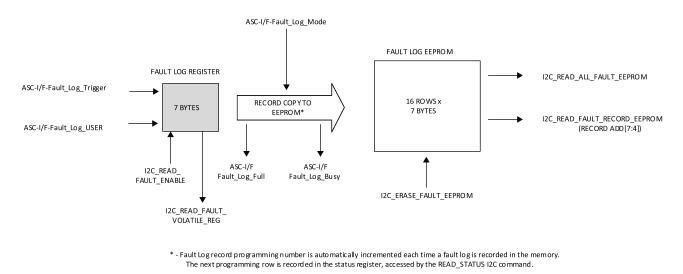

| Figure 6.25. Access to EEPROM and Volatile Memory for Fault Logging/User Tag Operation                     |    |

| Figure 6.26. System Connections - ASC and Platform Manager 2                                               |    |

| Figure 6.27. System Connections - ASC and MachXO2, or MachXO3                                              | 58 |

| Figure 6.28. System Connections - ASC and ECP5                                                             |    |

| Figure 7.1. ASC Devices in an I <sup>2</sup> C System                                                      |    |

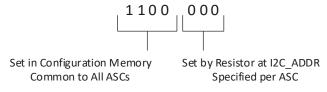

| Figure 7.2. I <sup>2</sup> C Slave Address Construction                                                    |    |

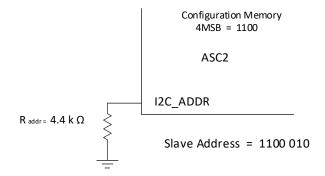

| Figure 7.3. I <sup>2</sup> C Address Resolution Example                                                    |    |

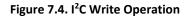

| Figure 7.4. I <sup>2</sup> C Write Operation                                                               |    |

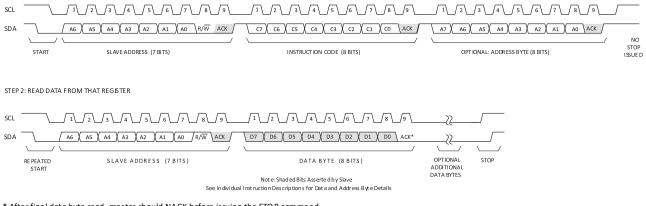

| Figure 7.5. I <sup>2</sup> C Read Operation                                                                |    |

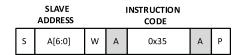

| Figure 7.6. READ_ID Instruction Format                                                                     |    |

| Figure 7.7. READ_STATUS - I <sup>2</sup> C Instruction Format                                              |    |

| Figure 7.8. ASC_Status Register                                                                            |    |

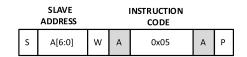

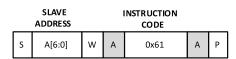

| Figure 7.9. ENABLE_PROG - I <sup>2</sup> C Instruction Format                                              |    |

| Figure 7.10. ENABLE_USER - I <sup>2</sup> C Instruction Format                                             |    |

| Figure 7.11. Configuration Memory Architecture                                                             |    |

| Figure 7.12. READ_EEPROM - I <sup>2</sup> C Instruction Format                                             |    |

| Figure 7.13. WRITE_CFG_REG - I <sup>2</sup> C Instruction Format                                           |    |

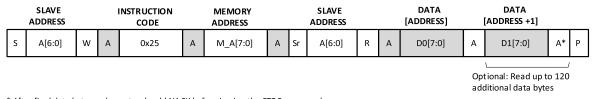

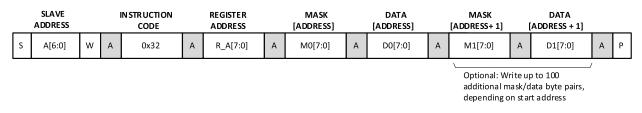

| Figure 7.14. WRITE_CFGREG_wMASK - I <sup>2</sup> C Instruction Format                                      |    |

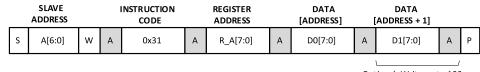

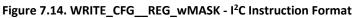

| Figure 7.15. READ_CFG_REG - I <sup>2</sup> C Instruction Format                                            |    |

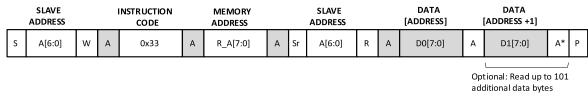

| Figure 7.16. READ_ALL_CFG_REG - I <sup>2</sup> C Instruction Format                                        |    |

| Figure 7.17. LOAD_CFG_REG - I <sup>2</sup> C Instruction Format                                            |    |

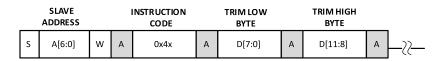

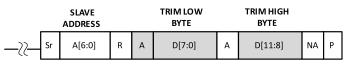

| Figure 7.18. TRIMx_CLT_P0_SET - I <sup>2</sup> C Instruction Format                                        |    |

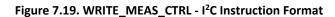

| Figure 7.19. WRITE_MEAS_CTRL - I <sup>2</sup> C Instruction Format                                         | 95 |

| Figure 7.20. READ_MEAS_CTRL - I <sup>2</sup> C Instruction Format<br>Figure 7.21. ADC Registers | 96  |

|-------------------------------------------------------------------------------------------------|-----|

| Figure 7.21. ADC Registers                                                                      | 97  |

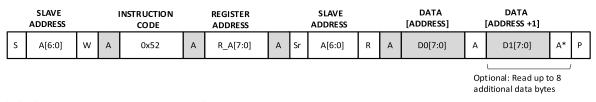

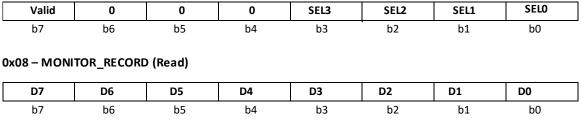

| Figure 7.22. IMON Average Control Registers                                                     | 98  |

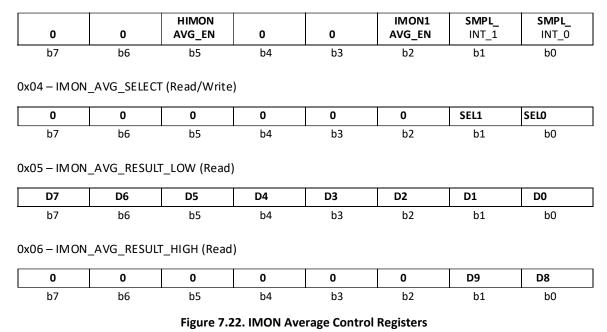

| Figure 7.23. Monitor Signal Access Registers                                                    | 100 |

| Figure 7.24. Output Control Block Register                                                      | 100 |

| Figure 7.25. Temperature Monitor Measurement Registers                                          |     |

| Figure 7.26. Temperature Monitor Status Registers                                               | 102 |

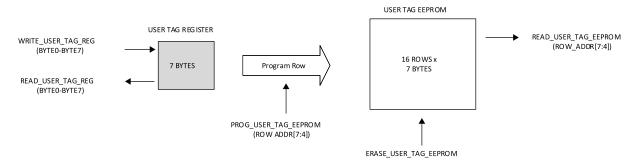

| Figure 7.27. User Tag Memory Architecture with I <sup>2</sup> C Instruction Access              |     |

| Figure 7.28. ERASE_USER_TAG_EEPROM - I <sup>2</sup> C Instruction Format                        | 103 |

| Figure 7.29. WRITE_USER_TAG_REG - I <sup>2</sup> C Instruction Format                           | 103 |

| Figure 7.30. READ_USER_TAG_REG - I <sup>2</sup> C Instruction Format                            | 104 |

| Figure 7.31. PROG_USER_TAG_EEPROM - I <sup>2</sup> C Instruction Format                         |     |

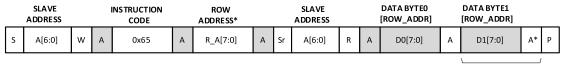

| Figure 7.32. READ_USER_TAG_EEPROM - I <sup>2</sup> C Instruction Format                         |     |

| Figure 7.33. Fault Log Memory Block with I <sup>2</sup> C Access Instructions                   |     |

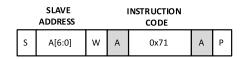

| Figure 7.34. ERASE_FAULT_EEPROM - I <sup>2</sup> C Instruction Format                           | 106 |

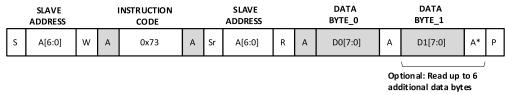

| Figure 7.35. READ_FAULT_VOLATILE_REG - I <sup>2</sup> C Instruction Format                      | 106 |

| Figure 7.36. READ_FAULT_ENABLE - I <sup>2</sup> C Instruction Format                            | 107 |

| Figure 7.37. Fault Log Status Register                                                          | 107 |

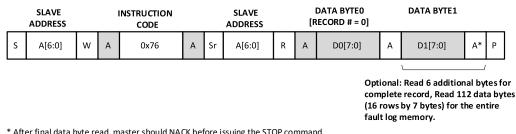

| Figure 7.38. READ_FAULT_RECORD_EEPROM - I <sup>2</sup> C Instruction Format                     | 107 |

| Figure 7.39. READ_ALL_FAULT_EEPROM - I <sup>2</sup> C Instruction Format                        | 108 |

| Figure 7.40. I <sup>2</sup> C Write Protect by GPIO1                                            | 109 |

## Tables

| Table 5.1. Absolute Maximum Ratings                                                             | 13 |

|-------------------------------------------------------------------------------------------------|----|

| Table 5.2. Recommended Operating Conditions                                                     | 14 |

| Table 5.3. Analog Specifications                                                                | 14 |

| Table 5.4. Power-On Reset                                                                       |    |

| Table 5.5. Voltage Monitors                                                                     | 16 |

| Table 5.6. Current Monitors                                                                     | 17 |

| Table 5.7. ADC Characteristics                                                                  |    |

| Table 5.8. ADC Error Budget Across Entire Operating Temperature Range                           | 19 |

| Table 5.9. Temperature Monitors                                                                 |    |

| Table 5.10. Digital Specifications                                                              |    |

| Table 5.11. High Voltage FET Drivers                                                            |    |

| Table 5.12. Margin/Trim DAC Output Characteristics                                              |    |

| Table 5.13. Fault Log                                                                           |    |

| Table 5.14. Oscillator                                                                          |    |

| Table 5.15. Propagation Delays                                                                  |    |

| Table 5.16. FPGA Section sysI/O Single-Ended DC Electrical Characteristics <sup>1, 2</sup>      |    |

| Table 5.17. ASC Interface (ASC-I/F) Timing Specifications                                       |    |

| Table 5.18. I <sup>2</sup> C Port Timing Specifications                                         |    |

| Table 6.1. Voltage Monitor Comparator Hysteresis versus Trip-Point                              |    |

| Table 6.2. Voltage Monitoring Window Logic                                                      |    |

| Table 6.3. Fast Fault Detector Current Trip Points versus Frequently Used Sense Resistor Values |    |

| Table 6.4. Comparator Trip Points                                                               |    |

| Table 6.5. IMON Window Mode Behavior                                                            |    |

| Table 6.6. HVMON Hysteresis vs Trip Point Range                                                 |    |

| Table 6.7. Remote TMON Diode Configurations                                                     |    |

| Table 6.8. Temperature Measurement Fault Readings                                               |    |

| Table 6.9. Temperature Measurement Settling Time                                                |    |

| Table 6.10. GPIO Input and Output Sources                                                       |    |

| Table 6.11. GPIO and HVOUT Safe-State Definitions                                               |    |

| Table 6.12. DAC Output Value versus Configuration Settings                                      |    |

| Table 6.13. Closed Loop Trim Update Rates                                                       |    |

| Table 6.14. Fault Log Record Memory Map                                                         |    |

| Table 6.15. Platform Manager 2 Design Options                                                   |    |

| Table 7.1. I <sup>2</sup> C Reserved Slave Device Addresses                                     |    |

| Table 7.2. R <sub>addr</sub> Value vs. ASC Device Number                                        |    |

| Table 7.3. I <sup>2</sup> C Instruction Summary                                                 |    |

| Table 7.4. Device Status and Mode Management Instruction Codes                                  |    |

| Table 7.5. ASC ID Codes                                                                         |    |

| Table 7.6. Configuration Register Instruction Codes                                             |    |

| Table 7.7. Trim Configuration Register Summary                                                  |    |

| Table 7.8. POL Setting vs Closed Loop Trim Polarity                                             |    |

| Table 7.9. BYP Setting vs Trim Voltage Source                                                   |    |

| Table 7.10. ATT Setting vs Attenuation Value                                                    |    |

| Table 7.11. RATE[1:0] Setting vs Closed Loop Trim Update Rate                                   |    |

| Table 7.12. Dx_BPZ[1:0] Setting vs DAC Bi-Polar Zero Output Voltage                             |    |

| Table 7.13. Voltage Monitor Configuration Register Summary                                      |    |

| Table 7.14. Trip Point for Over-Voltage Detection (Differential VMON1-VMON4)                    |    |

| Table 7.15. Trip Point for Under-Voltage Detection (Differential VMON1-VMON4)                   |    |

| Table 7.16. Trip Point for Over-Voltage Detection (Single-Ended VMON5-VMON9)                    |    |

| Table 7.17. Trip Point for Under-Voltage Detection (Single-Ended VMON5-VMON9)                   |    |

| Table 7.18. GBP Setting vs Glitch Bypass Behavior                                               |    |

| Table 7.19. WM Setting vs Window Mode Value                                                     | 81 |

| Table 7.20. | Trip-Point for Over-Voltage Detection (HVMON)             | 82   |

|-------------|-----------------------------------------------------------|------|

|             | Trip-Point for Over-Voltage Detection (HVMON)             |      |

| Table 7.22. | Current Monitor Configuration Register Summary            | 84   |

| Table 7.23. | Current Monitor Trip Points (Differential Voltage)        | 84   |

| Table 7.24. | GBP Setting vs Glitch Bypass Behavior                     | 84   |

| Table 7.25. | WM Setting vs Window Mode Value                           | 84   |

|             | LSS Setting vs Low Side Sensing Mode                      |      |

|             | Fast Current Monitor Trip Points (Differential Voltage)   |      |

| Table 7.28. | Temperature Monitor Configuration Register Summary        | 85   |

|             | Ideality Factor vs Ideality_Code Setting                  |      |

|             | Temperature Monitor Diode Configuration Settings          |      |

|             | Temperature Monitor Offset Settings                       |      |

| Table 7.32. | Temperature Monitor Thresholds Settings                   | 87   |

|             | Temperature Monitor Fault Setting                         |      |

|             | Temperature Monitor Measurement Average Settings          |      |

|             | Temperature Monitor Hysteresis Settings                   |      |

|             | High Voltage Output Configuration Register Summary        |      |

|             | OCB Setting vs HVOUT Source Selection                     |      |

|             | HVOUT Source Current Settings                             |      |

|             | HVOUT Sink Current Settings                               |      |

|             | HVOUT Output Voltage Settings                             |      |

|             | SW Setting vs HVOUT Mode                                  |      |

|             | FR Setting vs HVOUT Output Frequency (Switched Mode only) |      |

|             | OD Setting vs HVOUT Output Mode                           |      |

|             | HVOUT Switched Output Duty Cycle Settings                 |      |

|             | Output Control Block Configuration Register Summary       |      |

|             | Output Control Block – Output Source Signals              |      |

|             | Output Control Block – Hysteretic Control Mux Settings    |      |

|             | H4i G2i Setting vs OCB Output Behavior                    |      |

|             | HI_T Setting vs HIMONA Threshold Source                   |      |

|             | GPIO Input Configuration Register Summary.                |      |

|             | Grin Setting vs GPIO Input Setting                        |      |

|             | Write Protect and User Tag Configuration Register         |      |

|             | UT_EN vs Fault Log / User Tag Mode                        |      |

|             | Write Protect Settings                                    |      |

|             | UES Memory Summary                                        |      |

|             | Reserved Configuration Addresses                          |      |

|             | Closed Loop Trim Access Instructions                      |      |

|             | Measurement and Control Register Overview                 |      |

|             | ADC Input Attenuator Control                              |      |

|             | ADC Input Selection                                       |      |

|             | IMON Average Sample Interval Values                       |      |

|             | Selected IMON Average Readout Channel                     |      |

|             | -                                                         |      |

|             | MONITOR_RECORD Byte Selection                             |      |

|             | Temperature Measurement Data Format                       |      |

|             | User Tag Memory Access Instructions                       |      |

|             | Fault Log Access Instructions                             |      |

|             | Fault Log Status Details                                  |      |

|             | Pin Descriptions                                          |      |

| Table 12.1. | Halogen-Free Packaging                                    | .116 |

## 1. Features

## 1.1. Ten Rail Voltage Monitoring and Measurement

- UV/OV Fault Detection Accuracy 0.2% Typ.

- Fault Detection Speed <100 µs

- High Voltage, Single Ended and Differential Sensing

## 1.2. Two Channel Wide-Range Current Monitoring and Measurement

- High-side current Measurement up to 12 V

- Programmable OC/UC Fault Detect

- Detects Current faults in < 1 μs

# **1.3.** Three Temperature Monitoring and Measurement Channels

- Programmable OT/UT Faults Threshold

- Two channels of Temperature Monitoring using external diodes

- One On-Chip Temperature Monitor

## 1.4. Four High-Side MOSFET Drivers

Programmable Charge Pump

## 1.5. Four Precision Trim and Margin Channels

- Closed Loop Operation

- Voltage Scaling and VID Support

# 1.6. Nine General Purpose Input / Output

5 V tolerant I/O

## 1.7. Non-Volatile Fault Logging

## 1.8. In-system Programmable Through I<sup>2</sup>C

- Non-Volatile Configuration

- Background Programming Support

### 1.9. System Level Support

- 3.3 V Operation, wide input supply range 2.8 V to 3.6 V

- Industrial temperature range

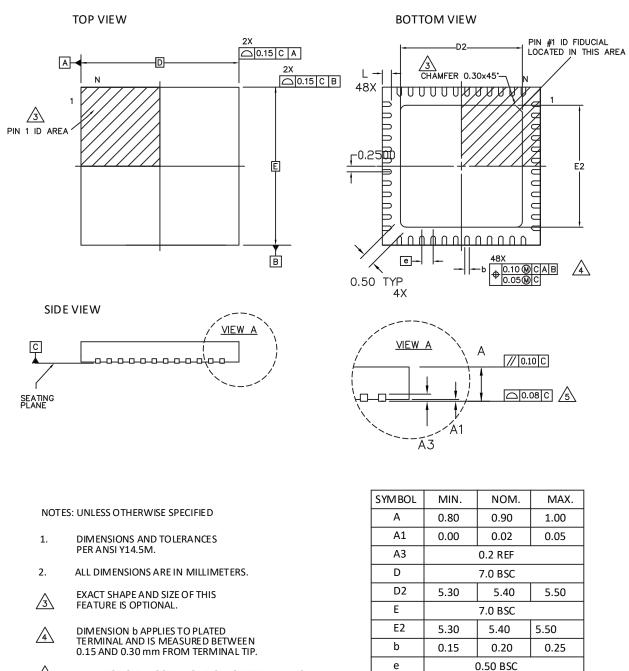

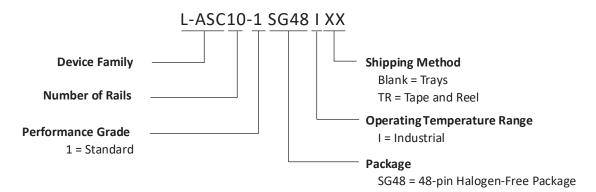

- 48-pin QFN

- RoHS compliant and halogen-free

### 1.10. Applications

- Telecommunication and Networking

- Industrial, Test and Measurement

- Medical Systems

- Servers and Storage Systems

- High Reliability Systems

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice

FPGA-DS-02038-2.5

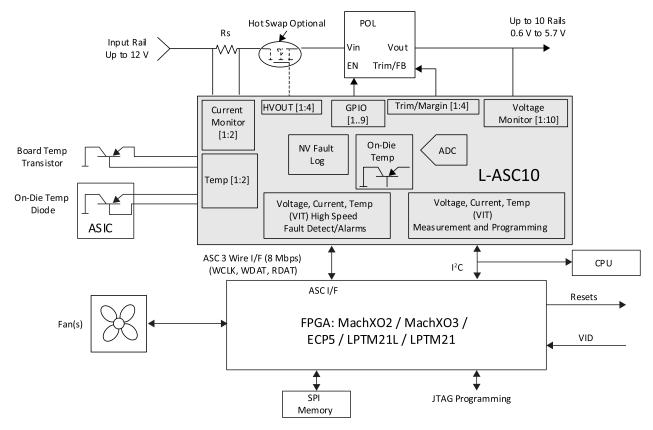

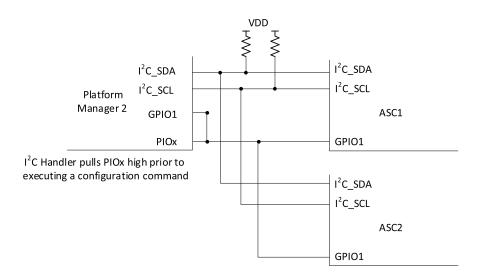

## 2. Application Diagram

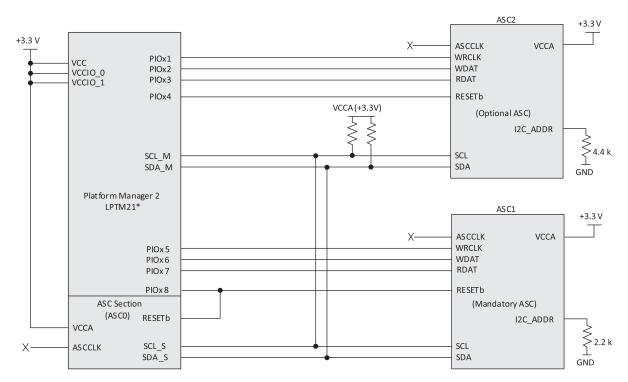

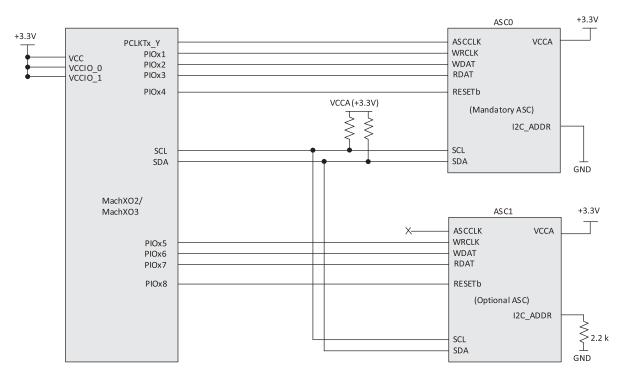

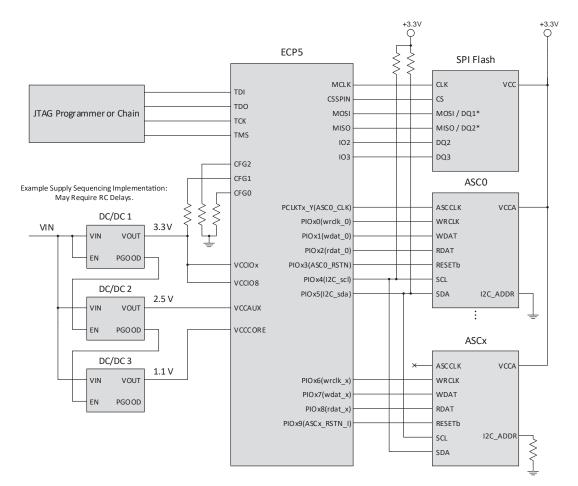

Figure 2.1. Hardware Management Application Block Diagram

## 3. Description

The L-ASC10 (Analog Sense and Control-10 rail) is a Hardware Management (Power, Thermal, and Control Plane Management) Expander designed to be used with Platform Manager™ 2, MachXO2™, MachXO3, or ECP5™ FPGAs to implement the Hardware Management Control function in a circuit board. The L-ASC10 (referred to as ASC) enables seamless scaling of power supply voltage and current monitoring, temperature monitoring, sequence and margin control channels. The ASC includes dedicated interfaces supporting the exchange of monitor signal status and output control signals with these centralized hardware management controllers. Up to eight ASC devices can be used to implement a hardware management system.

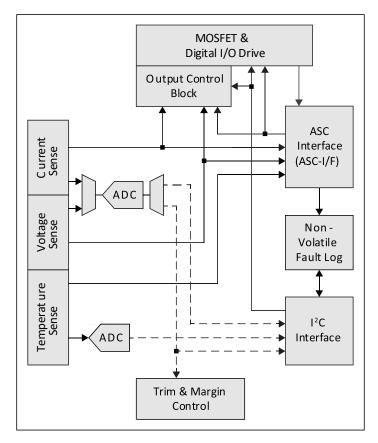

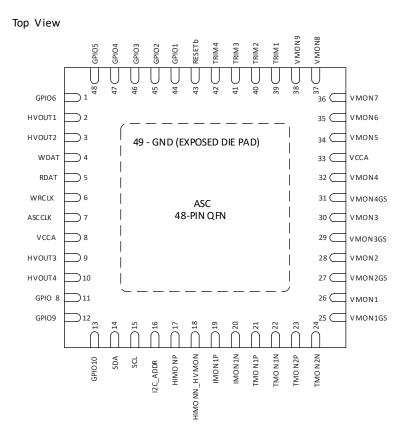

The ASC provides three types of analog sense channels: voltage (nine standard channels and one high voltage channel), current (one standard voltage and one high voltage), and temperature (two external and one internal) as shown in Figure 4.1.

Each of the analog sense channels is monitored through two independently programmable comparators to support both high/low and in-bounds/out-of-bounds (window-compare) monitor functions. The current sense channels feature a programmable gain amplifier and a fast fault detect (<1 µs response time) for detecting short circuit events. The temperature sense channels can be configured to work with different external transistor or diode configurations.

Nine general purpose 5 V tolerant open-drain digital input/output pins are provided that can be used in a system for controlling DC-DC converters, low-drop-out regulators (LDOs) and optocouplers, as well as for supervisory and general-purpose logic interface functions. Four high-voltage charge pumped outputs (HVOUT1-HVOUT4) may be configured as high-voltage MOSFET drivers to control high-side MOSFET switches. These HVOUT outputs can also be programmed as static output signals or as switched outputs (to support external charge pump implementation) operating at a dedicated duty cycle and frequency.

The ASC device incorporates four TRIM outputs for controlling the output voltages of DC-DC converters. Each power supply output voltage can be maintained typically within 0.5% tolerance across various load conditions using the Digital Closed Loop Control mode.

The internal 10-bit A/D converter can be used to monitor the voltage and current through the  $I^2C$  bus. The ADC is also used in the digital closed loop control mode of the trimming block.

The ASC also provides the capability of logging up to 16 status records into the on-chip nonvolatile EEPROM memory. Each record includes voltage, current and temperature monitor signals along with digital input and output levels.

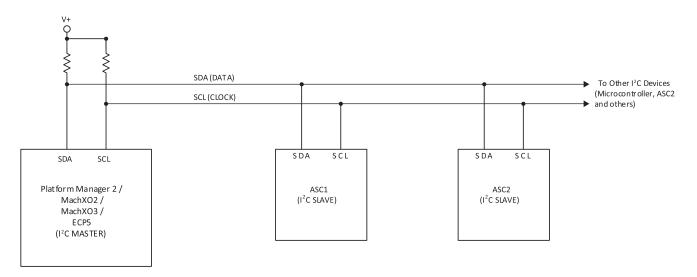

The dedicated ASC Interface (ASC-I/F) is a reliable serial channel used to communicate with a Platform Manager 2, MachXO2, MachXO3, or ECP5 FPGA in a scalable star topology. The centralized control algorithm in the FPGA monitors signal status and controls output behavior via this ASC-I/F. The ASC I<sup>2</sup>C interface is used by the FPGA or an external microcontroller for ASC background programming, interface configuration, and additional data transfer such as parameter measurement or I/O control or status. For example, voltage trim targets can be set over the I<sup>2</sup>C bus and measured voltage, current, or temperature values can be read over the I<sup>2</sup>C bus.

The ASC also includes an on-chip output control block (OCB) which allows certain alarms and control signals a direct connection to the GPIOs or HVOUTs, bypassing the ASC-I/F for a faster response. The OCB is used to connect the fast current fault detect signal to an FPGA input directly. It also supports functions like Hot Swap with a programmable hysteretic controller.

## 4. ASC Block Diagram

Figure 4.1. ASC Block Diagram

## 5. DC and Switching Characteristics

## 5.1. Absolute Maximum Ratings

#### Table 5.1. Absolute Maximum Ratings

| Symbol                  | Parameter                                    | Conditions               | Min  | Max.             | Units |

|-------------------------|----------------------------------------------|--------------------------|------|------------------|-------|

| V <sub>CCA</sub>        | Main Power Supply                            | -                        | -0.5 | 4.5              | V     |

| V <sub>IN_VMON</sub>    | VMON input voltage                           | -                        | -0.5 | 6                | V     |

| V <sub>IN_VMONGS</sub>  | VMON input voltage ground sense              | -                        | -0.5 | 6                | V     |

| VIN_HIMONP              | High voltage IMON input voltage              | -                        | -0.5 | 13.3             | V     |

| VIN_HIMONN              | High voltage IMON return/ VMON input voltage | -                        | -0.5 | 13.3             | V     |

| V <sub>DIFF_HIMON</sub> | High voltage IMON differential voltage       | -                        | -2.0 | 2.0              | V     |

| VIN_IMONP               | Low voltage IMON1 input voltage              | -                        | -0.5 | 6.0              | V     |

| V <sub>IN_IMONN</sub>   | Low voltage IMON1 return voltage             | -                        | -0.5 | 6.0              | V     |

| V <sub>DIFF_IMON</sub>  | Low voltage IMON1 differential voltage       | -                        | -2.0 | 2.0              | V     |

| VIN_TMONP               | TMON input voltage                           | -                        | -0.5 | V <sub>CCA</sub> | V     |

| V <sub>IN_TMONN</sub>   | TMON return voltage                          | -                        | -0.5 | V <sub>CCA</sub> | V     |

| V <sub>IN_GPIO</sub>    | Digital input voltage                        | -                        | -0.5 | 6                | V     |

| V <sub>OUT</sub>        | Open-drain output voltage                    | HVOUT [1:4]              | -0.5 | 13.3             | V     |

|                         |                                              | GPIO[1:6],<br>GPIO[8:10] | -0.5 | 6                | V     |

| V <sub>TRIM</sub>       | TRIM output voltage                          | -                        | -0.5 | V <sub>CCA</sub> | V     |

| I <sub>SINKMAX</sub>    | Maximum Sink Current on any output           | _                        | —    | 23               | mA    |

| Ts                      | Device Storage Temperature                   | -                        | -65  | +125             | °C    |

| T <sub>A</sub>          | Ambient Temperature                          | _                        | -40  | +125             | °C    |

## 5.2. Recommended Operating Conditions

#### **Table 5.2. Recommended Operating Conditions**

| Symbol                  | Parameter                                                 | Conditions                 | Min  | Max. | Units |

|-------------------------|-----------------------------------------------------------|----------------------------|------|------|-------|

| V <sub>CCA</sub>        | Main Power Supply <sup>1</sup>                            | -                          | 2.8  | 3.6  | V     |

| VIN_VMON                | VMON input voltage                                        | -                          | -0.3 | 5.9  | V     |

| VIN_VMONGS              | VMON input voltage ground sense                           | -                          | -0.2 | 0.3  | V     |

| VIN_HIMONP              | High voltage IMON input voltage <sup>2</sup>              | -                          | 4.5  | 13.2 | V     |

| VIN_HIMONN              | High voltage IMON return/ VMON input voltage <sup>2</sup> | -                          | 4.5  | 13.2 | V     |

| V <sub>DIFF_HIMON</sub> | High voltage IMON differential voltage                    | -                          | 0    | 500  | mV    |

| VIN_IMONP               | Low voltage IMON1 input voltage                           | Low Side Sense<br>Disabled | 0.6  | 5.9  | V     |

|                         |                                                           | Low Side Sense<br>Enabled  | -0.3 | 1.0  | V     |

| V <sub>IN_IMONN</sub>   | Low voltage IMON1 return voltage                          | Low Side Sense<br>Disabled | 0.6  | 5.9  | V     |

|                         |                                                           | Low Side Sense<br>Enabled  | -0.3 | 1.0  | V     |

| V <sub>DIFF_IMON</sub>  | Low voltage IMON1 differential voltage                    | -                          | 0    | 500  | mV    |

| VIN_GPIO                | Digital input voltage                                     | _                          | -0.3 | 5.5  | V     |

| V <sub>OUT</sub>        | Open-drain output voltage                                 | HVOUT [1:4]                | -0.3 | 13.2 | V     |

|                         |                                                           | GPIO[1:6],<br>GPIO[8:10]   | -0.3 | 5.5  | V     |

| T <sub>A</sub>          | Ambient Temperature                                       | _                          | -40  | +85  | °C    |

Notes:

1. The VCC of the I/O bank of the MachXO2, MachXO3, ECP5, LPTM21L, or LPTM21 that is used for the ASC-I/F needs to be connected to the VCCA of the respective ASC device. Refer to the System Connections section for more details.

2. HIMON circuits are operational down to 3 V. Accuracy is guaranteed within Recommended Operating Conditions.

## 5.3. Analog Specifications

#### **Table 5.3. Analog Specifications**

| Symbol                | Parameter                         | Conditions                                                                                        | Min. | Тур. | Max | Units |

|-----------------------|-----------------------------------|---------------------------------------------------------------------------------------------------|------|------|-----|-------|

| I <sub>CCA</sub>      | Supply Current                    | V <sub>CCA</sub> = 3.3 V,<br>Ta 25 °C                                                             | -    | 25   | 35  | mA    |

| I <sub>CC-HVOUT</sub> | Supply Current Adder per HVOUT    | V <sub>HVOUT</sub> = 12 V,<br>I <sub>SRC</sub> = 100 uA,<br>V <sub>CCA</sub> = 3.3 V,<br>Ta 25 °C | -    | _    | 2   | mA    |

| ICCPROG               | Supply Current during Programming | V <sub>CCA</sub> = 3.3 V,<br>Ta 25 °C                                                             | _    | _    | 40  | mA    |

## 5.4. ESD Performance

Please refer to the Platform Manager 2 Product Family Qualification Summary for complete qualification data, including ESD performance.

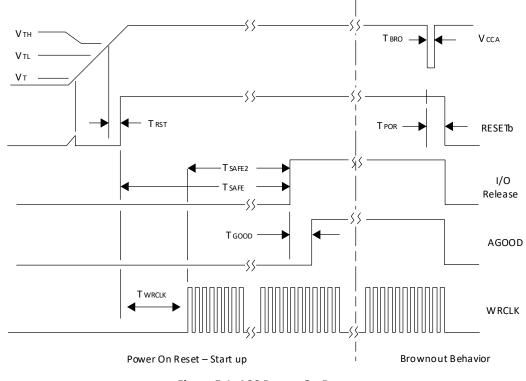

### 5.5. Power-On Reset

#### Table 5.4. Power-On Reset

| Symbol             | Parameter                                                                           | Conditions | Min | Тур. | Max. | Units |

|--------------------|-------------------------------------------------------------------------------------|------------|-----|------|------|-------|

| T <sub>RST</sub>   | Delay from VTH to start-up state                                                    | —          | —   | —    | 100  | μs    |

| T <sub>SAFE</sub>  | Delay from RESETb release to ASC Safe State<br>Exit and I/O Release <sup>1, 2</sup> | _          | _   | 1.8  | _    | ms    |

| T <sub>SAFE2</sub> | Delay from WRCLK start to ASC Safe State<br>Exit and I/O Release <sup>1, 2, 3</sup> | _          | 56  |      | —    | μs    |

| T <sub>GOOD</sub>  | Delay from I/O release to AGOOD asserted<br>high in FPGA section <sup>4</sup>       | _          |     | 16   | —    | μs    |

| T <sub>WRCLK</sub> | Delay from RESETb release to WRCLK start <sup>5</sup>                               | —          |     | 1.4  | —    | ms    |

| T <sub>BRO</sub>   | Minimum duration brown out required to trigger RESETb                               | _          | 1   | —    | 5    | μs    |

| T <sub>POR</sub>   | Delay from Brown out to reset state                                                 | _          | —   | —    | 13   | μs    |

| V <sub>TL</sub>    | Threshold below which RESETb is LOW                                                 | _          | _   | _    | 2.3  | V     |

| V <sub>TH</sub>    | Threshold above which RESETb is Hi-Z                                                | —          | 2.7 | _    | _    | V     |

| VT                 | Threshold above which RESETb is valid                                               | _          | 0.8 | _    | —    | V     |

| CL                 | Capacitive load on RESETb                                                           | —          | —   | —    | 200  | рF    |

Notes:

1. Both  $T_{SAFE}$  and  $T_{SAFE2}$  must complete before I/O are released from Safe State.

2. During the calibration period before T<sub>SAFE</sub> and T<sub>SAFE2</sub>, the ASC may ignore RESETb being driven low. After T<sub>SAFE</sub> and T<sub>SAFE2</sub>, the ASC can be reset by another device by driving RESETb low.

- 3. Safe State is released at ASC after a fixed number (64) of WRCLK cycles (typ. 8 MHz frequency) and three ASC-I/F data packets are properly detected.

- 4. AGOOD asserted in the FPGA on the next ASC-I/F packet after I/O exits Safe State as ASC.

- 5. Parameter is dependent on the FPGA configuration refresh time during POR. Refer to the Platform Manager 2, MachXO2, MachXO3, or ECP5 data sheet for details.

## 5.6. Voltage Monitors

#### Table 5.5. Voltage Monitors

| Symbol                    | Parameter                                                       | Conditions             | Min   | Тур | Max   | Units |

|---------------------------|-----------------------------------------------------------------|------------------------|-------|-----|-------|-------|

| R <sub>VMON_in</sub>      | Input Resistance                                                | -                      | 55    | 65  | 75    | kΩ    |

| C <sub>VMON_in</sub>      | Input Capacitance                                               | -                      | _     | 8   | —     | pF    |

| V <sub>MON</sub> Range    | Programmable trip-point Range                                   | -                      | 0.075 |     | 5.734 | Volts |

| V <sub>MON</sub> Accuracy | Absolute accuracy of any trip-point<br>– Differential VMON pins | VMON voltage > 0.650 V | _     | 0.2 | 0.7   | %     |

|                           | Single-ended VMON pins                                          | VMON voltage > 0.650 V | _     | 0.3 | 0.9   | %     |

| V <sub>MON</sub> HYST     | Hysteresis of any trip-point<br>(relative to setting)           | _                      | _     | 1   | -     | %     |

| V <sub>MON</sub> CMR      | Differential VMON Common mode rejection ratio                   | _                      | _     | 60  | -     | dB    |

| V <sub>z</sub> Sense      | Low Voltage Sense Trip Point Error                              | Trip Point = 0.075 V   | -5    | _   | +5    | mV    |

|                           | – Differential VMON1-4                                          | Trip Point = 0.150 V   | -5    | _   | +5    | mV    |

|                           |                                                                 | Trip Point = 0.300 V   | -10   | _   | +10   | mV    |

|                           |                                                                 | Trip Point = 0.545 V   | -15   | _   | +15   | mV    |

|                           | Low Voltage Sense Trip Point Error<br>– Single-Ended VMON5-9    | Trip Point = 0.080 V   | -10   | _   | +10   | mV    |

|                           |                                                                 | Trip Point = 0.155 V   | -15   | _   | +15   | mV    |

|                           |                                                                 | Trip Point = 0.310 V   | -25   | _   | +25   | mV    |

|                           |                                                                 | Trip Point = 0.565 V   | -55   | _   | +55   | mV    |

| High Voltage Mor          | nitor                                                           |                        |       |     |       |       |

| $H_{VMON}$ Range          | High Voltage VMON programmable trip-point range                 | -                      | 0.3   | -   | 13.2  | Volts |

| $H_{VMON}$ Accuracy       | HVMON Absolute accuracy of any trip-point                       | -                      | —     | 0.4 | 1.0   | %     |

| V <sub>z</sub> Sense      | Low Voltage Sense Trip Point Error                              | Trip Point = 0.220 V   | -20   | _   | +20   | mV    |

|                           | - HVMON pin                                                     | Trip Point = 0.425 V   | -35   | _   | +35   | mV    |

|                           |                                                                 | Trip Point = 0.810 V   | -75   | _   | +75   | mV    |

|                           |                                                                 | Trip Point = 1.280 V   | -130  | _   | +130  | mV    |

**Note:** VMON accuracy may degrade based on SSO conditions of hardware management controller ASC-I/F. Refer to the System Connections section for more details.

## 5.7. Current Monitors

#### **Table 5.6. Current Monitors**

| Symbol                                    | Parameter                           | Conditions                                                              | Min  | Тур | Max | Units |

|-------------------------------------------|-------------------------------------|-------------------------------------------------------------------------|------|-----|-----|-------|

| IIMONPleak                                | IMON1P input leakage                | Low Side Sense Disabled<br>Fast Trip Point V <sub>sns</sub> =<br>500 mV | -2   | _   | 250 | μΑ    |

|                                           |                                     | Low Side Sense Enabled<br>Fast Trip Point V <sub>sns</sub> =<br>500 mV  | -2   | _   | 40  | μΑ    |

| IIMONNleak                                | IMON1N input leakage                | Low Side Sense Disabled<br>Fast Trip Point V <sub>sns</sub> =<br>500 mV | -2   | _   | 2   | μΑ    |

|                                           |                                     | Low Side Sense Enabled<br>Fast Trip Point V <sub>sns</sub> =<br>500 mV  | -200 | _   | 2   | μΑ    |

| I <sub>HIMONPleak</sub>                   | HIMONP input leakage                | Fast Trip Point V <sub>sns</sub> = 500<br>mV                            | _    | _   | 550 | μΑ    |

| HIMONNleak                                | HIMONN_HVMON input leakage          | _                                                                       | _    | _   | 350 | μA    |

| I <sub>MONA/B</sub> Accuracy <sup>2</sup> | HIMON, IMON1A/B Comparator          | Gain = 100x                                                             | —    | 8   | —   | %     |

|                                           | Trip Point accuracy                 | Gain = 50x                                                              | _    | 5   | —   | %     |

|                                           |                                     | Gain = 25x                                                              | —    | 3   | —   | %     |

|                                           |                                     | Gain = 10x                                                              | —    | 2   | _   | %     |

| I <sub>MONA/B</sub> Gain                  | Programmable Gain Setting           | Four settings in software                                               | _    | 10  | —   | V/V   |

|                                           |                                     |                                                                         | _    | 25  | —   | V/V   |

|                                           |                                     |                                                                         | _    | 50  | —   | V/V   |

|                                           |                                     |                                                                         | _    | 100 | —   | V/V   |

| I <sub>MONF</sub> Accuracy <sup>2</sup>   | Fast comparator trip-point accuracy | V <sub>sns</sub> 1 = 50 mV, 100 mV,<br>or<br>150 mV                     | _    | 8   | _   | %     |

|                                           |                                     | V <sub>sns</sub> = 200 mV, 250 mV,<br>or 300 mV                         | —    | 5   | —   | %     |

|                                           |                                     | V <sub>sns</sub> = 400 mV or 500 mV                                     | —    | 3   | —   | %     |

| t <sub>IMONF</sub>                        | Fast comparator response time       | -                                                                       | _    | _   | 1   | μs    |

Notes:

1.  $V_{sns}$  is the differential voltage between IMON1P and IMON1N (or HIMONP and HIMONN).

2. IMON accuracy may degrade based on SSO conditions of hardware management controller ASC-I/F. Refer to the System Connections section for more details.

## 5.8. ADC Characteristics

#### **Table 5.7. ADC Characteristics**

| Symbol                   | Parameter                                     | Conditions                      | Min | Тур    | Max   | Units |

|--------------------------|-----------------------------------------------|---------------------------------|-----|--------|-------|-------|

|                          | Resolution                                    | -                               | _   | 10     | _     | Bits  |

| t <sub>convert</sub>     | Conversion Time from I <sup>2</sup> C Request | -                               | _   | _      | 200   | μs    |

| Voltage Monito           | ors                                           |                                 | •   | •      |       |       |

| V <sub>VMON-IN</sub>     | Input Range Full scale                        | Programmable                    | 0   | _      | 2.048 | V     |

|                          |                                               | Attenuator = 1                  |     |        |       |       |

|                          |                                               | Programmable                    | 0   | _      | 5.91  |       |

|                          |                                               | Attenuator = 3                  |     |        |       |       |

| LSB                      | ADC Step Size                                 | Programmable                    | _   | 2      | -     | mV    |

|                          |                                               | Attenuator = 1                  |     |        |       |       |

|                          |                                               | Programmable                    | —   | 6      | -     |       |

|                          |                                               | Attenuator = 3                  |     |        |       |       |

| E <sub>VMON</sub> -      | Error due to attenuator                       | Programmable                    | _   | +/-0.1 | -     | %     |

| attenuator               |                                               | Attenuator = 3                  |     |        |       |       |

| High Voltage N           | Ionitor                                       |                                 |     |        |       |       |

| V <sub>HVMON-IN</sub>    | Input Range Full scale                        | Programmable                    | 0   | —      | 8.192 | V     |

|                          |                                               | Attenuator = 4                  |     |        |       |       |

|                          |                                               | Programmable                    | 0   | _      | 13.21 |       |

|                          |                                               | Attenuator = 8                  |     |        |       |       |

| LSB                      | ADC Step Size                                 | Programmable                    | _   | 8      | -     | mV    |

|                          |                                               | Attenuator = 4                  |     |        |       |       |

|                          |                                               | Programmable                    | —   | 16     | -     |       |

|                          |                                               | Attenuator = 8                  |     |        |       |       |

| E <sub>HVMON</sub> -     | Error due to attenuator                       | Programmable                    | —   | +/-0.2 | —     | %     |

| attenuator               |                                               | Attenuator = 4                  |     |        |       |       |

|                          |                                               | Programmable                    | —   | +/-0.4 | _     | %     |

|                          |                                               | Attenuator = 8                  |     |        |       |       |

| Current Monito           | ors                                           |                                 |     |        |       |       |

| t <sub>IMON-sample</sub> | Sample period of HIMON and                    | 4 Settings via I <sup>2</sup> C | _   | 1      |       | ms    |

|                          | IMON1 conversions for averaged                | command                         | _   | 2      | _     |       |

|                          | value                                         |                                 | _   | 4      | _     |       |

|                          |                                               |                                 | _   | 8      | _     |       |

| V <sub>IMON-IN</sub>     | Input Range Full scale <sup>1</sup>           | Programmable Gain 10x           | 0   | _      | 200   | mV    |

|                          |                                               | Programmable Gain 25x           | 0   | _      | 80    |       |

|                          |                                               | Programmable Gain 50x           | 0   | _      | 40    |       |

|                          |                                               | Programmable Gain               | 0   | _      | 20    |       |

|                          |                                               | 100x                            | Ū   |        | 20    |       |

| LSB                      | ADC Step Size                                 | Programmable Gain 10x           | _   | 0.2    | _     | mV    |

|                          |                                               | Programmable Gain 25x           | —   | 0.08   | _     |       |

|                          |                                               | Programmable Gain 50x           | —   | 0.04   | —     |       |

|                          |                                               | Programmable Gain<br>100x       | —   | 0.02   | —     |       |

Note: Differential voltage applied across HIMONP/IMON1P and HIMONN/IMON1N before programmable gain amplification.

## 5.9. ADC Error Budget Across Entire Operating Temperature Range

| Table 5.8. ADC Error | Budget Across | Entire Operating | Temperature Range  |

|----------------------|---------------|------------------|--------------------|

|                      | Duuget Acioss | Linuie Operating | i emperature nange |

| Symbol     | Parameter                                                                                                      | Conditions                                                              | Min | Тур       | Max | Units |

|------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|-----------|-----|-------|

| TADC Error | Total ADC Measurement<br>Error at Any Voltage                                                                  | Measurement Range 600 mV - 2.048 V,<br>VMONxGS > -100 mV, Attenuator =1 | 8   | +/- 4     | 8   | mV    |

|            | (Differential Analog Inputs) <sup>1, 3</sup>                                                                   | Measurement Range 600 mV - 2.048 V,<br>VMONxGS > -200 mV, Attenuator =1 | -   | +/- 6     | -   | mV    |

|            |                                                                                                                | Measurement Range 0 - 2.048 V,<br>VMONxGS > -200 mV, Attenuator =1      | -   | +/-<br>10 | -   | mV    |

|            | Total Measurement Error at<br>Any Voltage (Single-Ended<br>Analog Inputs including<br>IMON) <sup>1, 2, 3</sup> | Measurement Range 600 mV - 2.048 V,<br>Attenuator =1                    | -8  | +/- 4     | 8   | mV    |

Notes:

- 1. Total error, guaranteed by characterization, includes INL, DNL, Gain, Offset, and PSR specs of the ADC.

- 2. Programmable gain error on IMON not included.

- 3. ADC accuracy may degrade based on SSO conditions of hardware management controller ASC-I/F. Refer to the System Connections section for more details.

## 5.10. Temperature Monitors

#### Table 5.9. Temperature Monitors

| Symbol                                              | Parameter                                              | Conditions                             | Min | Тур  | Max   | Units |

|-----------------------------------------------------|--------------------------------------------------------|----------------------------------------|-----|------|-------|-------|

| T <sub>MON_REMOTE</sub><br>Accuracy <sup>1, 7</sup> | Temp Error – Remote Sensor                             | Ta=-40 to +85 ºC Td=-64 to 150 ºC      | —   | 1    | -     | °C    |

| T <sub>MON_INT</sub><br>Accuracy <sup>7</sup>       | Internal Sensor – Relative to ambient <sup>6</sup>     | Ta=–40 to +85 ºC                       | -   | 1    | -     | °C    |

| T <sub>MON</sub><br>Resolution                      | Measurement Resolution                                 | -                                      | -   | 0.25 | -     | °C    |

| $T_{MON}$ Range                                     | Programmable threshold range                           | -                                      | -64 | -    | 155   | °C    |

| $T_{MON}$ Offset                                    | Temperature offset                                     | Programmable in software               | -64 | —    | 63.75 | °C    |

| T <sub>MON</sub><br>Hysteresis                      | Hysteresis of trip points                              | Programmable in software               | 0   | —    | 63    | °C    |

| $t_{\text{TMON}_{\text{settle}}^2}$                 | Temperature measurement                                | Measurement Averaging Coefficient = 1  | —   | 15   | _     | ms    |

|                                                     | settling time <sup>3</sup>                             | Measurement Averaging Coefficient = 8  | —   | 120  | -     | ms    |

|                                                     |                                                        | Measurement Averaging Coefficient = 16 | —   | 240  | -     | ms    |

| Tn                                                  | Ideality Factor n                                      | Programmable in software               | 0.9 | _    | 2     | _     |

| T <sub>limit</sub>                                  | Temperature measurement limit <sup>4</sup>             | -                                      | -   | -    | 160   | °C    |

| C <sub>TMON</sub>                                   | Maximum capacitance<br>between TMONP and<br>TMONN pins | _                                      | _   | _    | 200   | pF    |

| R <sub>TMONSeries</sub>                             | Equivalent external resistance to sensor <sup>5</sup>  | _                                      | _   | _    | 200   | Ω     |

<sup>© 2019-2023</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### Notes:

- 1. Accuracy number is valid for the use of a grounded collector pnp configuration, programmed with proper ideality factor, and 16x measurement filter enabled. Any other device or configuration can have additional errors, including beta, series resistance and ideality factor accuracy. Refer to the Temperature Monitors section for more details.

- 2. Settling time based on one TMON enabled. For multiple TMONs, settling time can be multiplied by the number of enabled TMON channels.

- 3. Settling time is defined as the time it takes a step change to settle to 1% of the measured value.

- 4. All values above T<sub>limit</sub> read as 0x3FF over I<sup>2</sup>C. There is no cold temperature limiting reading, although performance is not specified below –64 °C.

- 5. This is the maximum series resistance which the TMON circuit can compensate out. Equivalent series resistance includes all board trace wiring (TMONP and TMONN) as well as parasitic base and emitter resistances. Re=1/gm should not be included as part of series resistance.

- 6. Internal sensor is subject to self-heating, dependent on PCB design and device configuration. Self-heating not included in published accuracy.

- 7. TMON accuracy may degrade based on SSO conditions of hardware management controller ASC-I/F. Refer to the System Connections section for more details.

## 5.11. Digital Specifications

#### Table 5.10. Digital Specifications

| Symbol                           | Parameter                                         | Conditions                                                     | Min         | Тур | Max         | Units |

|----------------------------------|---------------------------------------------------|----------------------------------------------------------------|-------------|-----|-------------|-------|

| I <sub>IL</sub> ,I <sub>IH</sub> | Input Leakage, no pull-up, pull-down <sup>2</sup> | -                                                              | -           | _   | +/-<br>10   | μA    |

| I <sub>PD</sub>                  | Active Pull-Down Current <sup>2</sup>             | GPIO[1:10] configured as Inputs,<br>Internal Pull-Down enabled | -           | 200 | _           | μA    |

| I <sub>PD-ASCIF</sub>            | Input Leakage (WDAT and WRCLK) <sup>3</sup>       | Internal Pull-Down                                             | -           | 175 | -           | μA    |

| I <sub>он-нvout</sub>            | Output Leakage Current                            | HVOUT[1:4] in open drain mode and pulled up to 12 V            | -           | 35  | 100         | μA    |

| I <sub>PU-RESETb</sub>           | Input Pull-Up Current<br>(RESETb)                 | -                                                              | -           | -50 | -           | μA    |

| V <sub>IL</sub>                  | Voltage input, logic low                          | GPIO[1:10]                                                     | -           | _   | 0.8         | V     |

|                                  |                                                   | SCL, SDA                                                       | -           | -   | 30%<br>VCCA |       |

| V <sub>IH</sub>                  | Voltage input, logic high                         | GPIO[1:10]                                                     | 2.0         | —   | —           | V     |

|                                  |                                                   | SCL, SDA                                                       | 70%<br>VCCA | _   | _           |       |

| V <sub>OL</sub>                  | HVOUT[1:4] (open drain mode)                      | I <sub>SINK</sub> = 10 mA                                      | -           | _   | 0.8         | V     |

|                                  | GPIO[1:6], GPIO[8:10]                             | I <sub>SINK</sub> = 20 mA                                      |             |     |             |       |

| I <sub>SINKTOTAL</sub> 1         | All digital outputs                               |                                                                | _           | —   | 130         | mA    |

#### Notes:

- 1. Sum of maximum current sink from all digital outputs combined. Reliable operation is not guaranteed if this value is exceeded.

- 2. During safe-state, all GPIO default to output, refer to the Safe State of Digital Outputs section for more details. GPIO[1:6] and

- GPIO[10] default to active low output. This will result in a leakage current dependent on the input voltage which can exceed the specified input leakage.

- 3. WRCLK and WDAT pins may see transients above 1 mA in hot socket conditions. DC levels will remain below 1 mA.

© 2019-2023 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

## 5.12. High Voltage FET Drivers

#### Table 5.11. High Voltage FET Drivers

| Symbol               | Parameter                                         | Conditions                | Min  | Тур    | Max   | Units |

|----------------------|---------------------------------------------------|---------------------------|------|--------|-------|-------|

| V <sub>PP</sub>      | Gate driver output voltage                        | Four settings in software | -    | 12     | —     | Volts |

|                      |                                                   |                           | —    | 10     | —     |       |

|                      |                                                   |                           | _    | 8      | —     |       |

|                      |                                                   |                           | —    | 6      | —     |       |

| I <sub>OUTSRC</sub>  | Gate driver source current                        | Four settings in software | -    | 12.5   | —     | μA    |

|                      | (HIGH state)                                      |                           | —    | 25     | —     |       |

|                      |                                                   |                           | _    | 50     | —     |       |

|                      |                                                   |                           | _    | 100    | —     |       |

| I <sub>OUTSINK</sub> | Gate driver sink current (LOW                     | Four settings in software | _    | 100    | —     | μA    |

|                      | state)                                            |                           | —    | 250    | —     |       |

|                      |                                                   |                           | —    | 500    | —     |       |

|                      |                                                   |                           | _    | 3000   | —     |       |

| Frequency            | Switched Mode Frequency                           | Two settings in software  | _    | 15.625 | —     | kHz   |

|                      |                                                   |                           |      | 31.25  |       |       |

| Duty Cycle           | Switched Mode<br>Programmable Duty Cycle<br>Range | Programmable in software  | 6.25 | _      | 93.75 | %     |

|                      | Duty Cycle step size                              | —                         | -    | 6.25   | —     | %     |

### 5.13. Margin/Trim DAC Output Characteristics

#### Table 5.12. Margin/Trim DAC Output Characteristics

| Symbol                 | Parameter                                            | Conditions                                                    | Min  | Тур.            | Max. | Units |

|------------------------|------------------------------------------------------|---------------------------------------------------------------|------|-----------------|------|-------|

| -                      | Resolution                                           | -                                                             | -    | 8 (7 +<br>sign) | —    | Bits  |

| FSR                    | Full scale range                                     | _                                                             | -    | +/-<br>320      | _    | mV    |

| LSB                    | LSB step size                                        | -                                                             | -    | 2.5             | _    | mV    |

| I <sub>OUT</sub>       | Output source/sink current                           | -                                                             | -200 |                 | 200  | μA    |

| I <sub>TRIM_Hi-Z</sub> | Tri-state mode leakage                               | -                                                             | -    | 0.1             | —    | μA    |

| BPZ                    | Bipolar zero output voltage                          | Four settings in software                                     | -    | 0.6             | —    | V     |

|                        | (code=80h)                                           |                                                               | _    | 0.8             | —    |       |

|                        |                                                      |                                                               | _    | 1.0             | —    |       |

|                        |                                                      |                                                               | _    | 1.25            | —    |       |

| ts                     | TrimCell output voltage settling time <sup>1</sup>   | DAC code changed from 80H to FFH or<br>80H to 00H             | -    | _               | 2.5  | ms    |

| _                      | -                                                    | Single DAC code change                                        | -    | 256             | —    | μs    |

| C_LOAD                 | Maximum load capacitance                             | -                                                             | -    | —               | 50   | pF    |

| TOSE                   | Total open loop supply<br>voltage error <sup>2</sup> | Full scale DAC corresponds to +/- 5% supply voltage variation | -1%  | —               | +1%  | V/V   |

#### Notes:

1. To 1% of set value with 50 pF load connected to trim pins.

2. Total resultant error in the trimmed power supply output voltage referred to any DAC code due to DAC's INL, DNL, gain, output impedance, offset error and bipolar offset error across the temperature, and V<sub>CCA</sub> ranges of the device.

## 5.14. Fault Log

#### Table 5.13. Fault Log

| Symbol                    | Parameter                                                            | Conditions | Min | Тур. | Max. | Units   |

|---------------------------|----------------------------------------------------------------------|------------|-----|------|------|---------|

| Records                   | Number of available fault log records in EEPROM                      | _          |     | 16   | l    | Records |

| t <sub>faultTrigger</sub> | Minimum active time of<br>trigger signal to start fault<br>recording | _          | 64  | -    | -    | μs      |

| $t_{faultRecord}$         | Time to copy fault record to<br>EEPROM                               | -          |     |      | 5    | ms      |

| t <sub>faultWrite</sub>   | Time to complete writing fault record in EEPROM                      | _          | _   | _    | 10   | ms      |

### 5.15. Oscillator

#### Table 5.14. Oscillator

| Symbol             | Parameter                | Conditions | Min | Тур. | Max. | Units |

|--------------------|--------------------------|------------|-----|------|------|-------|

| CLK <sub>ASC</sub> | Internal ASC0 Clock      | _          | 7.6 | 8    | 8.4  | MHz   |

| CLK <sub>ext</sub> | Externally Applied Clock | —          | 7.6 | 8    | 8.4  | MHz   |

## 5.16. Propagation Delays

#### Table 5.15. Propagation Delays

| Symbol                                  | Parameter                                                    | Conditions                      | Min | Тур. | Max. | Units |

|-----------------------------------------|--------------------------------------------------------------|---------------------------------|-----|------|------|-------|

| Voltage Monit                           | ors                                                          |                                 |     |      |      |       |

| t <sub>VMONtoFPGA</sub>                 | Propagation delay VMON                                       | Glitch Filter Off               | _   | 48   | _    | μs    |

|                                         | input to signal update at FPGA                               | Glitch Filter ON                | _   | 96   | _    | μs    |

| $t_{\text{VMONtoOCB}}{}^2$              | Propagation delay VMON                                       | Glitch Filter Off               | —   | —    | 16   | μs    |

|                                         | input to output update at<br>OCB                             | Glitch Filter ON                | —   | —    | 64   | μs    |

| <b>Current Monite</b>                   | ors                                                          |                                 |     |      | _    |       |

| t <sub>IMONtoFPGA</sub>                 | Propagation delay IMON                                       | Glitch Filter Off               | —   | 48   | _    | μs    |

|                                         | input to signal update at FPGA                               | Glitch Filter ON                | -   | 96   | —    | μs    |

| $t_{\text{IMONtoOCB}}{}^2$              | Propagation delay IMON                                       | Glitch Filter Off               | _   | —    | 16   | μs    |

|                                         | input to output update at<br>OCB                             | Glitch Filter ON                | —   | —    | 64   | μs    |

| $t_{IMONFtoOCB}^2$                      | Propagation delay IMONF<br>input to output update at<br>OCB  | -                               |     | _    | 1    | μs    |

| Temperature N                           | Monitors                                                     |                                 |     |      |      |       |

| t <sub>tmontofpga</sub>                 | Propagation delay TMON                                       | Monitor Alarm Filter Depth = 1  | _   | 15   | _    | ms    |

|                                         | input to signal update at FPGA1                              | Monitor Alarm Filter Depth = 16 | -   | 240  | -    | ms    |

| GPIO – Inputs                           |                                                              |                                 |     |      |      |       |

| t <sub>gpiOtoFpga</sub>                 | Propagation delay GPIO input<br>to signal update at FPGA     | -                               | -   | 32   | -    | μs    |

| t <sub>GPIOtoOCB</sub> <sup>2</sup>     | Propagation delay GPIO input<br>to output update at OCB      | _                               | -   | —    | 50   | ns    |

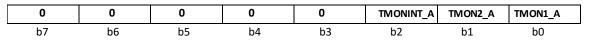

| GPIO – Output                           | s                                                            | •                               |     |      | •    |       |