Sample &

Buy

#### **OPT101**

SBBS002B – JANUARY 1994 – REVISED JUNE 2015

# **OPT101 Monolithic Photodiode and Single-Supply Transimpedance Amplifier**

Technical

Documents

## 1 Features

- Single Supply: 2.7 to 36 V

- Photodiode Size: 0.090 inch × 0.090 inch (2.29 mm × 2.29 mm)

- Internal 1-MΩ Feedback Resistor

- High Responsivity: 0.45 A/W (650 nm)

- Bandwidth: 14 kHz at  $R_F = 1 M\Omega$

- Low Quiescent Current: 120 µA

- Packages: Clear Plastic 8-pin PDIP and J-Lead SOP

## 2 Applications

- Medical Instrumentation

- Laboratory Instrumentation

- Position and Proximity Sensors

- Photographic Analyzers

- Barcode Scanners

- Smoke Detectors

- Currency Changers

## 3 Description

Tools &

Software

The OPT101 is a monolithic photodiode with on-chip transimpedance amplifier. The integrated combination of photodiode and transimpedance amplifier on a single chip eliminates the problems commonly encountered in discrete designs, such as leakage current errors, noise pick-up, and gain peaking as a result of stray capacitance. Output voltage increases linearly with light intensity. The amplifier is designed for single or dual power-supply operation.

The 0.09 inch  $\times$  0.09 inch (2.29 mm  $\times$  2.29 mm) photodiode operates in the photoconductive mode for excellent linearity and low dark current.

The OPT101 operates from 2.7 V to 36 V supplies and quiescent current is only 120  $\mu$ A. This device is available in clear plastic 8-pin PDIP, and J-lead SOP for surface mounting. The temperature range is 0°C to 70°C.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |

|-------------|----------|-------------------|

| OPT101      | PDIP (8) | 9.53 mm × 6.52 mm |

| OFTIOT      | SOP (8)  | 9.52 mm × 6.52 mm |

(1) For all available packages, see the package option addendum at the end of the data sheet.

## **Spectral Responsivity**

# **Table of Contents**

| 1 | Feat | tures                                   | 1              |

|---|------|-----------------------------------------|----------------|

| 2 | Арр  | lications                               | 1              |

| 3 | Des  | cription                                | 1              |

| 4 | Rev  | ision History                           | 2              |

| 5 | Pin  | Configuration and Functions             | 3              |

| 6 | Spe  | cifications                             | 4              |

|   | 6.1  | Absolute Maximum Ratings                | 4              |

|   | 6.2  | ESD Ratings                             | 4              |

|   | 6.3  | Recommended Operating Conditions        |                |

|   | 6.4  | Thermal Information                     | 4              |

|   | 6.5  | Electrical Characteristics              | <mark>5</mark> |

|   | 6.6  | Electrical Characteristics: Photodiode  | <mark>6</mark> |

|   | 6.7  | Electrical Characteristics: Op Amp      |                |

|   | 6.8  | Typical Characteristics                 | 7              |

| 7 | Para | ameter Measurement Information          | 10             |

|   | 7.1  | Light Source Positioning and Uniformity | 10             |

| 8 | Deta | ailed Description                       |                |

|   | 8.1  | Overview                                | 11             |

|   |      |                                         |                |

|    | 8.2  | Functional Block Diagram           | 11 |

|----|------|------------------------------------|----|

|    | 8.3  | Feature Description                | 12 |

|    | 8.4  | Device Functional Modes            | 15 |

| 9  | Арр  | lication and Implementation        | 16 |

|    | 9.1  | Application Information            | 16 |

|    | 9.2  | Typical Applications               | 17 |

|    | 9.3  | Dos and Don'ts                     | 22 |

| 10 | Pow  | ver-Supply Recommendations         | 23 |

| 11 | Lay  | out                                | 23 |

|    | 11.1 | Layout Guidelines                  | 23 |

|    | 11.2 | Layout Example                     | 23 |

| 12 | Dev  | ice and Documentation Support      | 24 |

|    | 12.1 | Community Resources                | 24 |

|    | 12.2 | Trademarks                         | 24 |

|    | 12.3 | Electrostatic Discharge Caution    | 24 |

|    | 12.4 | Moisture Sensitivity and Soldering | 24 |

|    | 12.5 | Glossary                           | 24 |

| 13 | Мес  | hanical, Packaging, and Orderable  |    |

|    | Info | mation                             | 24 |

|    |      |                                    |    |

## 4 Revision History

| CI | hanges from Revision A (October 2003) to Revision B                                                                                                                                                                                                                                                                 | Page |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added Pin Functions, ESD Ratings, Recommended Operating Conditions, and Thermal information tables, and<br>Parameter Measurement Information, Detailed Description, Application and Implementation, Power-Supply<br>Recommendations, Layout, and Device and Documentation Support sections; moved existing sections | 1    |

| •  | Deleted W version of device from Tolerance parameter of Electrical Characteristics table; W version now obsolete                                                                                                                                                                                                    | 5    |

| •  | Changed Application Information section                                                                                                                                                                                                                                                                             | 16   |

www.ti.com

#### OPT101 SBBS002B – JANUARY 1994 – REVISED JUNE 2015

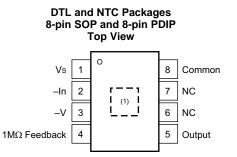

# 5 Pin Configuration and Functions

(1) Photodiode location.

#### **Pin Functions**

|     | PIN I/O      |        | DESCRIPTION                                                                                                             |  |

|-----|--------------|--------|-------------------------------------------------------------------------------------------------------------------------|--|

| NO. |              |        |                                                                                                                         |  |

| 1   | Vs           | Power  | Power supply of device. Apply 2.7 V to 36 V relative to -V pin.                                                         |  |

| 2   | –In          | Input  | Negative input of op amp and the cathode of the photodiode. Either do not connect, or apply additional op amp feedback. |  |

| 3   | -V           | Power  | Most negative power supply. Connect to ground or a negative voltage that meets the recommended operating conditions.    |  |

| 4   | 1MΩ Feedback | Input  | Connection to internal feedback network. Typically connect to Output, pin 5.                                            |  |

| 5   | Output       | Output | Output of device.                                                                                                       |  |

| 6   | NC           | _      | Do not connect                                                                                                          |  |

| 7   | NC           | —      | Do not connect                                                                                                          |  |

| 8   | Common       | Input  | Anode of the photodiode. Typically, connect to ground.                                                                  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                                         |                                  | MIN | MAX        | UNIT |

|---------------------------------------------------------|----------------------------------|-----|------------|------|

| Supply voltage (V <sub>S</sub> to Common pin or –V pin) |                                  | 0   | 36         | V    |

| Output short-circui                                     | Output short-circuit (to ground) |     | Continuous |      |

|                                                         | Operating                        | -25 | 85         | °C   |

| Temperature                                             | Junction                         |     | 85         | °C   |

|                                                         | Storage, T <sub>stg</sub>        | -25 | 85         | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                                                                   |                                                                                | VALUE | UNIT |

|--------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000                                                                          | V     |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                           | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   | MIN | NOM MAX | UNIT |

|-------------------|-----|---------|------|

| POWER SUPPLY      |     |         |      |

| Operating voltage | 2.7 | 36      | V    |

| TEMPERATURE       |     |         |      |

| Specified         | 0   | 70      | °C   |

| Operating         | 0   | 70      | °C   |

### 6.4 Thermal Information

|                       |                                              |           | OPT101     |      |

|-----------------------|----------------------------------------------|-----------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DTL (SOP) | NTC (PDIP) | UNIT |

|                       |                                              | 8 PINS    | 8 PINS     |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 138.6     | 128.2      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 96.4      | 113.1      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 126.6     | 107.0      | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 17.8      | 24.2       | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 118.8     | 105.9      | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

At  $T_A = 25^{\circ}$ C,  $V_S = 2.7$  V to 36 V,  $\lambda = 650$  nm, internal 1-M $\Omega$  feedback resistor, and  $R_L = 10$  k $\Omega$  (unless otherwise noted)

|         | PARAMETER                         | TEST CONDITIONS                                                          | MIN TY                    | P MAX  | UNIT            |

|---------|-----------------------------------|--------------------------------------------------------------------------|---------------------------|--------|-----------------|

| RESPONS | SIVITY                            |                                                                          |                           |        | I               |

|         | Photodiode current                |                                                                          | 0.4                       | 45     | A/W             |

|         | Voltage output                    |                                                                          | 0.4                       | 45     | V/µW            |

|         | Voltage output vs temperature     |                                                                          | 10                        | 00     | ppm/°C          |

|         | Unit-to-unit variation            |                                                                          | ±5                        | %      |                 |

|         | Nonlinearity <sup>(1)</sup>       | Full-scale (FS) output = 24 V                                            | ±0.0                      | 01     | % of FS         |

|         | Dhatadiada avaa                   | 0.090 in × 0.090 in                                                      | 0.0                       | 08     | in <sup>2</sup> |

|         | Photodiode area                   | 2.29 mm × 2.29 mm                                                        | 5                         | .2     | mm <sup>2</sup> |

| DARK ER | RORS, RTO <sup>(2)</sup>          |                                                                          | <u>.</u>                  |        |                 |

|         | Offset voltage, output            |                                                                          | 5 7                       | .5 10  | mV              |

|         | Offset voltage vs temperature     |                                                                          | ±                         | 10     | µV/°C           |

|         | Offset voltage vs power supply    | $V_{\rm S} = 2.7 \text{ V to } 36 \text{ V}$                             |                           | 10 100 | μV/V            |

|         | Voltage noise, dark               | $f_{\rm B}$ = 0.1 Hz to 20 kHz, V_{\rm S} = 15 V, $V_{\rm PIN3}$ = –15 V | 30                        | 00     | µVrms           |

| TRANSIM | PEDANCE GAIN                      |                                                                          | <u>.</u>                  |        |                 |

|         | Resistor                          |                                                                          |                           | 1      | MΩ              |

|         | Tolerance                         |                                                                          | ±0.5                      | % ±2%  |                 |

|         | Tolerance vs temperature          |                                                                          | ±                         | 50     | ppm/°C          |

| FREQUEN | ICY RESPONSE                      |                                                                          |                           |        |                 |

|         | Bandwidth                         | $V_{OUT} = 10 V_{PP}$                                                    |                           | 14     | kHz             |

|         | Rise and fall time                | 10% to 90%, V <sub>OUT</sub> = 10-V step                                 | :                         | 28     | μs              |

|         |                                   | to 0.05%, V <sub>OUT</sub> = 10-V step                                   | 16                        | 60     | μs              |

|         | Settling time                     | to 0.1%, V <sub>OUT</sub> = 10-V step                                    | 1                         | 30     | μs              |

|         |                                   | to 1%, V <sub>OUT</sub> = 10-V step                                      | -                         | 70     | μs              |

|         | Overload recovery                 | 100%, return to linear operation                                         |                           | 50     | μs              |

| OUTPUT  |                                   |                                                                          |                           |        |                 |

|         | Voltage output, high              |                                                                          | $(V_S) - 1.3 (V_S) - 1.7$ | 15     | V               |

|         | Capacitive load, stable operation |                                                                          |                           | 10     | nF              |

|         | Short-circuit current             | V <sub>S</sub> = 36 V                                                    |                           | 15     | mA              |

| POWER S | UPPLY                             |                                                                          |                           |        |                 |

|         |                                   | Dark, V <sub>PIN3</sub> = 0 V                                            | 1:                        | 20     | μA              |

|         | Quiescent current                 | R <sub>L</sub> = ∞, V <sub>OUT</sub> = 10 V                              | 22                        | 20     | μA              |

(1) Deviation in percent of full scale from best-fit straight line.

(2) Referred to output. Includes all error sources.

## 6.6 Electrical Characteristics: Photodiode

At  $T_A = 25^{\circ}$ C and  $V_S = 2.7$  V to 36 V (unless otherwise noted)

| PARAMETER                   | TEST CONDITIONS                     | MIN TYP MA        | X UNIT          |

|-----------------------------|-------------------------------------|-------------------|-----------------|

| Photodiode area             | 0.090 in × 0.090 in                 | 0.008             | in <sup>2</sup> |

| Filotodiode alea            | 2.29 mm × 2.29 mm                   | 5.2               | mm <sup>2</sup> |

|                             |                                     | 0.45              | A/W             |

| Current responsivity        | λ = 650 nm                          | 865               | (µA/W)/cm       |

| Dark current                | V <sub>DIODE</sub> = 7.5 mV         | 2.5               | pА              |

| Dark current vs temperature | $V_{\text{DIODE}} = 7.5 \text{ mV}$ | Doubles every 7°C | —               |

| Capacitance                 |                                     | 1200              | pF              |

## 6.7 Electrical Characteristics: Op Amp<sup>(1)</sup>

At  $T_A = 25^{\circ}$ C,  $V_S = 2.7$  V to 36 V,  $\lambda = 650$  nm, internal 1-M $\Omega$  feedback resistor, and  $R_L = 10$  k $\Omega$  (unless otherwise noted)

| PARAMETER                             | TEST CONDITIONS                             | MIN TYP MAX                                      | UNIT     |

|---------------------------------------|---------------------------------------------|--------------------------------------------------|----------|

| INPUT                                 |                                             |                                                  |          |

| Offset voltage                        |                                             | ±0.5                                             | mV       |

| vs temperature                        |                                             | ±2.5                                             | µV/°C    |

| vs power supply                       |                                             | 10                                               | μV/V     |

| Input bias current                    | (–) input                                   | 165                                              | pА       |

| vs temperature                        | (–) input                                   | Doubles every 10°C                               | _        |

|                                       | Differential                                | 400    5                                         | MΩ    pF |

| Input impedance                       | Common-mode                                 | 250    35                                        | GΩ∥pF    |

| Common-mode input voltage range       | Linear operation                            | 0 to (V <sub>S</sub> – 1)                        | V        |

| Common-mode rejection                 |                                             | 90                                               | dB       |

| OPEN-LOOP GAIN                        |                                             |                                                  |          |

| Open-loop voltage gain                |                                             | 90                                               | dB       |

| FREQUENCY RESPONSE                    |                                             |                                                  |          |

| Gain bandwidth product <sup>(2)</sup> |                                             | 2                                                | MHz      |

| Slew rate                             |                                             | 1                                                | V/µs     |

|                                       | 0.05%                                       | 8.0                                              | μs       |

| Settling time                         | 0.1%                                        | 7.7                                              | μs       |

|                                       | 1%                                          | 5.8                                              | μs       |

| OUTPUT                                |                                             |                                                  |          |

| Voltage output, high                  |                                             | (V <sub>S</sub> ) - 1.3 (V <sub>S</sub> ) - 1.15 | V        |

| Short-circuit current                 | V <sub>S</sub> = 36 V                       | 15                                               | mA       |

| POWER SUPPLY                          |                                             |                                                  |          |

| Quiescent current                     | Dark, V <sub>PIN3</sub> = 0 V               | 120                                              | μA       |

| Quiescent current                     | R <sub>L</sub> = ∞, V <sub>OUT</sub> = 10 V | 220                                              | μA       |

Op amp specifications provided for information and comparison only. Stable gains  $\geq$  10 V/V. (1)

(2)

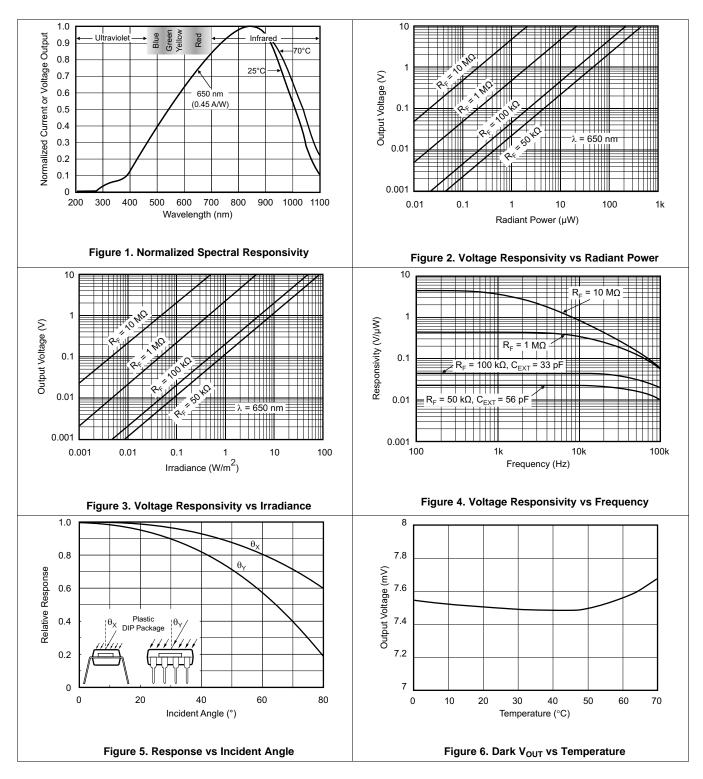

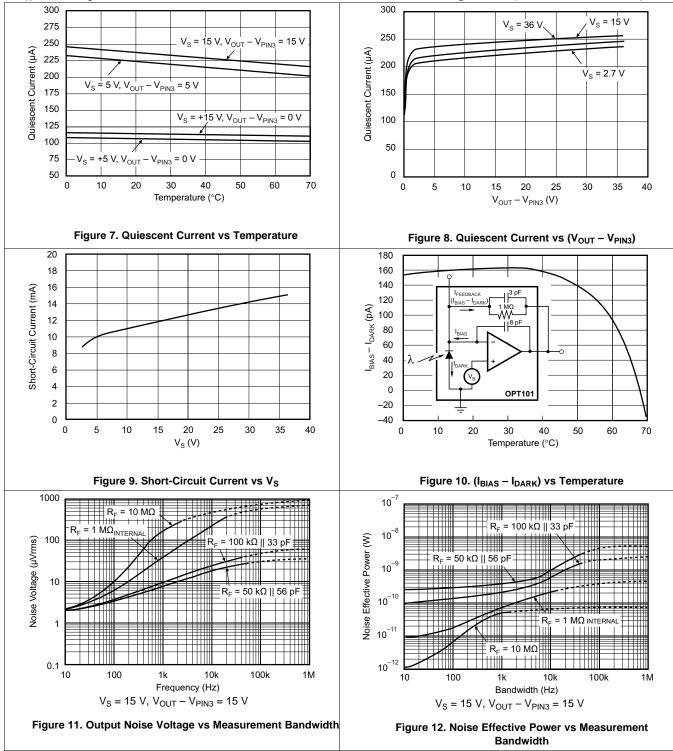

### 6.8 Typical Characteristics

At  $T_A = 25^{\circ}$ C,  $V_S = 2.7$  V to 36 V,  $\lambda = 650$  nm, internal 1-M $\Omega$  feedback resistor, and  $R_L = 10$  k $\Omega$  (unless otherwise noted)

## **Typical Characteristics (continued)**

At  $T_A = 25^{\circ}$ C,  $V_S = 2.7$  V to 36 V,  $\lambda = 650$  nm, internal 1-M $\Omega$  feedback resistor, and  $R_L = 10$  k $\Omega$  (unless otherwise noted)

### **Typical Characteristics (continued)**

At  $T_A = 25^{\circ}$ C,  $V_S = 2.7$  V to 36 V,  $\lambda = 650$  nm, internal 1-M $\Omega$  feedback resistor, and  $R_L = 10$  k $\Omega$  (unless otherwise noted)

## 7 Parameter Measurement Information

### 7.1 Light Source Positioning and Uniformity

The OPT101 is tested with a light source that uniformly illuminates the full area of the integrated circuit, including the op amp. Although the silicon of integrated circuit (IC) amplifiers is light-sensitive to some degree, the OPT101 op amp circuitry is designed to minimize this effect. Sensitive junctions are shielded with metal, and the photodiode area is very large relative to the op amp input circuitry.

If the light source is focused to a small area, be sure that it is properly aimed to fall on the photodiode. A narrowly-focused beam falling only on the photodiode provides improved settling times compared to a source that uniformly illuminates the full area of the die. If a narrowly-focused light source misses the photodiode area and falls only on the op amp circuitry, the OPT101 does not perform properly. The large 0.09-in  $\times$  0.09-in (2.29 mm  $\times$  2.29 mm) photodiode area allows easy positioning of narrowly-focused light sources. The photodiode area is easily visible because the area appears very dark compared to the surrounding active circuitry.

The incident angle of the light source also effects the apparent sensitivity in uniform irradiance. For small incident angles, the loss in sensitivity is simply due to the smaller effective light gathering area of the photodiode (proportional to the cosine of the angle). At a greater incident angle, light is diffracted and scattered by the package. These effects are shown in Figure 5.

## 8 Detailed Description

## 8.1 Overview

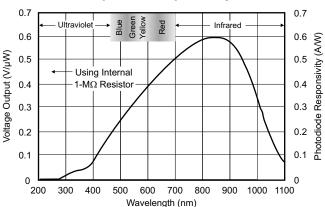

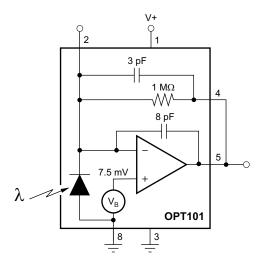

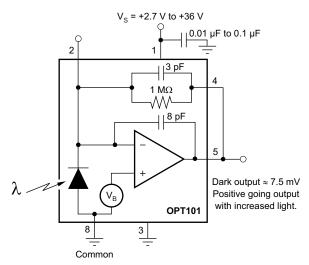

The OPT101 is a large-area photodiode integrated with an optimized operational amplifier that makes the OPT101 a small, easy-to-use, light-to-voltage device. The photodiode has a very large measurement area that collects a significant amount of light, and thus allows for high-sensitivity measurements. The photodiode has a wide spectral response with a maximum peak in the infrared spectrum, and a useable range from 300 nm to 1100 nm. The wide power-supply range of 2.7 V to 36 V makes this device useful in a variety of architectures; from all-analog circuits to data conversion base circuits. The on-chip voltage source keeps the amplifier in a good operating region, even at low light levels.

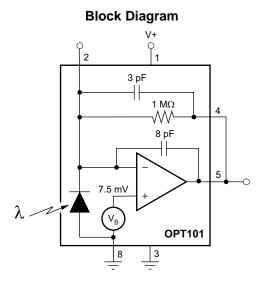

The OPT101 voltage output is the product of the photodiode current times the feedback resistor,  $(I_DR_F)$ , plus a pedestal voltage,  $V_B$ , of approximately 7.5 mV introduced for single-supply operation. Output is 7.5 mV dc with no light, and increases with increasing illumination. Photodiode current,  $I_D$ , is proportional to the radiant power, or flux, (in watts) falling on the photodiode. At a wavelength of 650 nm (visible red) the photodiode responsivity,  $R_I$ , is approximately 0.45 A/W. Responsivity at other wavelengths is shown in Figure 1. The internal feedback resistor is laser trimmed to 1 M $\Omega$ . Using this resistor, the output voltage responsivity,  $R_V$ , is approximately 0.45 V/ $\mu$ W at 650-nm wavelength.

See Figure 2 for the response throughout a wide range of radiant power in microwatts. Figure 3 shows the response throughout a wide range of irradiance in watts per square meter.

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Dark Performance

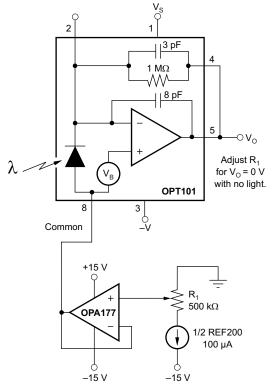

The dark errors in the *Electrical Characteristics* table include all sources. The dominant source of dark output voltage is the pedestal voltage applied to the noninverting input of the op amp. This voltage is introduced to provide linear operation in the absence of light falling on the photodiode. Photodiode dark current is approximately 2.5 pA, and contributes virtually no offset error at room temperature. The bias current of the op amp summing junction (negative input) is approximately 165 pA. The dark current is subtracted from the amplifier bias current, and this residual current flows through the feedback resistor creating an offset. The effects of temperature on this difference current are seen in Figure 10. The dark output voltage is trimmed to zero with the optional circuit shown in Figure 17. Use a low-impedance offset driver (op amp) to drive pin 8 (Common) because this node has signal-dependent currents.

Figure 17. Dark Error (Offset) Adjustment Circuit

#### Feature Description (continued)

#### 8.3.2 Feedback Network and Dynamic Response

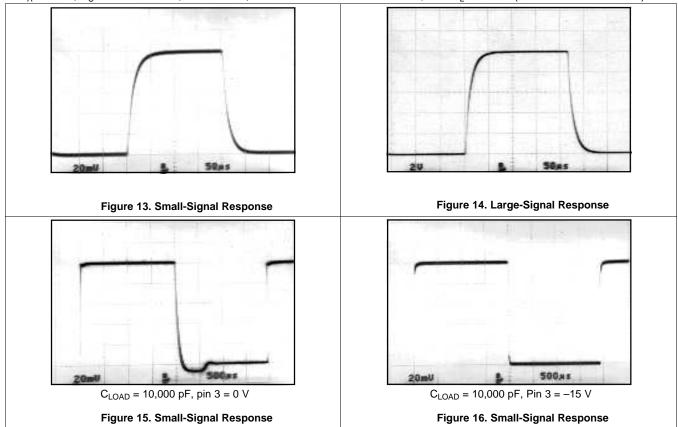

The OPT101 features a feedback network for optimal dynamic response. The dynamic response of the OPT101 is dominated by the feedback network and op amp combination. Using the internal 1-M $\Omega$  resistor, the dynamic response of the photodiode and op amp combination can be modeled as a simple RC circuit with a -3-dB cutoff frequency of approximately 14 kHz. The R and C values are 1 M $\Omega$  and 11 pF, respectively. To improve the frequency response, use external resistors with less than 3-pF parasitic capacitance. An external 1-M $\Omega$  resistor used in the configuration shown in Figure 19 creates a 23-kHz bandwidth with the same 106 V/A dc transimpedance gain. This increased bandwidth yields a rise time of approximately 15  $\mu$ s (10% to 90%). Dynamic response is not limited by op amp slew rate, as demonstrated in Figure 13 and Figure 14, showing virtually identical large-signal and small-signal response.

Dynamic response varies with feedback network value, as shown in Figure 4. Rise time (10% to 90%) varies as a function of the –3-dB bandwidth produced by the feedback network value shown in Equation 1:

$t_r = 0.35 \ / \ f_C$

where

- $t_r$  is the rise time (10% to 90%)

- f<sub>C</sub> is the -3dB bandwidth

#### 8.3.2.1 Changing Responsivity

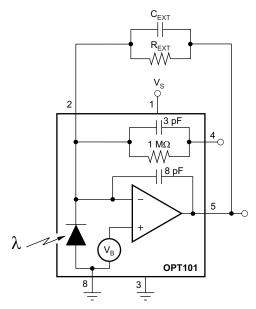

To set a different voltage responsivity, connect an external resistor,  $R_{EXT}$ . To increase the responsivity, place this resistor in series with the internal 1-M $\Omega$  resistor (Figure 18), or replace the internal resistor with an external resistor by not connecting pin 4 (Figure 19). The second configuration also reduces the circuit gain below 106 V/A when using external resistors that are less than 1 M $\Omega$ .

| Figure 18. | Changing Responsivity | with External | <b>Resistor in</b> | Series with | Internal Resistor |

|------------|-----------------------|---------------|--------------------|-------------|-------------------|

|------------|-----------------------|---------------|--------------------|-------------|-------------------|

| R <sub>EXT</sub><br>(MΩ) | C <sub>EXT</sub><br>(pF) | DC Gain<br>(× 10 <sup>6</sup> V/A) | Bandwidth<br>(kHz) |

|--------------------------|--------------------------|------------------------------------|--------------------|

| 1                        | 50                       | 2                                  | 8                  |

| 2                        | 25                       | 3                                  | 6                  |

| 5                        | 10                       | 6                                  | 2.5                |

| 10                       | 5                        | 11                                 | 1.3                |

| 50                       |                          | 51                                 | 0.33               |

#### Table 1. Responsivity and Bandwidth for Figure 18

Copyright © 1994–2015, Texas Instruments Incorporated

### Figure 19. Changing Responsivity with External Resistor Only (Internal Resistor Disabled)

|                          | • •                      | •                                  |                    |

|--------------------------|--------------------------|------------------------------------|--------------------|

| R <sub>EXT</sub><br>(MΩ) | C <sub>EXT</sub><br>(pF) | DC Gain<br>(× 10 <sup>6</sup> V/A) | Bandwidth<br>(kHz) |

| 0.05 <sup>(1)</sup>      | 56                       | 0.05                               | 58                 |

| 0.1 <sup>(1)</sup>       | 33                       | 0.1                                | 44                 |

| 1                        | —                        | 1                                  | 23                 |

| 2                        | —                        | 2                                  | 9.4                |

| 5                        | _                        | 5                                  | 3.6                |

| 10                       | —                        | 10                                 | 1.8                |

| 50                       | _                        | 50                                 | 0.34               |

#### Table 2. Responsivity and Bandwidth for Figure 19

(1) May require 1 k $\Omega$  in series with pin 5 when driving large capacitances.

Applications using a feedback resistor significantly larger than the internal 1-M $\Omega$  resistor require special consideration. Input bias current of the op amp and dark current of the photodiode increase significantly at higher temperatures. This increase combined with the higher gain (R<sub>F</sub> > 1 M $\Omega$ ) can cause the op amp output to be driven to ground at high temperatures. If this problem occurs, use a positive bias voltage applied to pin 8 to make sure that the op amp output remains in the linear operating region when the photodiode is not exposed to light. Alternatively, use a dual power supply. The output may be negative when sensing dark conditions. Use the information discussed in the *Dark Performance* section and Figure 10 to analyze the desired configuration.

#### 8.3.3 Noise Performance

Noise performance of the OPT101 is determined by the op amp characteristics, feedback network, photodiode capacitance, and signal level. Figure 11 shows how the noise varies with  $R_F$  and measured bandwidth (0.1 Hz to the indicated frequency), when the output voltage minus the voltage on pin 3 (–V) is greater than approximately 50 mV. Below this level, the output stage is powered down, and the effective bandwidth is decreased. This decreased bandwidth reduces the noise to approximately 1/3 the nominal noise value of 300  $\mu$ Vrms, or 100  $\mu$ Vrms. This decreased bandwidth enables a low-level signal to be resolved.

To reduce noise and improve the signal-to-noise ratio, filter the output with a cutoff frequency equal to the signal bandwidth. In addition, output noise increases in proportion to the square root of the feedback resistance, while responsivity increases linearly with feedback resistance. To improve the signal-to-noise ratio performance, use large feedback resistance, if decreased bandwidth is acceptable to the application.

The noise performance of the photodetector is sometimes characterized by noise effective power (NEP), the radiant <u>power</u> that produces an output signal equal to the noise level. NEP has the units of radiant power (watts), or  $W/\sqrt{Hz}$  to convey spectral information about the noise. Figure 12 illustrates the NEP for the OPT101.

#### 8.3.4 Linearity Performance

The photodiode is operated in the photoconductive mode so the current output of the photodiode is very linear with radiant power throughout a wide range. Nonlinearity remains less than approximately 0.05% for photodiode currents less than 100- $\mu$ A. The photodiode is able to produce output currents of 1 mA or greater with high radiant power, but nonlinearity increases to several percent in this region.

This very linear performance at high radiant power assumes that the full photodiode area is uniformly illuminated. If the light source is focused to a small area of the photodiode, nonlinearity occurs at lower radiant power.

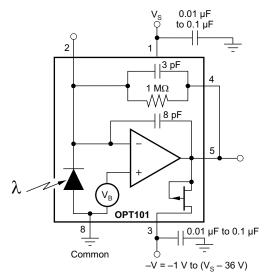

#### 8.3.5 Capacitive Load Drive

The OPT101 is capable of driving load capacitances of 10 nF without instability. However, dynamic performance with capacitive loads may improve by applying a negative bias voltage to pin 3 (–V, shown in Figure 20). This negative power-supply voltage allows the output to go negative in response to the reactive effect of a capacitive load. An internal JFET connected between pin 5 (output) and pin 3 (–V) allows the output to sink current. This current sink capability is also useful when driving the capacitive inputs of some analog-to-digital converters that require the signal source to sink currents up to approximately 100  $\mu$ A. The benefits of this current sink are shown in Figure 15 and Figure 16. These figures compare operation with pin 3 (–V) grounded and connected to –15 V.

Figure 20. Bipolar Power-Supply Circuit Connections

Because of the architecture of this output stage current sink, there is a slight increase in operating current when there is a voltage between pin 3 (–V) and the output. Depending on the magnitude of this voltage, the quiescent current increases by approximately 100  $\mu$ A, as shown in Figure 8.

### 8.4 Device Functional Modes

The OPT101 has a single functional mode and is operational when the power-supply voltage is greater than 2.7 V. The maximum power supply voltage for the OPT101 is 36 V.

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

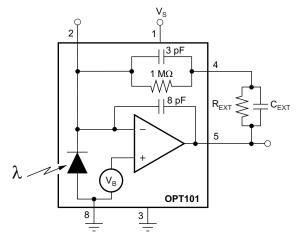

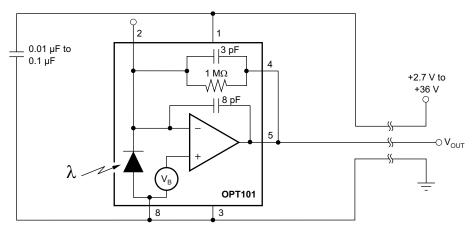

Figure 21 shows the basic circuit connections for the OPT101 operating with a single power supply and using the internal 1-M $\Omega$  feedback resistor for a response of 0.45 V/ $\mu$ W at 650 nm. Pin 3 (–V) is connected to common in this configuration. Applications with high-impedance power supplies may require decoupling capacitors located close to the device pins as shown.

Figure 21. Basic Circuit Connections

### 9.2 Typical Applications

#### 9.2.1 Color and Reflective Wavelength Tester

A common application for the OPT101 is testing physical materials. Information can be gained about a test material by determining the optical reflection, transmission, or absorption properties at particular wavelengths. These test materials can be solid objects, biological or chemical liquids, or any other type of material.

For an intuitive example, this application for OPT101 tests red, green, and blue reflective color properties of a variety of test materials. This application is not intended to match the color standards as defined by the Commission Internationale de l'Eclairage (CIE), but to illustrate a generic optical wavelength-specific test technique. Different applications can test for different wavelengths, including invisible ultraviolet or infrared wavelengths, that are appropriate for the objective of that application.

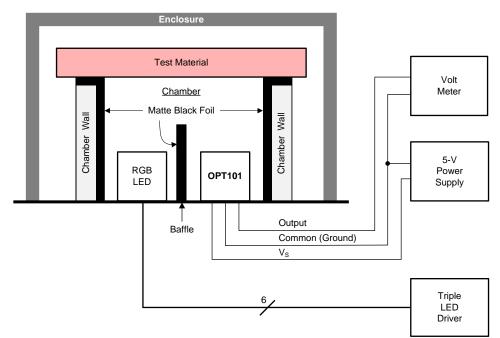

### Figure 22. Fixture for Measurement of Optical Reflective Properties of a Test Material

### 9.2.1.1 Design Requirements

For this design example, use the parameters listed in Table 3 as the input design requirement parameters.

| DESIGN PARAMETER                                                   | VALUE      |

|--------------------------------------------------------------------|------------|

| Input power supply voltage                                         | 5 V        |

| Room ambient light condition                                       | < 2000 lux |

| Ratio of blue and green response to red response, for red target   | < 60%      |

| Ratio of red and green response to blue response, for blue target  | < 60%      |

| Ratio of red and blue response to green response, for green target | < 80%      |

#### Table 3. Design Parameters

#### 9.2.1.2 Detailed Design Procedure

This design illuminates a test material with specific wavelengths, and measures the resulting reflection. Choose an RGB LED that sequentially creates individual red, green, and blue wavelengths. Red material has a strong reflection of red wavelengths, and a weaker reflection of green and blue wavelengths. Green and blue materials follow a similar pattern, reflecting the respective primary color wavelengths stronger than other color wavelengths.

Design a fixture with a chamber that allows the RGB LED to illuminate the test material and allows the OPT101 to receive the resulting reflection, as shown in Figure 22. Design the chamber to keep out ambient light from the room. Line the chamber with a matte black foil so that the chamber walls absorb as much light as possible. The matte black foil helps the OPT101 sensor measure reflections primarily from the test material and only minimally from the chamber walls. Design a baffle structure between the RGB LED and the OPT101 sensor so that light does not transmit directly from the RGB LED to the OPT101 sensor without reflecting off of the test material. Place an additional enclosure over the chamber to enhance the isolation from any light in the room.

Drive the OPT101 power supply pin,  $V_S$ , with a 5-V power supply, and measure the output pin voltage with a voltmeter. This voltmeter can easily be replaced with an ADC.

Choose LED drive currents for each of the RGB LEDs. Throughout this procedure, either drive each LED with this specific chosen current, or do not drive the LED at all. Choose an LED drive current that equalizes the power dissipation (the drive current times the forward-biased voltage drop across each LED). This equal power dissipation minimizes thermal transient settling time when switching between the LEDs. This equal power dissipation is not a requirement if test speed and settling time are not an issue for the application.

Calibrate the fixture by measuring a standard white card as a test material. Drive the red LED, and record the resulting voltage from the OPT101. Repeat this procedure with the green and blue LEDs.

Next, measure a test material with the same procedure used for the white card. Normalize the results by dividing the test material result by the white card result for each LED. Determine the color of the object by selecting the largest of the three LED normalized measurements. Perform an additional normalization step for data clarity by dividing each of the three LED measurements by the largest of the three measurements.

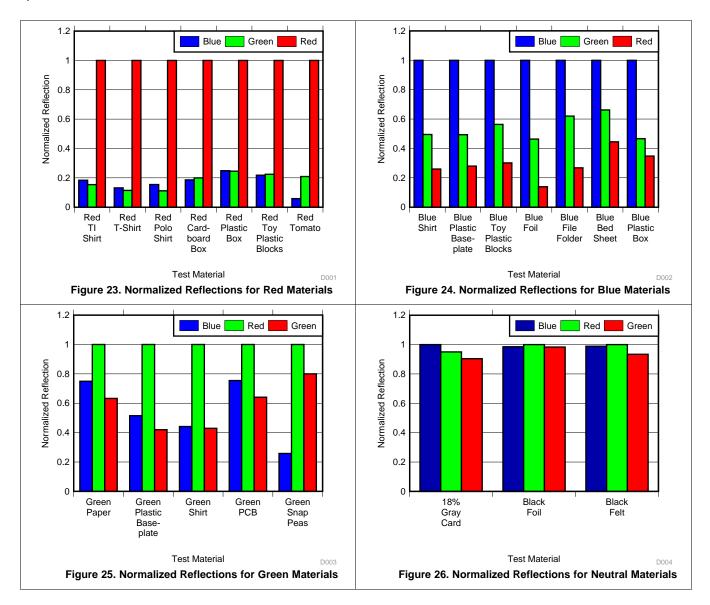

#### 9.2.1.3 Application Curves

The following figures show that the colors of the test materials sorted properly, as expected. The red test materials all showed a stronger reflection for red LED than the green and blue LEDs. The results are plotted in four groups: red (Figure 23, blue (Figure 24), green (Figure 25), and neutral color (Figure 26). The application clearly identifies the primary color of each test material. When the color is neutral, then the red, green, and blue test results are very similar to each other, as expected (within 10% of each other).

The red results had the most contrast. The green results had the least contrast. These results are likely different because the red LED has the least spectral overlap with the green and blue LEDs. The green LED has the widest spectral content. If more contrast is required, try LEDs (or other light sources) with more-narrow spectrums.

**OPT101**

SBBS002B - JANUARY 1994 - REVISED JUNE 2015

#### 9.2.2 Three-Wire Remote Light Measurement

Use the connections to the OPT101 shown on the right side of Figure 27 to sense a remote location with a threewire light measurement circuit.

Figure 27. Three-Wire Remote Light Measurement

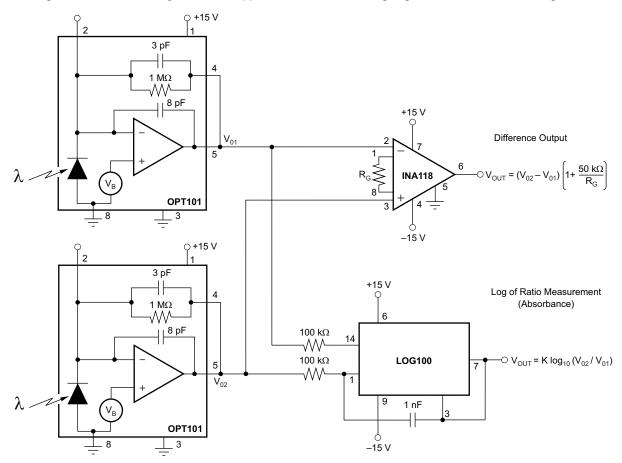

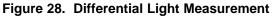

#### 9.2.3 Differential Light Measurement

Use a configuration similar to Figure 28 for applications that sense light gradients or differential light.

#### 9.2.4 LED Output Regulation Circuit

To keep an LED (or other light) producing a constant amount of light over changing temperature and over the lifetime efficiency degradation of the LED, use a circuit similar to Figure 29. As the efficiency of the LED degrades, this circuit increases the LED drive current to keep the output at the appropriate constant level.

Figure 29. LED Output Regulation Circuit

#### 9.3 Dos and Don'ts

As with any optical product, special care must be taken into consideration when handling the OPT101. Although the OPT101 has low sensitivity to dust and scratches, proper optical device handling procedures are still recommended.

The optical surface of the device must be kept clean for optimal performance in both prototyping with the device and mass production manufacturing procedures. Tweezers with plastic or rubber contact surfaces are recommended to avoid scratches on the optical surface. Avoid manipulation with metal tools when possible. The optical surface must be kept clean of fingerprints, dust, and other optical-inhibiting contaminants.

If the device optical surface requires cleaning, use deionized water or isopropyl alcohol. A few gentile brushes with a soft swab are appropriate. Avoid potentially abrasive cleaning and manipulating tools and excessive force that can scratch the optical surface.

If the OPT101 performs less than optimally, inspect the optical surface for dirt, scratches, or other optical artifacts.

Any light falling on the op amp circuitry area must be uniform; see the *Parameter Measurement Information* section for more information about light uniformity.

## **10** Power-Supply Recommendations

The OPT101 is designed to operate from an input voltage supply range between 2.7 V and 36 V. Make sure the power-supply input is well regulated. Place a 0.01- $\mu$ F to 0.1- $\mu$ F bypass capacitor with low-impedance, short connections between V<sub>S</sub> (pin 1) and -V (pin 3). If -V (pin 3) is not connected to Common (pin 8), place an additional bypass capacitor between V<sub>S</sub> (pin 1) and Common (pin 8).

## 11 Layout

### 11.1 Layout Guidelines

Make all power connections with short, low impedance connections.

Depending on the application, the design might benefit from having the OPT101 mounted to the opposite side of the board as the other electrical components. Keeping the optical sensor side free from extra components allows for easier mounting of any required optical-mechanical structures around the OPT101.

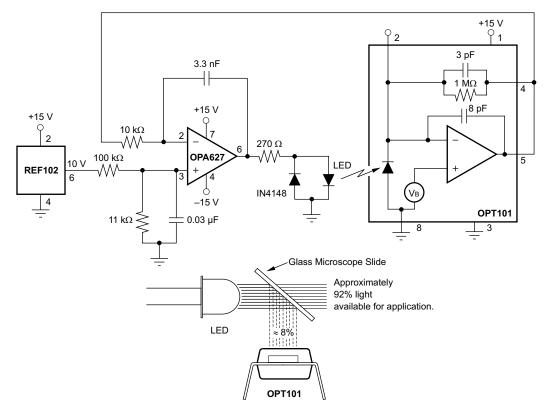

#### 11.2 Layout Example

The following example shows an external feedback network (R2 and C2) that bypasses the internal feedback network, similar to Figure 19. This example also shows an external feedback network (R1, C1) in series with the internal feedback network, similar to Figure 18. To use only the internal feedback network, load R1 or C1 with a short circuit. This example allows for three different configurations with the same layout. Do not load R1, C1, R2, and C2 simultaneously.

Figure 30. Layout Example

## **12 Device and Documentation Support**

#### 12.1 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.2 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 12.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 12.4 Moisture Sensitivity and Soldering

Clear plastic does not contain the structural-enhancing fillers used in black plastic molding compound. As a result, clear plastic is more sensitive to environmental stress than black plastic. This can cause difficulties if devices have been stored in high humidity prior to soldering. The rapid heating during soldering can stress wire bonds and cause failures. Prior to soldering, it is recommended that plastic devices be baked-out at 85°C for 24 hours.

The fire-retardant fillers used in black plastic are not compatible with clear molding compound. The OPT101 plastic packages cannot meet flammability test, UL-94.

#### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| OPT101P          | ACTIVE        | PDIP         | NTC                | 8    | 50             | RoHS & Green    | NIPDAU                               | N / A for Pkg Type   | 0 to 70      | OPT101                  | Samples |

| OPT101P-J        | ACTIVE        | SOP          | DTL                | 8    | 50             | RoHS & Green    | NIPDAU                               | Level-4-250C-72 HR   | 0 to 70      | OPT101                  | Samples |

| OPT101P-JG4      | ACTIVE        | SOP          | DTL                | 8    | 50             | RoHS & Green    | NIPDAU                               | Level-4-250C-72 HR   | 0 to 70      | OPT101                  | Samples |

| OPT101PG4        | ACTIVE        | PDIP         | NTC                | 8    | 50             | RoHS & Green    | NIPDAU                               | N / A for Pkg Type   | 0 to 70      | OPT101                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

10-Dec-2020

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

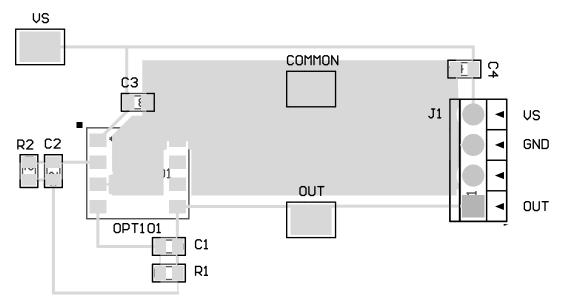

# **DTL0008A**

# PACKAGE OUTLINE

## SOP - 4.95 mm max height

PLASTIC SMALL OUTLINE

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 4. For automatic insertion, any raised irregularity on the top surface (step, mesa, etc.) shall be symmetrical about the lateral and longitudinal package centerlines.

- 5. Center of the photodiode must be within 0.25 of the center of the photodiode area.

- 6. The mold compoud for this package is clear.

# DTL0008A

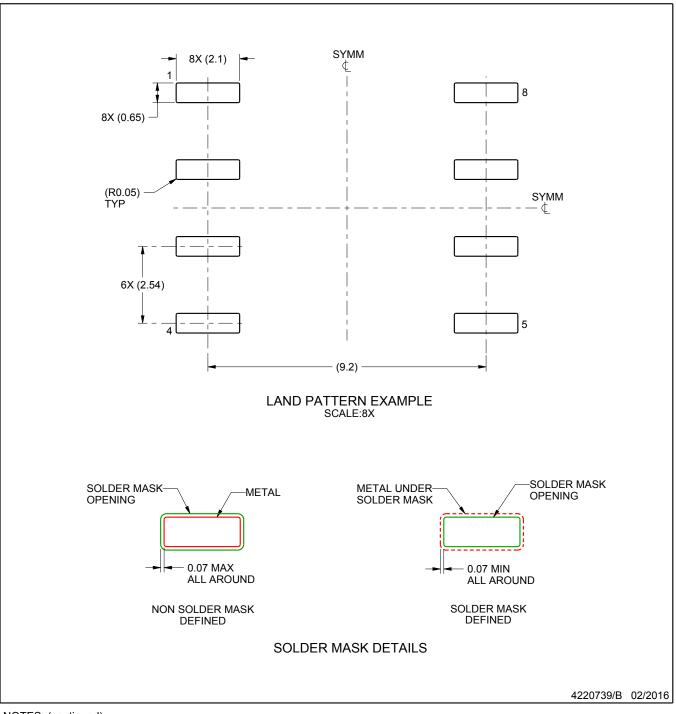

# **EXAMPLE BOARD LAYOUT**

## SOP - 4.95 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

7. Publication IPC-7351 may have alternate designs.

8. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

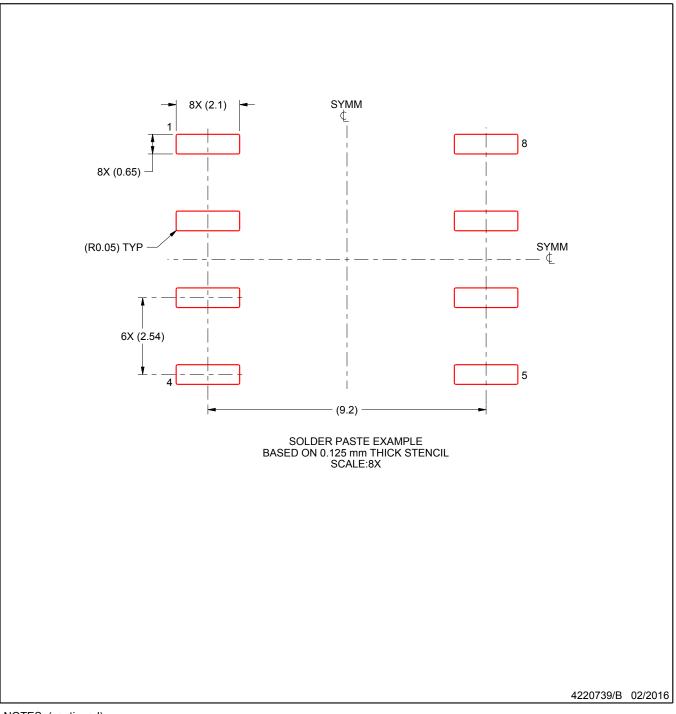

# DTL0008A

# **EXAMPLE STENCIL DESIGN**

## SOP - 4.95 mm max height

PLASTIC SMALL OUTLINE

NOTES: (continued)

- 9. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 10. Board assembly site may have different recommendations for stencil design.

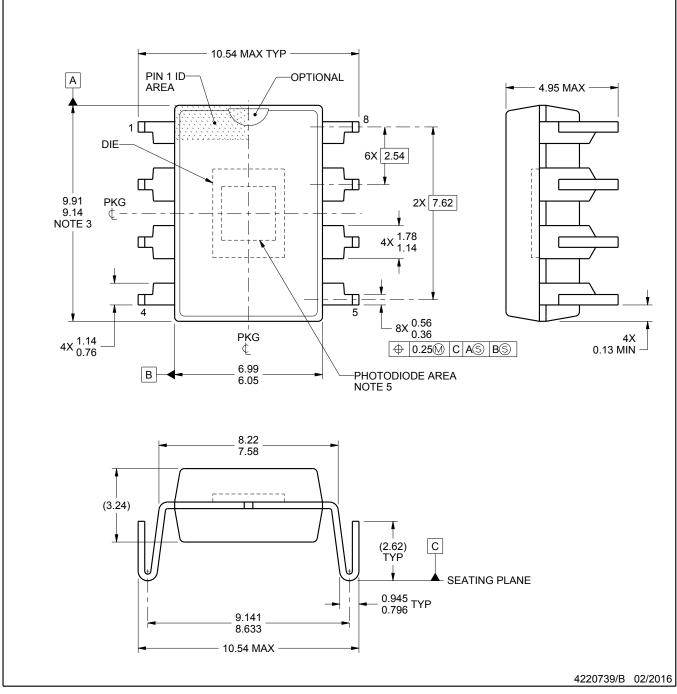

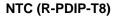

## **MECHANICAL DATA**

MPDI059 - APRIL 2001

PLASTIC DUAL-IN-LINE

- NOTES: A. All linear dimensions are in inches (millimeters). B. This drawing is subject to change without notice.

- Dimensions are measured with the package seated in JEDEC seating plane gauge GS-3.

- Dimensions do not include mold flash or protrusions.

- Mold flash or protrusions shall not exceed 0.010 (0,25). f Dimensions measured with the leads constrained to be

- perpendicular to Datum C.

- <u>/F.</u> Dimensions are measured at the lead tips with the leads unconstrained.

- G. Pointed or rounded lead tips are preferred to ease  $\bigwedge$  insertion.

- Maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 (0,25).

- I. Distance between leads including dambar protrusions to be 0.005 (0,13) minumum.

- J. A visual index feature must be located within the cross-hatched area.

- K. For automatic insertion, any raised irregularity on the top surface (step, mesa, etc.) shall be symmetrical about the lateral and longitudinal package centerlines.

- Center of photodiode must be within 0.010 (0,25) of center of photodiode area

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated