**OPA454**

SBOS391B - DECEMBER 2007 - REVISED MARCH 2016

# OPA454 High-Voltage (100-V), High-Current (50-mA) Operational Amplifiers, G = 1 Stable

#### **Features**

- Wide Power-Supply Range: ±5 V (10 V) to ±50 V (100 V)

- High-Output Load Drive: I<sub>O</sub> > ±50 mA

- Wide Output Voltage Swing: 1 V to Rails

- Independent Output Disable or Shutdown

- Wide Temperature Range: -40°C to +85°C

- 8-Pin SO Package

## **Applications**

- Test Equipment

- Avalanche Photodiode: High-V Current Sense

- Piezoelectric Cells

- Transducer Drivers

- Servo Drivers

- **Audio Amplifiers**

- High-Voltage Compliance Current Sources

- General High-Voltage Regulators and Power

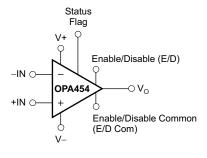

## Simplified Pin Description

## 3 Description

The OPA454 device is a low-cost operational amplifier with high voltage (100 V) and relatively high current drive (50 mA). It is unity-gain stable and has a gain-bandwidth product of 2.5 MHz.

OPA454 internally protected is overtemperature conditions and current overloads. It is fully specified to perform over a wide power-supply range of ±5 V to ±50 V or on a single supply of 10 V to 100 V. The status flag is an open-drain output that allows it to be easily referenced to standard lowvoltage logic circuitry. This high-voltage operational amplifier provides excellent accuracy, wide output swing, and is free from phase inversion problems that are often found in similar amplifiers.

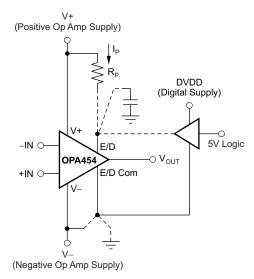

The output can be independently disabled using the Enable or Disable Pin that has its own common return pin to allow easy interface to low-voltage logic circuitry. This disable is accomplished without disturbing the input signal path, not only saving power but also protecting the load.

Featured in a small exposed metal pad package, the OPA454 is easy to heatsink over the extended industrial temperature range, -40°C to +85°C.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE          | BODY SIZE (NOM)   |

|-------------|------------------|-------------------|

| OPA454      | SO PowerPAD™ (8) | 4.89 mm × 3.90 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Table of Contents**

| 1 | Features 1                                               | 10    | Application and Implementation       | 22 |

|---|----------------------------------------------------------|-------|--------------------------------------|----|

| 2 | Applications 1                                           |       | 10.1 Applications Information        |    |

| 3 | Description 1                                            |       | 10.2 Typical Application             |    |

| 4 | Revision History2                                        |       | 10.3 System Examples                 |    |

| 5 | Device Comparison Table                                  | 11    | Power Supply Recommendations         | 33 |

| 6 | Pin Configuration and Functions                          | 12    | Layout                               |    |

| 7 | Specifications4                                          |       | 12.1 Layout Guidelines               |    |

| • | 7.1 Absolute Maximum Ratings                             |       | 12.2 Layout Example                  | 35 |

|   | 7.2 ESD Ratings                                          |       | 12.3 Thermal Protection              | 36 |

|   | 7.3 Recommended Operating Conditions                     |       | 12.4 Power Dissipation               | 36 |

|   | 7.4 Thermal Information                                  |       | 12.5 Heatsinking                     |    |

|   | 7.5 Electrical Characteristics: $V_S = \pm 50 \text{ V}$ | 13    | Device and Documentation Support     |    |

|   | 7.6 Typical Characteristics                              |       | 13.1 Device Support                  |    |

| 8 | Parameter Measurement Information                        |       | 13.2 Documentation Support           |    |

| _ |                                                          |       | 13.3 Community Resources             |    |

| 9 | Detailed Description                                     |       | 13.4 Trademarks                      |    |

|   | 9.1 Overview                                             |       | 13.5 Electrostatic Discharge Caution | 39 |

|   | 9.2 Functional Block Diagram                             |       | 13.6 Glossary                        |    |

|   | 9.3 Feature Description                                  | 14    | Mechanical, Packaging, and Orderable |    |

|   | 9.4 Device Functional Modes                              | • • • | Information                          | 39 |

|   |                                                          |       |                                      |    |

## 4 Revision History

| Changes from Revision A | (December 2008) to Revision B |

|-------------------------|-------------------------------|

|                         |                               |

**Page**

| • | Added Pin Functions table, ESD Ratings table, Recommended Operating Conditions table, Thermal Information table, Feature Description section, Device Functional Modes section, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1 |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • | Changed OPA454 Related Products table to Device Comparison table                                                                                                                                                                                                                                                                                                                    |   |

|   | Deleted Ordering Information table                                                                                                                                                                                                                                                                                                                                                  |   |

|   | Corrected symbol error in Absolute Maximum Ratings table; changed operating temperature specification from $T_J$ to $T_\Delta$                                                                                                                                                                                                                                                      |   |

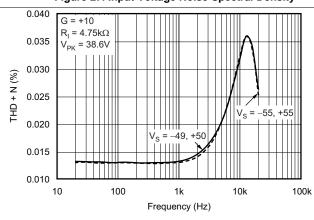

| • | Changed Figure 29 title from THD+N vs Temperature to THD+N vs Frequency                                                                                                                                                                                                                                                                                                             |   |

|   | Changed Figure 30 title from THD+N vs Temperature to THD+N vs Frequency                                                                                                                                                                                                                                                                                                             |   |

## Changes from Original (December 2007) to Revision A

Pag

| • | Deleted DDA Package from title of Figure 14                                                                           | . 9 |

|---|-----------------------------------------------------------------------------------------------------------------------|-----|

| • | Corrected mislabeled y-axis in Figure 42                                                                              | 12  |

| • | Corrected mislabeled y-axis in Figure 43                                                                              | 13  |

| • | Corrected mislabeled y-axis in Figure 44                                                                              | 13  |

|   | Changed statement about thermal shutdown cycling qualification studies from 400 hours to 1000 hours in <i>Current</i> |     |

|   | Limit section                                                                                                         | 21  |

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

## 5 Device Comparison Table

| PRODUCT               | DESCRIPTION  |  |

|-----------------------|--------------|--|

| OPA445 <sup>(1)</sup> | 80 V, 15 mA  |  |

| OPA452                | 80 V, 50 mA  |  |

| OPA547                | 60 V, 750 mA |  |

| OPA548                | 60 V, 3 A    |  |

| OPA549                | 60 V, 9 A    |  |

| OPA551                | 60 V, 200 mA |  |

| OPA567                | 5 V, 2 A     |  |

| OPA569                | 5 V, 2.4 A   |  |

(1) The OPA445 is pin-compatible with the OPA454, except in applications using the offset trim, and NC pins other than open.

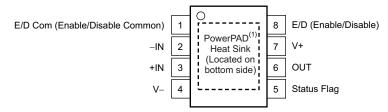

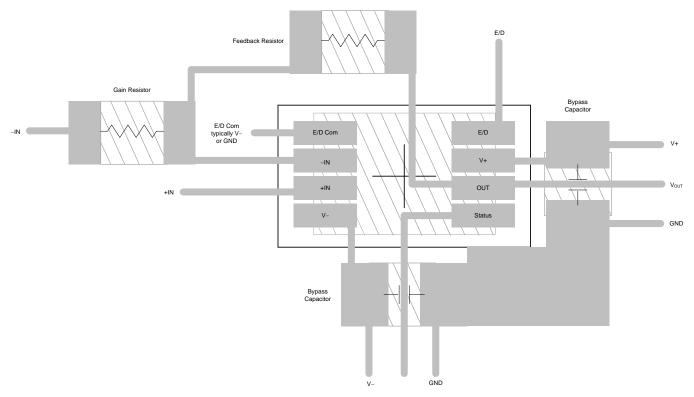

# 6 Pin Configuration and Functions

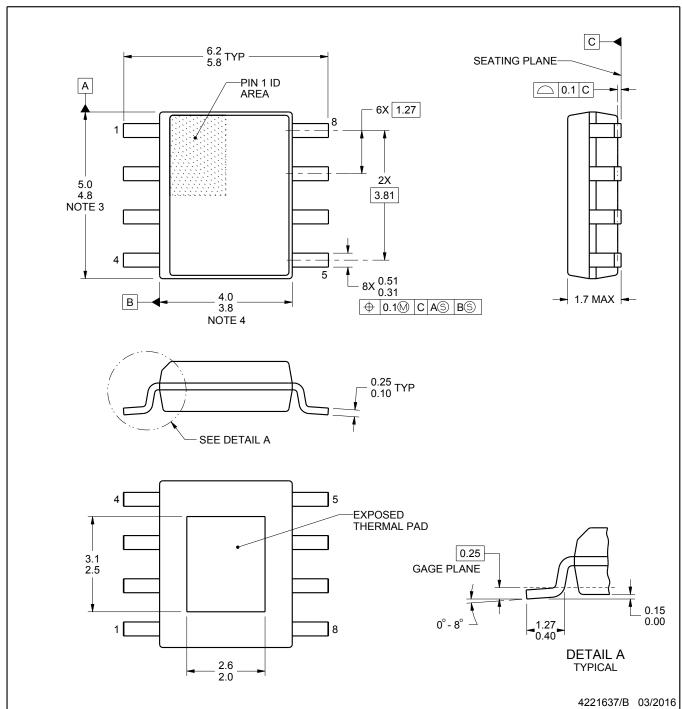

#### DDA PACKAGE 8-Pin SO PowerPAD Top View

(1) PowerPAD is internally connected to V-. Soldering the PowerPAD to the printed-circuit board (PCB) is always required, even with applications that have low power dissipation.

#### **Pin Functions**

| PIN NAME NO.         |   | 1/0               | DECORIDATION                                                                                                                                           |  |

|----------------------|---|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                      |   | 1/0               | DESCRIPTION                                                                                                                                            |  |

| E/D (Enable/Disable) | 8 | 1                 | Enable/Disable                                                                                                                                         |  |

| E/D Com              | 1 | 1                 | Enable/Disable common                                                                                                                                  |  |

| -IN                  | 2 | I Inverting input |                                                                                                                                                        |  |

| +IN                  | 3 | I                 | Noninverting input                                                                                                                                     |  |

| OUT                  | 6 | 0                 | Output                                                                                                                                                 |  |

| Status Flag          | 5 | 0                 | The Status Flag is an open-drain active-low output referenced to E/D Com. This pin goes active for either an overcurrent or overtemperature condition. |  |

| V-                   | 4 | _                 | Negative (lowest) power supply                                                                                                                         |  |

| V+ 7                 |   | _                 | Positive (highest) power supply                                                                                                                        |  |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|             |                                     | MIN         | MAX        | UNIT |

|-------------|-------------------------------------|-------------|------------|------|

|             | Supply voltage, $V_S = (V+) - (V-)$ |             | 120        | ٧    |

| Voltage     | Signal input pin <sup>(2)</sup>     | (V-) - 0.3  | (V+) + 0.3 | ٧    |

|             | E/D to E/D Com                      |             | 5.5        | ٧    |

| Comment     | Signal input pin <sup>(2)</sup>     |             | ±10        | mA   |

| Current     | Output short circuit (3)            | Continuous  |            |      |

|             | Operating, T <sub>A</sub>           | <b>-</b> 55 | 125        | °C   |

| Temperature | Junction, T <sub>J</sub>            |             | 150        | °C   |

|             | Storage, T <sub>stg</sub>           | <b>-</b> 55 | 125        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

| (===)              |                         | Machine model (MM)                                                  | ±150  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                      | MIN         | NOM MAX   | UNIT |

|--------------------------------------|-------------|-----------|------|

| Supply voltage, $V_S = (V+) - (V-)$  | 10 (±5)     | 100 (±50) | V    |

| T <sub>A</sub> Operating temperature | <b>–</b> 55 | 125       | °C   |

#### 7.4 Thermal Information

|                       |                                              | OPA454   |      |

|-----------------------|----------------------------------------------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DDA (SO) | UNIT |

|                       |                                              | 8 PINS   |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 40.6     | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 46       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 20.7     | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 5.6      | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 20.6     | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.5      | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.3 V beyond the supply rails must be current-limited to 10 mA or less.

<sup>(3)</sup> Short-circuit to ground.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.5 Electrical Characteristics: $V_s = \pm 50 \text{ V}$

At  $T_P^{(1)}$  = 25°C,  $R_L$  = 4.8 k $\Omega$  to mid-supply,  $V_{CM}$  =  $V_{OUT}$  = mid-supply, unless otherwise noted.

|                      | PA                                                                            | RAMETER                                                               | TEST CONDITIONS                                                                                          | MIN        | TYP                    | MAX        | UNIT               |

|----------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------|------------------------|------------|--------------------|

| OFFSET               | VOLTAGE                                                                       |                                                                       |                                                                                                          |            |                        |            |                    |

| Vos                  | Input offset volta                                                            | age                                                                   | I <sub>O</sub> = 0 mA                                                                                    |            | ±0.2                   | ±4         | mV                 |

| dV <sub>OS</sub> /dT | Input offset volta                                                            | age vs temperature                                                    | At $T_A = -40$ °C to +85°C                                                                               |            | ±1.6                   | ±10        | μV/°C              |

| PSRR                 | Input offset volta                                                            | age vs power supply                                                   | V <sub>S</sub> = ±4 V to ±60 V, V <sub>CM</sub> = 0 V                                                    |            | 25                     | 100        | μV/V               |

| INPUT B              | IAS CURRENT                                                                   |                                                                       |                                                                                                          |            |                        |            |                    |

|                      | 1                                                                             |                                                                       | At T <sub>P</sub> = 25°C                                                                                 |            | ±1.4                   | ±100       | pА                 |

| I <sub>B</sub>       | Input bias currer                                                             | At T <sub>A</sub> = -40°C to +85°C See <i>Typical Characteristics</i> |                                                                                                          | cs         |                        |            |                    |

| Ios                  | Input offset curre                                                            | ent                                                                   |                                                                                                          |            | ±0.2                   | ±100       | pA                 |

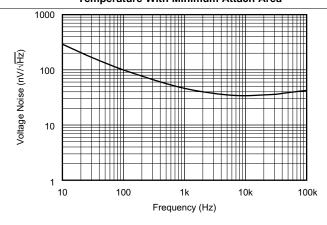

| NOISE                |                                                                               |                                                                       |                                                                                                          |            |                        |            |                    |

|                      | l                                                                             |                                                                       | f = 10 Hz                                                                                                |            | 300                    |            | nV/√ <del>Hz</del> |

| e <sub>n</sub>       | Input voltage no                                                              | ise density                                                           | f = 10 kHz                                                                                               |            | 35                     |            | nV/√Hz             |

|                      | Input voltage no                                                              | ise                                                                   | f = 0.01 Hz to 10 Hz                                                                                     |            | 15                     |            | $\mu V_{PP}$       |

| i <sub>n</sub>       | Current noise de                                                              | ensity                                                                | f = 1 kHz                                                                                                |            | 40                     |            | fA/√Hz             |

| INPUT V              | OLTAGE RANGE                                                                  |                                                                       |                                                                                                          |            |                        |            |                    |

| V <sub>CM</sub>      | Common-mode                                                                   | voltage range                                                         | Linear operation                                                                                         | (V-) + 2.5 | See Note (2)           | (V+) - 2.5 | V                  |

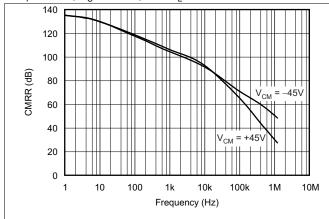

|                      | Common-mode rejection                                                         |                                                                       | $V_S = \pm 50 \text{ V}, -25 \text{ V} \le V_{CM} \le 25 \text{ V}$                                      | 100        | 146                    |            | dB                 |

|                      |                                                                               |                                                                       | V <sub>S</sub> = ±50 V, −45 V ≤ V <sub>CM</sub> ≤ 45 V                                                   | 100        | 147                    |            | dB                 |

| CMRR                 |                                                                               |                                                                       | At $T_A = -40^{\circ}\text{C}$ to +85°C,<br>$V_S = \pm 50 \text{ V}$ , -25 V ≤ $V_{CM} \le 25 \text{ V}$ | 80         | 88                     |            | dB                 |

|                      |                                                                               |                                                                       | At $T_A = -40$ °C to +85°C,<br>$V_S = \pm 50 \text{ V}$ , -45 V ≤ $V_{CM} \le 45 \text{ V}$              | 72         | 82                     |            | dB                 |

| INPUT IN             | //PEDANCE                                                                     |                                                                       |                                                                                                          |            |                        |            |                    |

|                      | Differential                                                                  |                                                                       |                                                                                                          |            | 10 <sup>13</sup>    10 |            | Ω    pF            |

|                      | Common-mode                                                                   |                                                                       |                                                                                                          |            | 10 <sup>13</sup>    9  |            | Ω    pF            |

| OPEN-LO              | OOP GAIN                                                                      |                                                                       |                                                                                                          |            |                        |            |                    |

|                      |                                                                               | (V–) + 1 V < V <sub>O</sub> < (V+) – 1 V,                             |                                                                                                          | 100        | 130                    |            | dB                 |

|                      |                                                                               | $R_L = 49 \text{ k}\Omega, I_O = \pm 1 \text{ mA}$                    | At $T_A = -40$ °C to +85°C                                                                               |            | 112                    |            | dB                 |

|                      | Open-loop                                                                     | $(V-) + 1 V < V_O < (V+) - 2 V,$                                      | 7                                                                                                        | 100        | 115                    |            | dB                 |

| A <sub>OL</sub>      | voltage gain (3)                                                              | $R_L = 4.8 \text{ k}\Omega, I_O = \pm 10 \text{ mA}$                  | At $T_A = -40^{\circ}\text{C}$ to +85°C                                                                  |            | 106                    |            | dB                 |

|                      |                                                                               | (V–) + 2 V < V <sub>O</sub> < (V+) – 3 V,                             |                                                                                                          | 80         | 102                    |            | dB                 |

|                      | $(V-) + 2 V < V_O < (V+) - 3$<br>$R_L = 1880 \Omega, I_O = \pm 25 \text{ mA}$ | $R_L = 1880 \Omega, I_O = \pm 25 \text{ mA}$                          | At $T_A = -40$ °C to +85°C                                                                               |            | 84                     |            | dB                 |

| FREQUE               | NCY RESPONSE                                                                  | (4)                                                                   |                                                                                                          |            |                        |            | <del></del>        |

| GBW                  | Gain-bandwidth                                                                |                                                                       | Small-signal                                                                                             |            | 2.5                    |            | MHz                |

|                      |                                                                               |                                                                       | $G = \pm 1, V_O = 80-V \text{ step},$                                                                    |            |                        |            |                    |

| SR                   | Slew rate                                                                     |                                                                       | $R_L = 3.27 \text{ k}\Omega$                                                                             |            | 13                     |            | V/µs               |

|                      | Full-power band                                                               | width <sup>(5)</sup>                                                  |                                                                                                          |            | 35                     |            | kHz                |

|                      |                                                                               |                                                                       | To $\pm 0.1\%$ , G = $\pm 1$ , V <sub>O</sub> = 20-V step                                                |            | 3                      |            | μs                 |

| t <sub>S</sub>       | Settling time <sup>(6)</sup>                                                  |                                                                       | To $\pm 0.01\%$ , G = $\pm 5$ or $\pm 10$ ,<br>V <sub>O</sub> = 80-V step                                |            | 10                     |            | μs                 |

| THD+N                | Total harmonic                                                                | distortion + noise <sup>(7)</sup>                                     | $V_S = +40.6 \text{ V/}-39.6 \text{ V}, G = \pm 1,$<br>f = 1 kHz, $V_O = 77.2 \text{ V}_{PP}$            |            | 0.0008%                |            |                    |

<sup>(1)</sup>  $T_P$  is the temperature of the leadframe die pad (exposed thermal pad) of the PowerPAD package. (2) Typical range is (V-) + 1.5 V to (V+) - 1.5 V.

Measured using low-frequency (<10 Hz) ±49-V square wave. See typical characteristic curve, *Current Limit vs Temperature* (Figure 23). See *Typical Characteristics* curves.

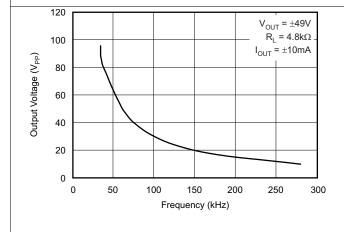

See typical characteristic curve, *Maximum Output Voltage vs Frequency* (Figure 11).

See the *Feature Description* section, *Settling Time*.

Supplies reduced to allow closer swing to rails due to test equipment limitations. See typical characteristic curves *Total Harmonic* Distortion + Noise vs Frequency (Figure 29 and Figure 30) for additional power levels.

# Electrical Characteristics: $V_S = \pm 50 \text{ V}$ (continued)

At  $T_P^{(1)} = 25^{\circ}C$ ,  $R_L = 4.8 \text{ k}\Omega$  to mid-supply,  $V_{CM} = V_{OUT} = \text{mid-supply}$ , unless otherwise noted.

|                 | PA                                                        | RAMETER                                                              | TEST CONDITIONS                                                                  | MIN           | TYP          | MAX          | UNIT |

|-----------------|-----------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------|--------------|--------------|------|

| OUTPU           | Т                                                         |                                                                      |                                                                                  |               |              |              |      |

|                 | Voltage output swing from rail <sup>(8)</sup>             |                                                                      | $R_L = 49 \text{ k}\Omega, A_{OL} \ge 100 \text{ dB},$<br>$I_O = 1 \text{ mA}$   | (V–) + 1      |              | (V+) - 1     | V    |

| Vo              |                                                           |                                                                      | $R_L = 4.8 \text{ k}\Omega, A_{OL} \ge 100 \text{ dB},$<br>$I_O = 10 \text{ mA}$ | (V–) + 1      |              | (V+) - 2     | V    |

|                 |                                                           |                                                                      | $R_L = 1880 \ \Omega, \ A_{OL} \ge 80 \ dB,$<br>$I_O = 26 \ mA$                  | (V-) + 2      |              | (V+) - 3     | V    |

|                 | Continuous curre                                          | inuous current output, DC Depends on circuit conditions See Figure 5 |                                                                                  |               |              |              |      |

|                 | Maximum peak current output, current limit <sup>(3)</sup> |                                                                      |                                                                                  |               | +120/–150    |              | mA   |

| l <sub>o</sub>  |                                                           |                                                                      | At $T_A = -40$ °C to +85°C                                                       |               | +140/–170    |              | mA   |

| $C_{LOAD}$      | Capacitive load                                           | drive <sup>(4)</sup>                                                 |                                                                                  |               | 200          |              | pF   |

| $R_{O}$         | Open-loop output impedance                                |                                                                      |                                                                                  |               | See Figure 4 |              | Ω    |

|                 | Output                                                    | Output capacitance                                                   |                                                                                  |               | 18           |              | pF   |

|                 | disabled                                                  | Feedthrough capacitance (9)                                          |                                                                                  |               | 150          |              | fF   |

| STATUS          | S FLAG PIN (Refer                                         | enced to E/D Com)                                                    |                                                                                  |               |              |              |      |

|                 | Status Flag delay                                         |                                                                      | Enable → Disable                                                                 |               | 6            |              | μs   |

|                 |                                                           |                                                                      | Disable → Enable                                                                 |               | 4            |              | μs   |

|                 |                                                           |                                                                      | Overcurrent delay <sup>(10)</sup>                                                |               | 15           |              | μs   |

|                 |                                                           |                                                                      | Overcurrent recovery delay <sup>(10)</sup>                                       |               | 10           |              | μs   |

| TJ              | Junction<br>temperature                                   | Alarm (Status Flag high)                                             |                                                                                  |               | 150          |              | °C   |

|                 |                                                           | Return to normal operation (Status Flag low)                         |                                                                                  |               | 130          |              | °C   |

|                 |                                                           |                                                                      | Normal operation                                                                 |               |              | E/D Com + 2  | V    |

|                 | Output voltage <sup>(4)</sup>                             |                                                                      | $R_L = 100 \Omega$ during thermal overdrive, alarm                               | (V+) - 2.5    |              |              | V    |

| E/D (EN         | ABLE/DISABLE) P                                           | PIN                                                                  |                                                                                  |               |              |              |      |

|                 | E/D pin, referen                                          | ced to E/D Com pin <sup>(11)(12)</sup>                               |                                                                                  |               |              |              |      |

| V <sub>SD</sub> | High (output enabled)                                     |                                                                      | Pin open or forced high                                                          | E/D Com + 2.5 |              | E/D Com + 5  | V    |

|                 | Low (output disabled)                                     |                                                                      | Pin forced low                                                                   | E/D Com       | E/           | D Com + 0.65 | V    |

|                 | Output disable ti                                         | me                                                                   |                                                                                  |               | 4            |              | μs   |

|                 | Output enable ti                                          | me                                                                   |                                                                                  |               | 3            |              | μs   |

| E/D CO          | M PIN                                                     |                                                                      |                                                                                  |               |              |              |      |

|                 | Voltage range                                             |                                                                      |                                                                                  | (V-)          |              | (V+) - 5     | V    |

| POWER           | SUPPLY                                                    |                                                                      |                                                                                  |               |              |              |      |

| Vs              | Specified range                                           |                                                                      |                                                                                  |               | ±50          |              | V    |

|                 | Operating voltage range                                   |                                                                      |                                                                                  | ±5            |              | ±50          | V    |

| IQ              | Quiescent current                                         |                                                                      | $I_O = 0 \text{ mA}$                                                             |               | 3.2          | 4            | mA   |

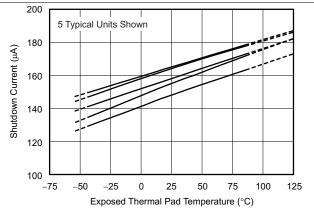

|                 | Quiescent current in Shutdown mode                        |                                                                      | $I_{O} = 0$ mA, $V_{E/D} = 0.65$ V                                               |               | 150          | 210          | μA   |

| TEMPE           | RATURE RANGE                                              |                                                                      |                                                                                  |               |              |              |      |

| T <sub>A</sub>  | Specified range                                           |                                                                      |                                                                                  | -40           |              | 85           | °C   |

|                 | Operating range                                           |                                                                      |                                                                                  | -55           |              | 125          | °C   |

<sup>(8)</sup> See typical characteristic curve, *Output Voltage Swing vs Output Current* (Figure 10). (9) Measured using Figure 56.

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

<sup>(10)</sup> See *Typical Characteristics* curves for current limit behavior.

(11) See typical characteristic curve, *I<sub>ENABLE</sub>* vs *V<sub>ENABLE</sub>* (Figure 45).

(12) High enables the outputs.

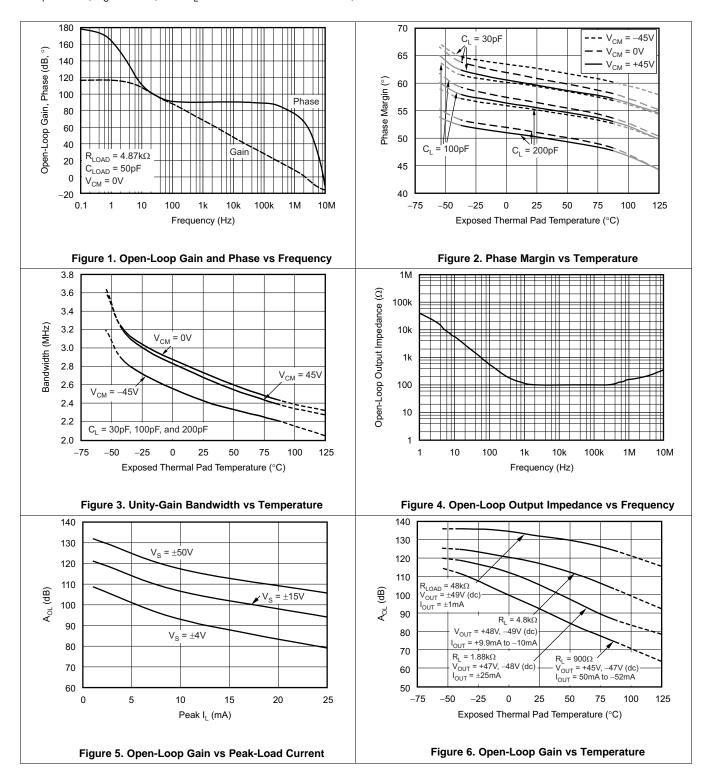

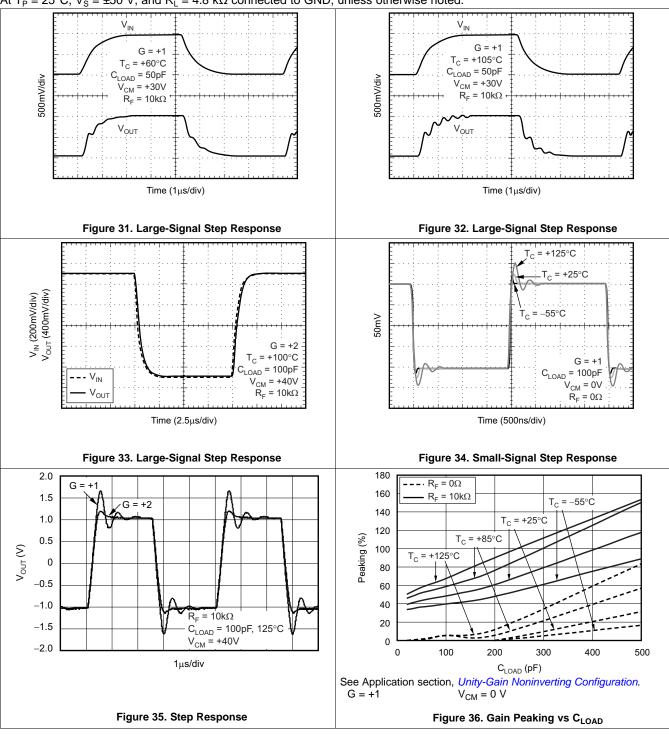

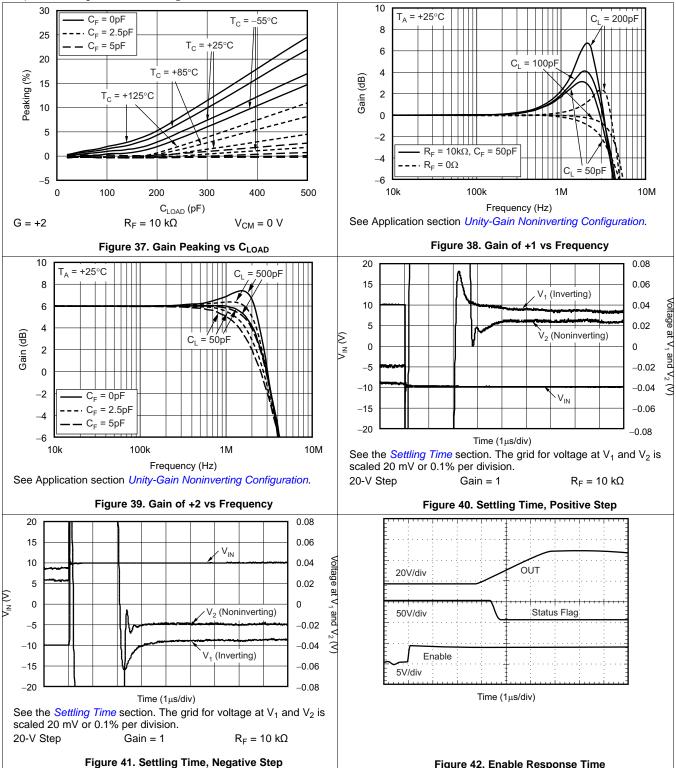

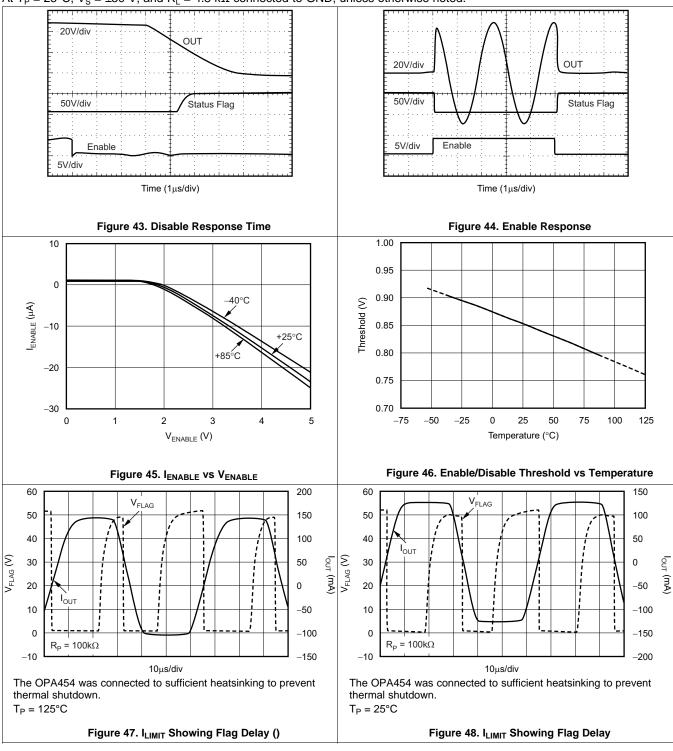

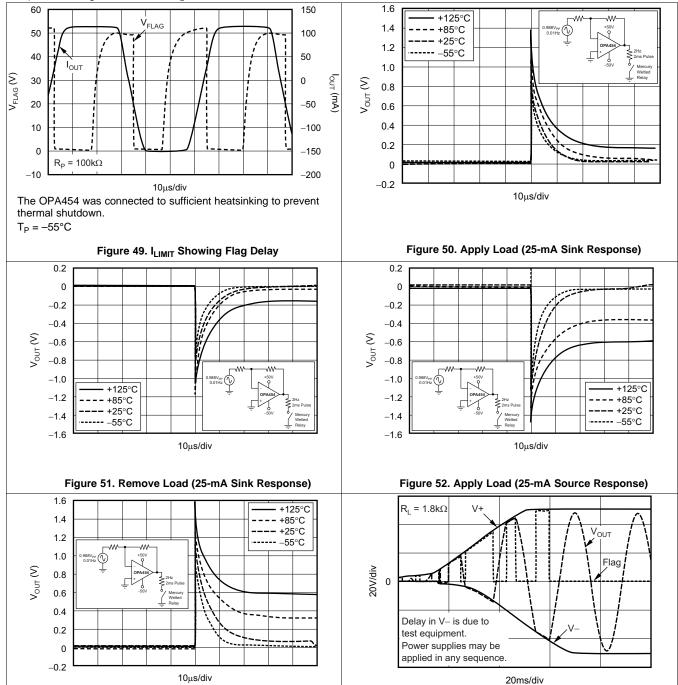

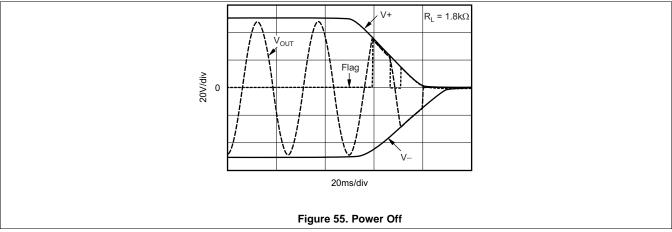

#### 7.6 Typical Characteristics

At  $T_P$  = 25°C,  $V_S$  = ±50 V, and  $R_L$  = 4.8 k $\Omega$  connected to GND, unless otherwise noted.

Copyright © 2007–2016, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

At  $T_P$  = 25°C,  $V_S$  = ±50 V, and  $R_L$  = 4.8 k $\Omega$  connected to GND, unless otherwise noted.

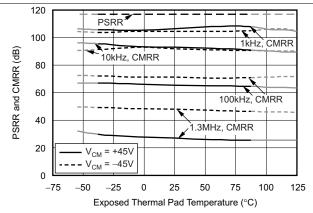

Figure 7. Common-Mode Rejection Ratio vs Frequency

Figure 8. Power-Supply and Common-Mode Rejection Ratio vs Temperature

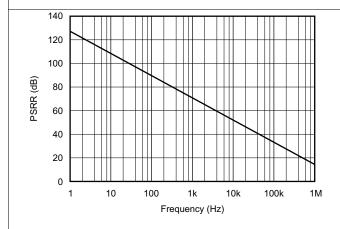

Figure 9. Power-Supply Rejection Ratio vs Frequency

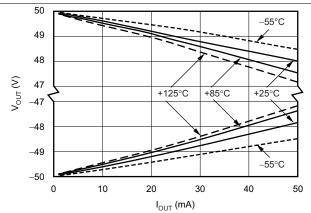

Figure 10. Output Voltage Swing vs Output Current (Measured When Status Flag Transitions From Low To High)

Figure 11. Maximum Output Voltage vs Frequency

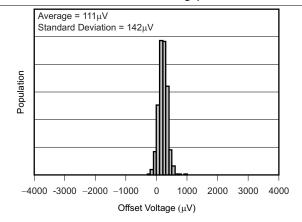

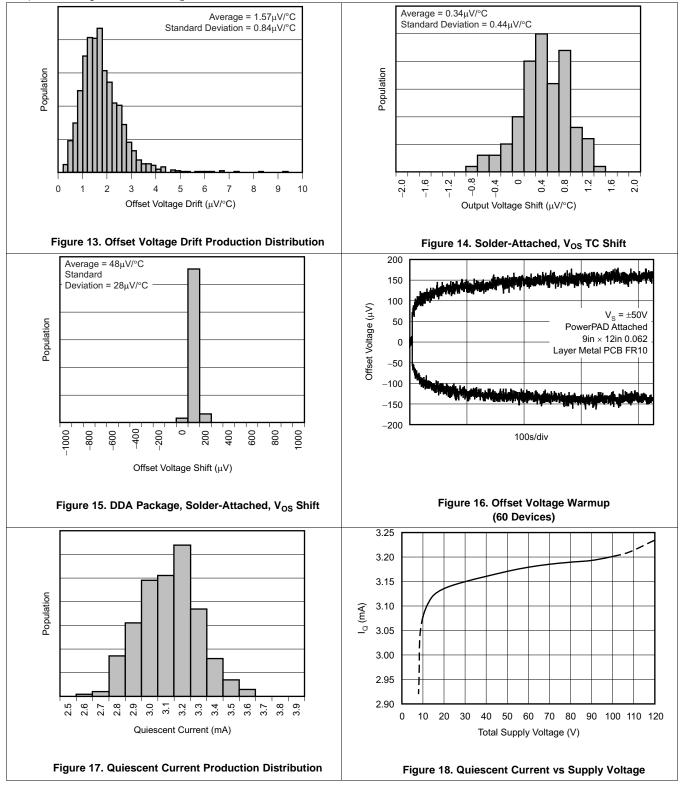

Figure 12. DDA Package Offset Voltage Production Distribution

At  $T_P = 25$ °C,  $V_S = \pm 50$  V, and  $R_L = 4.8$  k $\Omega$  connected to GND, unless otherwise noted.

Copyright © 2007–2016, Texas Instruments Incorporated

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

At  $T_P$  = 25°C,  $V_S$  = ±50 V, and  $R_L$  = 4.8 k $\Omega$  connected to GND, unless otherwise noted.

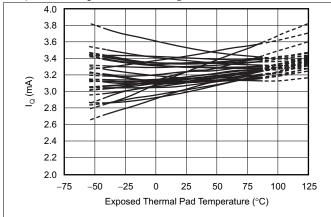

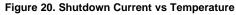

Figure 19. Quiescent Current vs Temperature

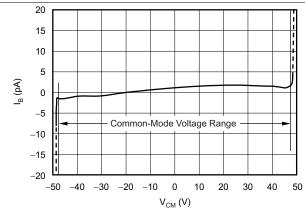

Figure 21. Input Bias Current vs Temperature

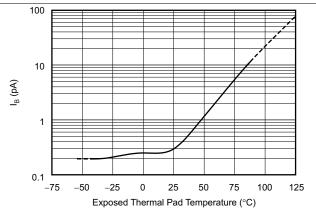

Figure 22. Input Bias Current vs Common-Mode Voltage

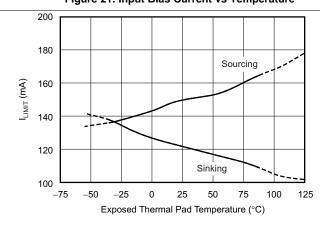

Figure 23. Current Limit vs Temperature

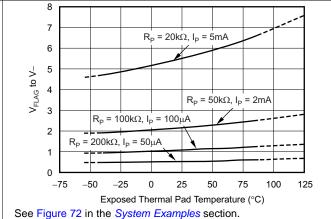

Figure 24. Status Flag Voltage vs Temperature (E/D Com Connected To V-)

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

At  $T_P$  = 25°C,  $V_S$  = ±50 V, and  $R_L$  = 4.8 k $\Omega$  connected to GND, unless otherwise noted.

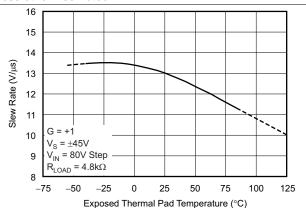

Figure 26. Slew Rate vs Temperature

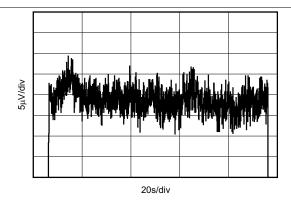

Figure 27. Input Voltage Noise Spectral Density

Figure 28. 0.01-Hz to 10-Hz Input Voltage Noise

$V_S = +41.6$

-40.6

$\dot{V}_{S} = +40.6$

-39.6

Figure 29. Total Harmonic Distortion + Noise vs Frequency

Figure 30. Total Harmonic Distortion + Noise vs Frequency

Copyright © 2007-2016, Texas Instruments Incorporated

Submit Documentation Feedback

100k

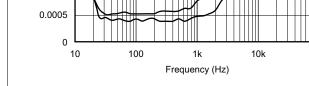

0.0030

0.0025

0.0020

0.0015

0.0010

(%) N + QHL

G = +1

$R_1 = 4.75k\Omega$

$V_{PK} = 38.6V$

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

At  $T_P$  = 25°C,  $V_S$  = ±50 V, and  $R_L$  = 4.8 k $\Omega$  connected to GND, unless otherwise noted.

At  $T_P = 25$ °C,  $V_S = \pm 50$  V, and  $R_L = 4.8$  k $\Omega$  connected to GND, unless otherwise noted.

Copyright © 2007-2016, Texas Instruments Incorporated

Submit Documentation Feedback

Figure 42. Enable Response Time

At  $T_P = 25$ °C,  $V_S = \pm 50$  V, and  $R_L = 4.8$  k $\Omega$  connected to GND, unless otherwise noted.

At  $T_P = 25$ °C,  $V_S = \pm 50$  V, and  $R_L = 4.8$  k $\Omega$  connected to GND, unless otherwise noted.

Copyright © 2007-2016, Texas Instruments Incorporated

Figure 53. Remove Load (25-mA Source Response)

Figure 54. Power On

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

At  $T_P$  = 25°C,  $V_S$  = ±50 V, and  $R_L$  = 4.8 k $\Omega$  connected to GND, unless otherwise noted.

## 8 Parameter Measurement Information

Figure 56. Feedthrough Capacitance Circuit

## 9 Detailed Description

#### 9.1 Overview

The OPA454 is a low-cost operational amplifier (op amp) with high voltage (100 V) and a relatively high current drive of 50 mA. This device is unity-gain stable and features a gain-bandwidth product of 2.5 MHz. The high-voltage OPA454 offers excellent accuracy, wide output swing, and has no phase inversion problems that are typically found in similar op amps. The device can be used in virtually any ±5-V to ±50-V op amp configuration, and is especially useful for supply voltages greater than 36 V.

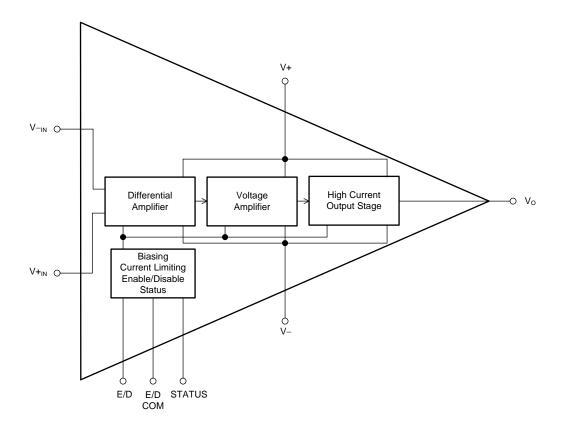

#### 9.2 Functional Block Diagram

#### 9.3 Feature Description

The OPA454 includes safety features on both the device input and output. On the input, protection is provided for a variety of fault conditions. On the output, current limiting and thermal protection are provided. Performance advantages include a ±50-mA output current capability along with the ability to swing to within 1 V of the supply rails. The Enable/Disable function provides the ability to turn off the output stage and reduce power consumption when not being used. The Status Flag indicates fault conditions and can be used in conjunction with the Enable/Disable function to implement fault control loops.

#### 9.3.1 Input Protection

The OPA454 has increased protection against damage caused by excessive voltage between op amp input pins or input pin voltages that exceed the power supplies; external series resistance is not needed for protection. Internal series JFETs limit input overload current to a non-destructive 4 mA, even with an input differential voltage as large as 120 V. Additionally, the OPA454 has dielectric isolation between devices and the substrate. Therefore, the amplifier is free from the limitations of junction isolation common to many IC fabrication processes.

#### 9.3.2 Input Range

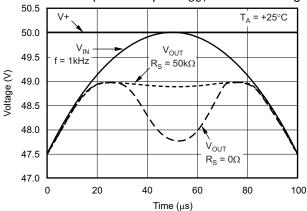

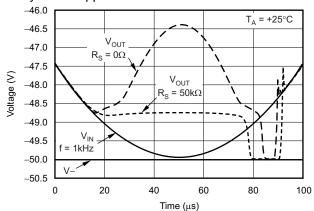

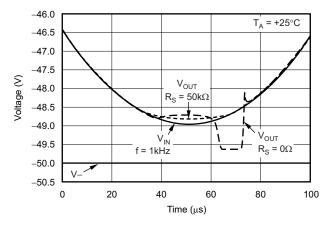

The OPA454 is specified to give linear operation with input swing to within 2.5 V of either supply. Generally, a gain of +1 is the most demanding configuration. Figure 57 and Figure 58 show output behavior as the input swings to within 0 V of the rail, using the circuit shown in Figure 60. Figure 59 shows the behavior with an input signal that swings beyond the specified input range to within 1 V of the rail, also using the circuit in Figure 60. Notice that the beginning of the phase reversal effect may be reduced by inserting series resistance ( $R_S$ ) in the connection to the positive input.  $V_{OUT}$  does not swing all the way to the opposite rail.

Figure 57. Output Voltage with Input Voltage up to V+

Figure 58. Output Voltage with Input Voltage Down to V-

Figure 59. Output Voltage with Input Voltage Down to (V-) + 1 V

Figure 60. Input Range Test Circuit

#### 9.3.3 Output Range

The OPA454 is specified to swing to within 1 V of either supply rail with a 49-k $\Omega$  load while maintaining excellent linearity. Swing to the rail decreases with increasing output current. The OPA454 can swing to within 2 V of the negative rail and 3 V of the positive rail with a 1.88-k $\dot{\Omega}$  load. The typical characteristic curve, Output Voltage Swing vs Output Current (Figure 10), shows this behavior in detail.

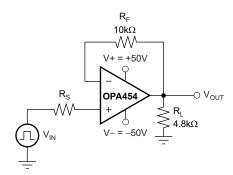

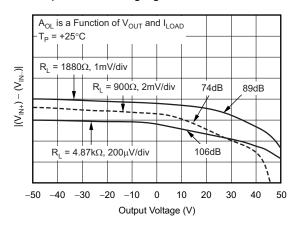

#### 9.3.4 Open-Loop Gain Linearity

Figure 61 shows the nonlinear relationship of A<sub>OL</sub> and output voltage. As Figure 61 shows, open-loop gain is lower with positive output voltage levels compared to negative voltage levels. Specifications in *Electrical* Characteristics:  $V_S = \pm 50$  V are based upon the average gain measured at both output extremes.

Figure 61. Differential Input Voltage (+IN to -IN) vs Output Voltage

Copyright © 2007-2016, Texas Instruments Incorporated

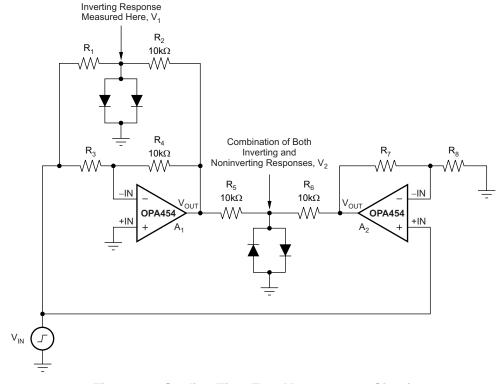

#### 9.3.5 Settling Time

The circuit in Figure 62 is used to measure the settling time response. The left half of the circuit is a standard, false-summing junction test circuit used for settling time and open-loop gain measurement.  $R_1$  and  $R_2$  provide the gain and allow for measurement without connecting a scope probe directly to the summing junction, which can disturb proper op amp function by causing oscillation.

The right half of the circuit looks at the combination of both inverting and noninverting responses.  $R_5$  and  $R_6$  remove the large step response. The remaining voltage at  $V_2$  shows the small-signal settling time that is centered on zero. This test circuit can be used for incoming inspection, real-time measurement, or in designing compensation circuits in system applications.

Table 1 lists the settling time measurement circuit configuration shown in Figure 62 with different gain settings.

Table 1. Settling Time Measurement Circuit Configuration Using Different Gain Settings for Figure 62

| COMPONENT                          | GAIN |     |     |  |  |

|------------------------------------|------|-----|-----|--|--|

| COMPONENT                          | 1    | 5   | 10  |  |  |

| $R_1(\Omega)$                      | 10 k | 2 k | 1 k |  |  |

| R <sub>3</sub> (Ω)                 | 10 k | 2 k | 1 k |  |  |

| R <sub>7</sub> (Ω)                 | 10 k | 4 k | 9 k |  |  |

| R <sub>8</sub> (Ω)                 | ∞    | 1 k | 1 k |  |  |

| V <sub>IN</sub> (V <sub>PP</sub> ) | 20   | 16  | 8   |  |  |

Figure 62. Settling Time Test Measurement Circuit

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

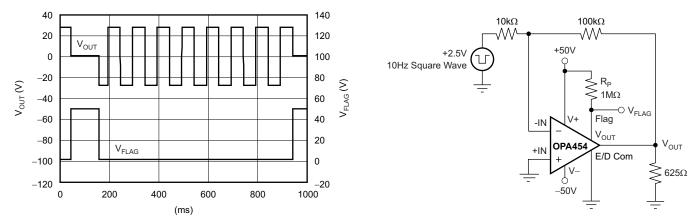

#### 9.3.6 ENABLE and E/D Com

If left disconnected, E/D Com is pulled near V– (negative supply) by an internal 10- $\mu$ A current source. When left floating, ENABLE is held approximately 2 V above E/D Com by an internal 1- $\mu$ A source. Even though active operation of the OPA454 results when the ENABLE and E/D Com pins are not connected, a moderately fast, negative-going signal capacitively coupled to the ENABLE pin can overpower the 1- $\mu$ A pullup current and cause device shutdown. This behavior can appear as an oscillation and is encountered first near extreme cold temperatures. If the enable function is not used, a conservative approach is to connect ENABLE through a 30-pF capacitor to a low impedance source. Another alternative is the connection of an external current source from V+ (positive supply) sufficient to hold the enable level above the shutdown threshold. Figure 63 shows a circuit that connects ENABLE and E/D Com. Choosing R<sub>P</sub> to be 1 M $\Omega$  with a +50-V positive power supply voltage results in  $I_P = 50~\mu$ A.

Figure 63. ENABLE and E/D Com

#### 9.3.7 Current Limit

Figure 23 and Figure 47 to Figure 49 show the current limit behavior of the OPA454. Current limiting is accomplished by internally limiting the drive to the output transistors. The output can supply the limited current continuously, unless the die temperature rises to 150°C, which initiates thermal shutdown. With adequate heatsinking, and use of the lowest possible supply voltage, the OPA454 can remain in current limit continuously without entering thermal shutdown. Although qualification studies have shown minimal parametric shifts induced by 1000 hours of thermal shutdown cycling, this mode of operation must be avoided to maximize reliability. It is always best to provide proper heatsinking (either by a physical plate or by airflow) to remain considerably below the thermal shutdown threshold. For longest operational life of the device, keep the junction temperature below 125°C.

## 9.4 Device Functional Modes

A unique mode of the OPA454 is the output disable capability. This function conserves power during idle periods (quiescent current drops to approximately 150  $\mu$ A). This disable is accomplished without disturbing the input signal path, not only saving power but also protecting the load. This feature makes disable useful for implementing external fault shutdown loops.

## 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 10.1 Applications Information

The OPA454 is a high-voltage, high-current operational amplifier capable of operating with supply voltages as high as ±50 V, or as low as ±10 V. Its design and processing allows it to be used in applications where most operational amplifiers cannot be used because of high-voltage power supply conditions, or as a result of the need for very high-output voltage swing. The output is capable of swinging within a volt, to a few volts, of the supply rails depending on the output current, which can be as much as ±50 mA. In addition, the OPA454 features input overvoltage protection, built-in output current limiting, thermal protection, and an output enable/disable function.

#### 10.1.1 Lowering Offset Voltage and Drift

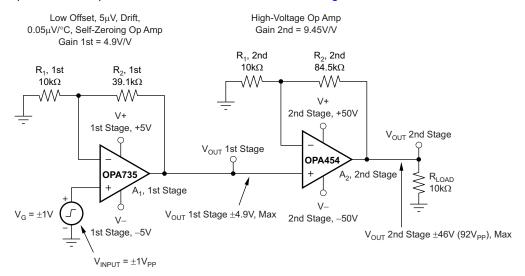

The OPA454 can be used with an OPA735 zero-drift series op amp to create a high-voltage op amp circuit that has very low input offset temperature drift. This circuit is shown in Figure 64.

Figure 64. Two-Stage, High-Voltage Op Amp Circuit with Very Low Input Offset Temperature Drift

## **Applications Information (continued)**

#### 10.1.2 Increasing Output Current

The OPA454 drives an output current of a few milliamps to greater than 50 mA while maintaining good op amp performance. See Figure 6 for open-loop gain versus temperature at various output current levels.

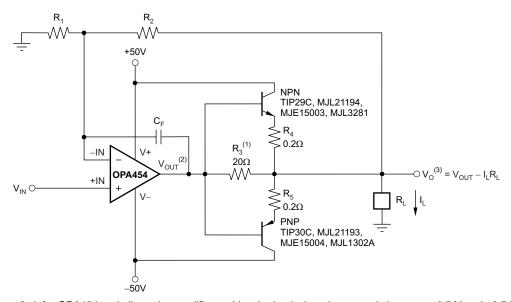

In applications where the 25-mA output current is not sufficient to drive the required load, the output current can be increased by connecting two or more OPA454s in parallel, as Figure 65 shows. Amplifier A1 is the master amplifier and may be configured in virtually any op amp circuit. Amplifier A2, the slave, is configured as a unitygain buffer. Alternatively, external output transistors can be used to boost output current. The circuit in Figure 66 is capable of supplying output currents up to 1 A, with the transistors shown.

(1) R<sub>S</sub> resistors minimize the circulating current that always flows between the two devices because of V<sub>OS</sub> errors.

Figure 65. Parallel Amplifiers Increase Output Current Capability

- (1) Provides current limit for OPA454 and allows the amplifier to drive the load when the output is between +0.7 V and -0.7 V.

- (2) Op amp  $V_{OUT}$  swings from +47 V to -48 V.

- (3)  $V_O$  swings from +44.1 V to -45.1 V at  $I_L = 1$  A.

Figure 66. External Output Transistors Boost Output Current Greater Than 1 A

## **Applications Information (continued)**

#### 10.1.3 Unity-Gain Noninverting Configuration

When in the noninverting unity-gain configuration, the OPA454 has more gain peaking with increasing positive common-mode voltage and increasing temperature. It has less gain peaking with more negative common-mode voltage. As with all op amps, gain peaking increases with increasing capacitive load. A resistor and small capacitor placed in the feedback path can reduce gain peaking and increase stability.

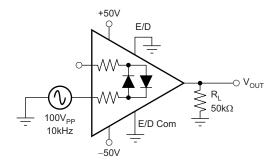

## 10.2 Typical Application

Figure 67 shows the OPA454 in a typical noninverting application with output voltage boost.

Figure 67. OPA454 Noninverting,  $A_V = 20 \text{ V/V}$ , Output Voltage Boost

#### 10.2.1 Design Requirements

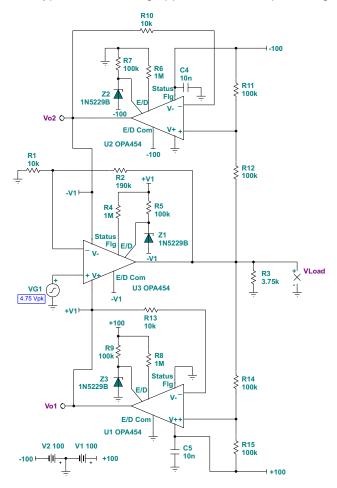

Figure 67 shows an output voltage boost circuit where three OPA454 op amps connected as shown can produce an output voltage swing as high as 195  $V_{PP}$ . The resulting output swing range is twice that attainable with a single OPA454 device operating from  $\pm 50$ -V supplies, and is useful in applications where an even higher output swing is required. A  $\pm 100$ -V<sub>DC</sub> power supply is required for this configuration.

Three of the design goals for this circuit are:

- A noninverting gain of 20 V/V (26 dB)

- A peak output voltage approaching 97.5 V, while delivering a peak output current of approximately 24 mA

- Correct biasing of the Enable/Disable (E/D), E/D Com, and Status flag pins

#### **Typical Application (continued)**

#### 10.2.2 Detailed Design Procedure

U3 (an OPA454) is the only amplifier of the three devices in the application that is responsible for signal amplification. The other two op amps, U1 and U2, provide the positive and negative supply sources (respectively) for U3. The voltage gain of U3 is that of a traditional noninverting op amp amplifier. A simple relation involving U3 feedback ( $R_2$ ) and input ( $R_1$ ) resistors sets the closed-loop gain,  $A_V$ . Equation 1 shows this calculation.

$$A_{V} = \frac{V_{OUT}}{V_{IN}} = \frac{(R_1 + R_2)}{R_1} = 1 + \left[\frac{R_2}{R_1}\right]$$

where

•  $R_1 = 10 \text{ k}\Omega$

•

$$R_2 = 190 \text{ k}\Omega$$

•  $A_V = 20 \text{ V/V}$  (1)

Applying this gain and a  $V_{PK}$  of  $\pm 97.5$  V, the maximum input voltage that may be applied without causing the output to clip is  $\pm 4.75$  V.

U1 and U2 are connected as unity-gain buffers. The purpose of this configuration is to track the U3 output voltage, and then adjust the voltage levels at the U3 V+ and V- pins so that 100 V is maintained across them. This input is accomplished by the U1 and U2 input connection to the U3 output voltage through the 100-k $\Omega$  voltage dividers formed by R<sub>11</sub>, R<sub>12</sub>, and R<sub>14</sub>, R<sub>15</sub>. For example, as the output of U3 moves more positive, the voltage on the U1 noninverting input moves up more closely to the +100-V supply level. Even though U2 provides the U1 V- supply, its output moves more positive as well. The result is that all the devices move together in unison up and down, while maintaining the 100-V difference between the V+ and V- pins for U3.

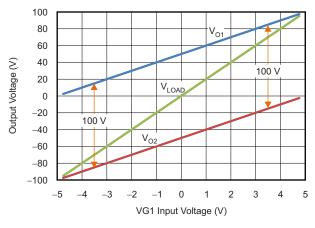

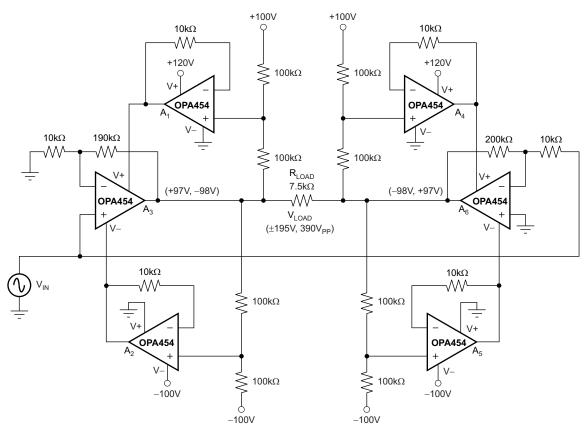

Figure 68 shows how the U3 op amp output voltage  $V_{LOAD}$  moves upward, becoming more positive, as the input voltage VG1 increases from -4.75 V to 4.75 V. Figure 68 also shows  $V_{O1}$  and  $V_{O2}$ , the U1 and U2 (respectively) output voltages. The 100-V difference between the supply pins is evident in the graph. Notice how the U3 V+ pin  $(V_{O1})$  allows 100 V greater than its V- pin  $(V_{O2})$ .

Figure 68. OPA454 Output Voltage Levels vs V<sub>S1</sub> Input Voltage

(2)

## **Typical Application (continued)**

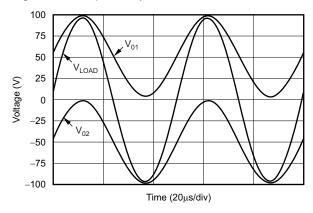

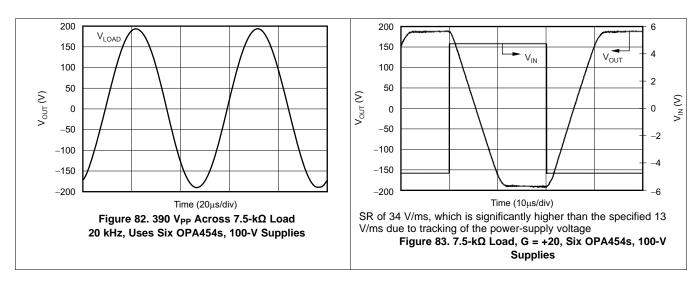

Figure 69 shows the  $V_{LOAD}$  output, a 195- $V_{PP}$ , 20-kHz sine wave, as developed across the 3.75-k $\Omega$  load resistor. The peak current provided by the OPA454 U3 output is 26 mA. U1 and U2 alternately source and sink the output current, in addition to the operating current required by U3.

Figure 69. Output Voltage Boost Develops 195- $V_{PP}$   $V_{LOAD}$  Across 3.75- $k\Omega$  Load Resistance

The output voltage booster may be used in an inverting configuration also. This use is easily accomplished by applying the input signal to the input resistor  $R_1$  as seen in Figure 70. The noninverting input is grounded and the ratio of feedback resistor  $R_2$  to  $R_1$  is set to 20:1 to satisfy the inverting gain equation given in Equation 2.

$$A_{V} = \frac{-V_{OUT}}{V_{IN}} = \frac{-R_{2}}{R_{1}}$$

where

- $R_1 = 10 \text{ k}\Omega$

- $R_2 = 200 \text{ k}\Omega$

- $A_V = -20 \text{ V/V}$

To U2 10k 200k 100k **R12** ≥ **1M** 100k **Status Z1** 1N5229B Flg E/D **VLoad** E/D Com 3.75k U3 OPA454 R14 100k +V1 To Vo1 +IN

Figure 70. OPA454 Output Boost Circuit Applied as an Inverting Amplifier

## **Typical Application (continued)**

#### 10.2.3 Application Curve

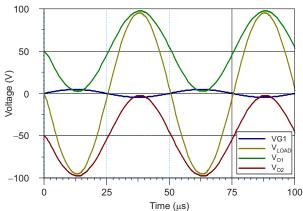

Figure 71 shows an example of the inverting output boost amplifier output waveforms obtained from a TINA-TI simulation.

Figure 71. Voltage Levels in OPA454 Inverting Boost Amplifier Circuit from TINA-TI Simulation

## 10.3 System Examples

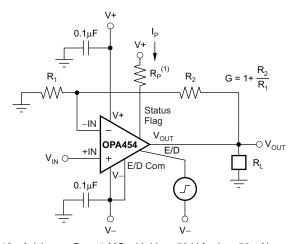

#### 10.3.1 Basic Noninverting Amplifier

Figure 72 shows the OPA454 connected as a basic noninverting amplifier. The OPA454 can be used in virtually any ±5-V to ±50-V op amp configuration. It is especially useful for supply voltages greater than 36 V.

Power-supply terminals must be bypassed with  $0.1-\mu F$  (or greater) capacitors, located near the power-supply pins. Be sure that the capacitors are appropriately rated for the power-supply voltage used.

(1) Pullup resistor with at least 10  $\mu A$  (choose  $R_P = 1~M\Omega$  with V+ = 50 V for  $I_P = 50~\mu A$ ).

Figure 72. Basic Noninverting Amplifier Configuration

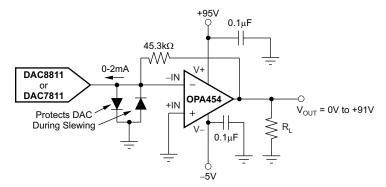

#### 10.3.2 Programmable Voltage Source

Figure 73 illustrates the OPA454 in a programmable voltage source.

Figure 73. Programmable Voltage Source

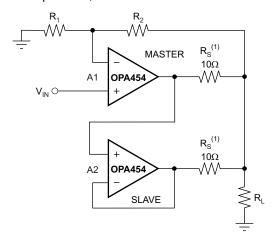

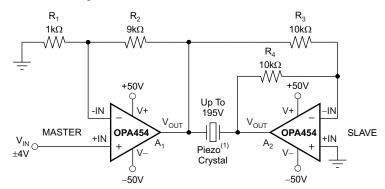

#### 10.3.3 Bridge Circuit

Figure 74 shows the OPA454 in a bridge circuit.

(1) For transducers with large capacitance, stabilization may become an issue. Be certain that the *Master* amplifier is stable before stabilizing the *Slave* amplifier.

Figure 74. Bridge Circuit Doubles Voltage for Exciting Piezo Crystals

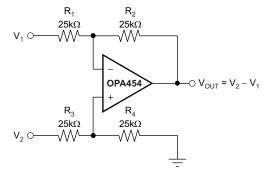

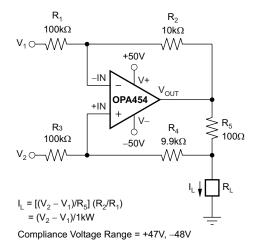

#### 10.3.4 High-Compliance Voltage Current Sources

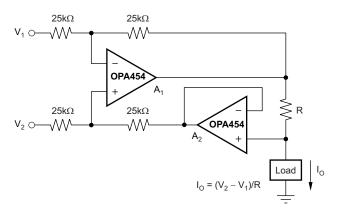

This section describes four different applications using high-compliance voltage current sources with differential inputs. Figure 75 shows a high-voltage difference amplifier circuit. Figure 76 and Figure 78 illustrate the different applications.

Figure 75. High-Voltage Difference Amplifier

Figure 76. Differential Input Voltage-to-Current Converter for Low I<sub>OUT</sub>

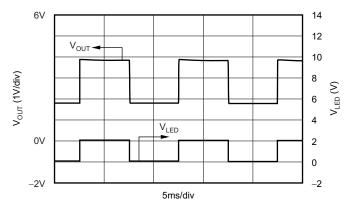

A red light emitting diode (LED) was used to generate Figure 77.

Figure 77. Avalanche Photodiode Circuit

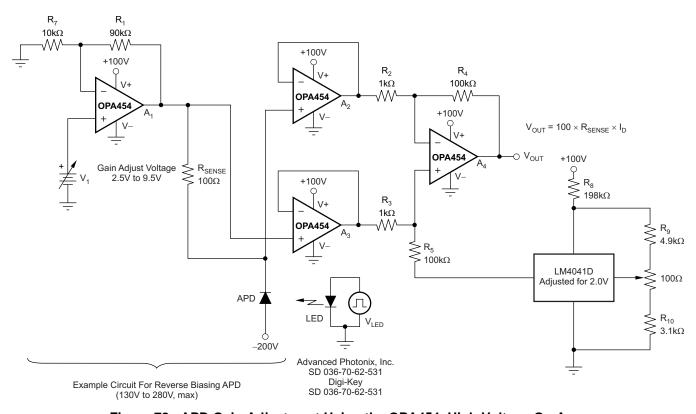

Gain of the avalanche photodiode (APD) is adjusted by changing the voltage across the APD. Gain starts to increase when reverse voltage is increased beyond 130 V for this APD diode. See Figure 78.

Copyright © 2007–2016, Texas Instruments Incorporated

Figure 78. APD Gain Adjustment Using the OPA454, High-Voltage Op Amp

#### 10.3.5 High-Voltage Instrumentation Amplifier

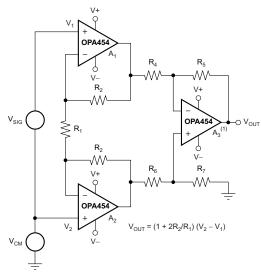

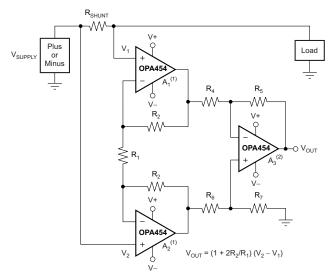

Figure 79 uses three OPA454s to create a high-voltage instrumentation amplifier.  $V_{CM} \pm V_{SIG}$  must be between (V-) + 2.5 V and (V+) - 2.5 V. The maximum supply voltage equals  $\pm 50$  V or 100 V total.

(1) The linear input range is limited by the output swing on the input amplifiers,  $A_1$  and  $A_2$ .

Figure 79. High-Voltage Instrumentation Amplifier

Figure 80 uses three OPA454s to measure current in a high-side shunt application.  $V_{SUPPLY}$  must be greater than  $V_{CM}$ .  $V_{CM}$  must be between (V-) + 2.5 V and (V+) - 2.5 V. Adhering to these restrictions keeps  $V_1$  and  $V_2$  within the voltage range required for linear operation of the OPA454. For example, if V+=50 V and V-=50 V, then  $V_1=+47.5$  V (maximum) and  $V_2=-47.5$  V (minimum). The maximum supply voltage equals  $\pm 50$  V, or 100 V total

- (1) To increase the linear input voltage range, configure A<sub>1</sub> and A<sub>2</sub> as unity-gain followers.

- (2) The linear input range is limited by the output swing on the input amplifiers,  $A_1$  and  $A_2$ .

Figure 80. High-Voltage Instrumentation Amplifier for Measuring High-Side Shunt

Figure 81 shows an example circuit that uses the OPA454 in an output voltage boost configuration with six op amp output stages.

Figure 81. Output Voltage Boost with ±195 V (390 V<sub>PP</sub>) Across Bridge-Tied Load (Six Op Amps, see Figure 82 and Figure 83)

Submit Documentation Feedback

Copyright © 2007–2016, Texas Instruments Incorporated

## 11 Power Supply Recommendations

The OPA454 may be operated from power supplies up to ±50 V or a total of 100 V with excellent performance. Most behavior remains unchanged throughout the full operating voltage range. Parameters that vary significantly with operating voltage are shown in *Typical Characteristics*.

Some applications do not require equal positive and negative output voltage swing. Power-supply voltages do not need to be equal. The OPA454 can operate with as little as 10 V between the supplies and with up to 100 V between the supplies. For example, the positive supply could be set to 90 V with the negative supply at –10 V, or vice-versa (as long as the total is less than or equal to 100 V).

## 12 Layout

## 12.1 Layout Guidelines

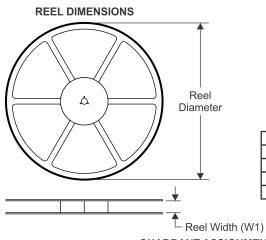

### 12.1.1 Thermally-Enhanced PowerPAD Package

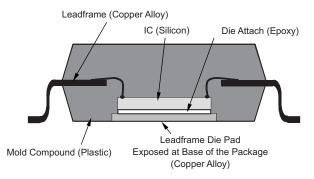

The OPA454 comes in an 8-pin SO with PowerPAD version that provides an extremely low thermal resistance  $(\theta_{JC})$  path between the die and the exterior of the package. This package features an exposed thermal pad. This thermal pad has direct thermal contact with the die; thus, excellent thermal performance is achieved by providing a good thermal path away from the thermal pad.

The OPA454 SO-8 PowerPAD is a standard-size SO-8 package constructed using a downset leadframe upon which the die is mounted, as Figure 84 shows. This arrangement results in the lead frame being exposed as a thermal pad on the underside of the package. The thermal pad on the bottom of the IC can then be soldered directly to the PCB, using the PCB as a heatsink. In addition, plated-through holes (vias) provide a low thermal resistance heat flow path to the back side of the PCB. This architecture enhances the OPA454 power dissipation capability significantly, eliminates the use of bulky heatsinks and slugs traditionally used in thermal packages, and allows the OPA454 to be easily mounted using standard PCB assembly techniques.

#### **NOTE**

Because the SO-8 PowerPAD is pin-compatible with standard SO-8 packages, the OPA454 is a drop-in replacement for operational amplifiers in existing sockets. Soldering the PowerPAD to the PCB is always required, even with applications that have low power dissipation. Soldering the device to the PCB provides the necessary thermal and mechanical connection between the leadframe die pad and the PCB.

Figure 84. Cross-Section View of a PowerPAD Package

#### **Layout Guidelines (continued)**

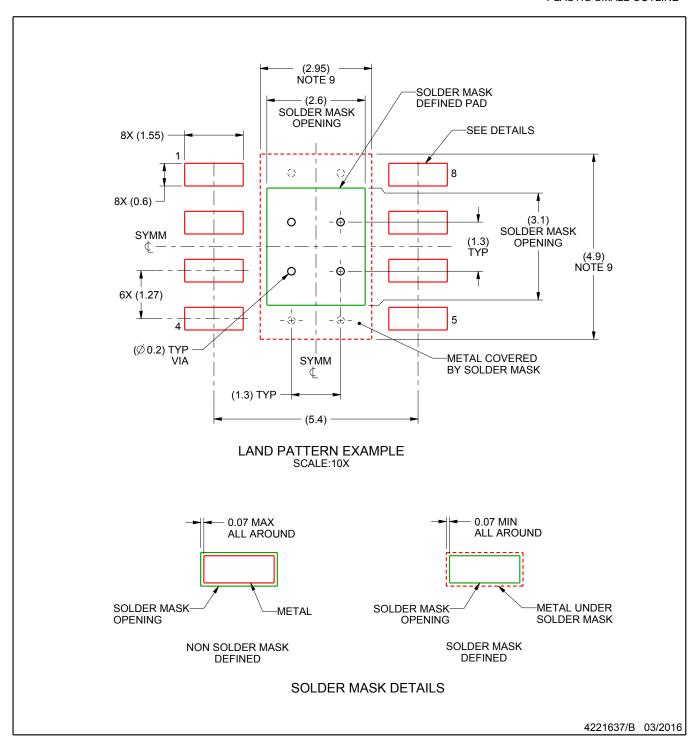

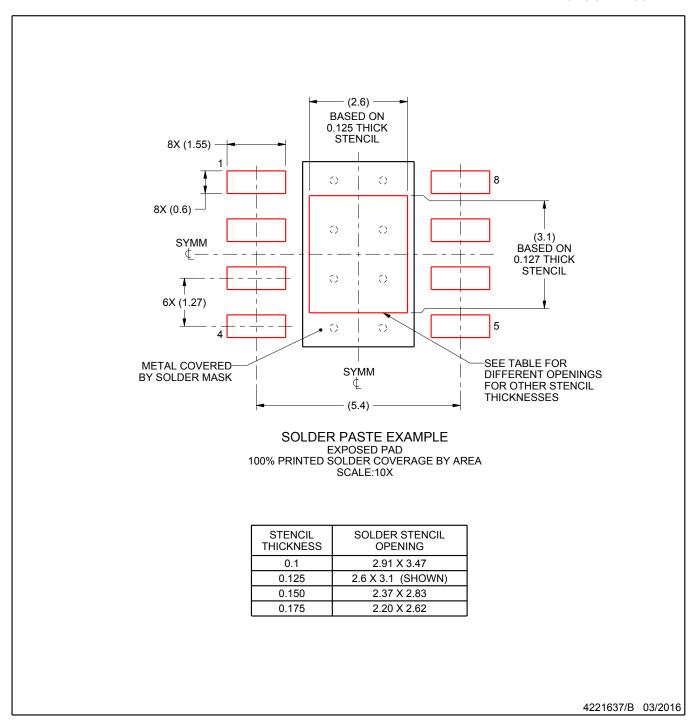

#### 12.1.2 PowerPAD Layout Guidelines

The PowerPAD package allows for both assembly and thermal management in one manufacturing operation. During the surface-mount solder operation (when the leads are being soldered), the thermal pad must be soldered to a copper area underneath the package. Through the use of thermal paths within this copper area, heat can be conducted away from the package into either a ground plane or other heat-dissipating device. Soldering the PowerPAD to the PCB is always required, even with applications that have low power dissipation. Follow these steps to attach the device to the PCB:

- 1. The PowerPAD must be connected to the most negative supply voltage on the device, V-.

- 2. Prepare the PCB with a top-side etch pattern. There must be etching for the leads as well as etch for the thermal pad.

- 3. Use of thermal vias improves heat dissipation, but are not required. The thermal pad can connect to the PCB using an area equal to the pad size with no vias, but externally connected to V–.

- 4. Place recommended holes in the area of the thermal pad. Recommended thermal land size and thermal via patterns for the SO-8 DDA package are shown in the thermal land pattern mechanical drawing appended at the end of this document. These holes must be 13 mils (.013 in, or 0.3302 mm) in diameter. Keep them small, so that solder wicking through the holes is not a problem during reflow. The minimum recommended number of holes for the SO-8 PowerPAD package is five.

- 5. Additional vias may be placed anywhere along the thermal plane outside of the thermal pad area. These vias help dissipate the heat generated by the OPA454 IC. These additional vias may be larger than the 13-mil diameter vias directly under the thermal pad. They can be larger because they are not in the thermal pad area to be soldered; thus, wicking is not a problem.

- 6. Connect all holes to the internal power plane of the correct voltage potential (V–).

- 7. When connecting these holes to the plane, do not use the typical web or spoke via connection methodology. Web connections have a high thermal resistance connection that is useful for slowing the heat transfer during soldering operations, making the soldering of vias that have plane connections easier. In this application, however, low thermal resistance is desired for the most efficient heat transfer. Therefore, the holes under the OPA454 PowerPAD package must make the connections to the internal plane with a complete connection around the entire circumference of the plated-through hole.

- 8. The top-side solder mask must leave the terminals of the package and the thermal pad area exposed. The bottom-side solder mask must cover the holes of the thermal pad area. This masking prevents solder from being pulled away from the thermal pad area during the reflow process.

- 9. Apply solder paste to the exposed thermal pad area and all of the IC terminals.

- 10. With these preparatory steps in place, the PowerPAD IC is simply placed in position and run through the solder reflow operation as any standard surface-mount component. This preparation results in a properly installed part.

For detailed information on the PowerPAD package, including thermal modeling considerations and repair procedures, see technical brief SLMA002 PowerPAD Thermally-Enhanced Package, available for download at www.ti.com.

## 12.2 Layout Example

Figure 85. OPA454 Layout Example

#### 12.3 Thermal Protection

Figure 86 shows the thermal shutdown behavior of a socketed OPA454 that internally dissipates 1 W. Unsoldered and in a socket,  $\theta_{JA}$  of the DDA package is typically 128°C/W. With the socket at 25°C, the output stage temperature rises to the shutdown temperature of 150°C, which triggers automatic thermal shutdown of the device. The device remains in thermal shutdown (output is in a high-impedance state) until it cools to 130°C where it again is powered. This thermal protection hysteresis feature typically prevents the amplifier from leaving the safe operating area, even with a direct short from the output to ground or either supply. The rail-to-rail supply voltage at which catastrophic breakdown occurs is typically 135 V at 25°C. However, the absolute maximum specification is 120 V, and the OPA454 must not be allowed to exceed 120 V under any condition. Failure as a result of breakdown, caused by spiking currents into inductive loads (particularly with elevated supply voltage), is not prevented by the thermal protection architecture.

Figure 86. Thermal Shutdown

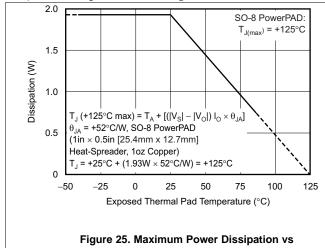

## 12.4 Power Dissipation

Power dissipation depends on power supply, signal, and load conditions. For DC signals, power dissipation is equal to the product of the output current times the voltage across the conducting output transistor,  $P_D = I_L (V_S - V_O)$ . Power dissipation can be minimized by using the lowest possible power-supply voltage necessary to assure the required output voltage swing.

For resistive loads, the maximum power dissipation occurs at a DC output voltage of one-half the power-supply voltage. Dissipation with AC signals is lower because the root-mean square (RMS) value determines heating. Application bulletin SBOA022 explains how to calculate or measure dissipation with unusual loads or signals. For constant current source circuits, maximum power dissipation occurs at the minimum output voltage, as Figure 87 shows.

The OPA454 can supply output currents of 25 mA and larger. Supplying this amount of current presents no problem for some op amps operating from ±15-V supplies. However, with high supply voltages, internal power dissipation of the op amp can be quite high. Operation from a single power supply (or unbalanced power supplies) can produce even greater power dissipation because a large voltage is impressed across the conducting output transistor. Applications with high power dissipation may require a heatsink or a heat spreader.

### **Power Dissipation (continued)**

NOTE:  $R_1 = R_3$  and  $R_2 = R_4 + R_5$ .

Figure 87. Precision Voltage-to-Current Converter With Differential Inputs

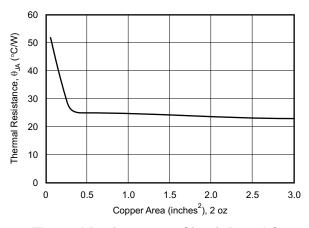

## 12.5 Heatsinking

Power dissipated in the OPA454 causes the junction temperature to rise. For reliable operation, junction temperature must be limited to 125°C, maximum. Maintaining a lower junction temperature always results in higher reliability. Some applications require a heatsink to assure that the maximum operating junction temperature is not exceeded. Junction temperature can be determined according to Equation 3:

$$T_{J} = T_{A} + P_{D}\theta_{JA}$$

(3)

Package thermal resistance,  $\theta_{JA}$ , is affected by mounting techniques and environments. Poor air circulation and use of sockets can significantly increase thermal resistance to the ambient environment. Many op amps placed closely together also increase the surrounding temperature. Best thermal performance is achieved by soldering the op amp onto a circuit board with wide printed circuit traces to allow greater conduction through the op amp leads. Increasing circuit board copper area to approximately 0.5 in<sup>2</sup> decreases thermal resistance; however, minimal improvement occurs beyond 0.5 in<sup>2</sup>, as shown in Figure 88.

For additional information on determining heatsink requirements, consult Application Bulletin SBOA021 (available for download at www.ti.com).

Figure 88. Thermal Resistance vs Circuit Board Copper Area

Product Folder Links: OPA454

ents Incorporated Submit Documentation Feedback

# 13 Device and Documentation Support

## 13.1 Device Support

#### 13.1.1 Development Support

### 13.1.1.1 TINA-TI™ (Free Software Download)

TINA™ is a simple, powerful, and easy-to-use circuit simulation program based on a SPICE engine. TINA-TI™ is a free, fully-functional version of the TINA software, preloaded with a library of macro models in addition to a range of both passive and active models. TINA-TI provides all the conventional dc, transient, and frequency domain analysis of SPICE, as well as additional design capabilities.

Available as a free download from the Analog eLab Design Center, TINA-TI offers extensive post-processing capability that allows users to format results in a variety of ways. Virtual instruments offer the ability to select input waveforms and probe circuit nodes, voltages, and waveforms, creating a dynamic guick-start tool.

#### NOTE

These files require that either the TINA software (from DesignSoft™) or TINA-TI software be installed. Download the free TINA-TI software from the TINA-TI folder.

## 13.1.1.2 TI Precision Designs

TI Precision Designs are analog solutions created by TI's precision analog applications experts and offer the theory of operation, component selection, simulation, complete PCB schematic and layout, bill of materials, and measured performance of many useful circuits. TI Precision Designs are available online at <a href="http://www.ti.com/ww/en/analog/precision-designs/">http://www.ti.com/ww/en/analog/precision-designs/</a>.

# 13.1.1.3 WEBENCH® Filter Designer

WEBENCH® Filter Designer is a simple, powerful, and easy-to-use active filter design program. The WEBENCH Filter Designer lets you create optimized filter designs using a selection of TI operational amplifiers and passive components from TI's vendor partners.

Available as a web-based tool from the WEBENCH® Design Center, WEBENCH® Filter Designer allows you to design, optimize, and simulate complete multistage active filter solutions within minutes.

### 13.2 Documentation Support

### 13.2.1 Related Documentation

The following documents are relevant to using the OPA454, and recommended for reference. All are available for download at www.ti.com unless otherwise noted.

- Application bulletin AB-038: Heat Sinking—TO-3 Thermal Model, SBOA021

- Application bulletin AB-039: Power Amplifier Stress and Power Handling Limitations, SBOA022

- Application bulletin AB-045: Op Amp Performance Analysis, SBOA054

- Application bulletin AB-067: Single-Supply Operation of Operational Amplifiers, SBOA059

- Application bulletin AB-105: Tuning in Amplifiers, SBOA067.

- Technical brief: PowerPAD Thermally-Enhanced Package, SLMA002.

Product Folder Links: OPA454

# 13.3 Community Resources