|                                                                          |                                                                                                                                                                                                                                                           | Devices Connected/Referenced |                                                                                         |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------|

| <b>Circuits</b><br>from the <b>Lab</b> <sup>®</sup><br>Reference Designs | Circuits from the Lab® reference designs are engineered and<br>tested for quick and easy system integration to help solve today's<br>analog, mixed-signal, and RF design challenges. For more<br>information and/or support, visit www.analog.com/CN0364. | AD7173-8                     | Low Power, 8-/16-Channel, 31.25 kSPS, 24-Bit, Highly Integrated $\Sigma$ - $\Delta$ ADC |

|                                                                          |                                                                                                                                                                                                                                                           | AD5700-1                     | Low Power HART Modem with<br>Internal Oscillator                                        |

|                                                                          |                                                                                                                                                                                                                                                           | ADuM5211                     | Dual-Channel Isolator with Integrated<br>DC-to-DC Converter                             |

|                                                                          |                                                                                                                                                                                                                                                           | ADuM3151                     | 3.75 kV, 7-Channel, SPIsolator Digital<br>Isolator for SPI                              |

|                                                                          |                                                                                                                                                                                                                                                           | ADG704                       | CMOS, Low Voltage, 4 Ω, 4-Channel<br>Multiplexer                                        |

|                                                                          |                                                                                                                                                                                                                                                           | ADP2441                      | 36 V, 1 A, Synchronous, Step-Down<br>DC-to-DC Regulator                                 |

# PLC/DCS Quad Channel Voltage and Current Input with HART Compatibility

# **EVALUATION AND DESIGN SUPPORT**

#### **Circuit Evaluation Boards**

CN-0364 Circuit Evaluation Board (EVAL-CN0364-SDPZ) System Demonstration Platform (EVAL-SDP-CB1Z) Design and Integration Files

Schematics, Layout Files, Bill of Materials

#### **CIRCUIT FUNCTION AND BENEFITS**

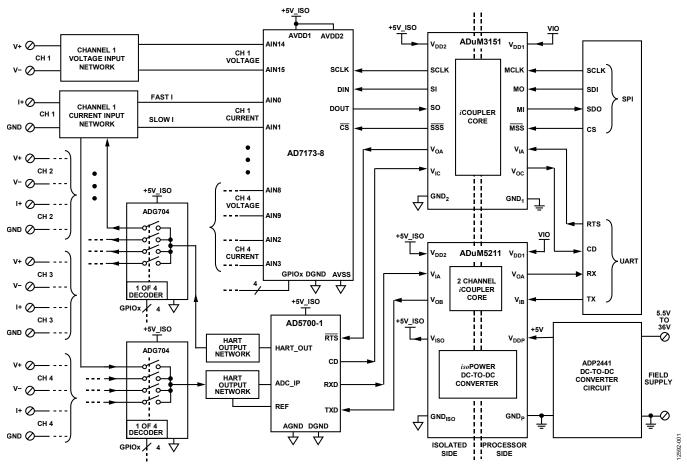

The circuit shown in Figure 1 provides a complete, fully isolated, highly flexible, quad channel analog input system suitable for programmable logic controllers (PLCs) and distributed control system (DCS) applications that require multiple voltage inputs and HART-compatible, 4 mA to 20 mA current inputs.

The analog input circuit is designed for group isolated industrial analog inputs and can support voltage and current input ranges including  $\pm 5$  V,  $\pm 10$  V, 0 V to +5 V, 0 V to +10 V, +4 mA to +20 mA, and 0 mA to +20 mA.

The circuit is powered from a standard 24 V bus supply and generates an isolated 5 V system supply voltage.

# **CIRCUIT DESCRIPTION**

The data conversion is performed by the AD7173-8 24-bit,  $\Sigma$ - $\Delta$  analog-to-digital converter (ADC). The AD7173-8 is software configurable and allows 8 fully differential or 16 single-ended input channels, offering great flexibility via an internal crosspoint multiplexer. The AD7173-8 is in a small 6 mm × 6 mm LFCSP package, making it ideal where space is a premium. The internal clock and precision 2.5 V voltage reference minimize external

components and result in additional space savings. The four programmable general-purpose output pins (GPIO0, GPIO1, GPO2, GPO3) allow external multiplexer control, which allows the control of the multiplexed HART interface and eliminates the need for additional control lines from the processor/controller. The AD7173-8 has internal calibration registers that can be programmed to provide offset and gain corrections for the full input path.

The AD5700-1 is the industry's lowest power and smallest footprint HART-compliant modem and is used in conjunction with the current input channels to form a HART-compatible, 4 mA to 20 mA receiver solution. The AD5700-1 includes a precision internal oscillator that provides additional space savings, especially in isolated applications.

The ADG704 multiplexer provides HART connectivity to the multiple current input channels.

The ADuM5211 isolates two data channels (Tx, Rx) and also provides the 5 V power isolation via integrated *iso*Power<sup>®</sup> technology. The ADuM3151 SPIsolator provides serial peripheral interface (SPI) isolation at clock rates of up to 17 MHz (B grade), as well as isolating three additional data channels.

The ADP2441 36 V, step-down, dc-to-dc regulator accepts an industrial standard 24 V supply, with wide tolerance on the input voltage. The ADP2441 steps the input voltage down to 5 V to power all controller side circuitry. The circuit also includes standard external protection on the 24 V supply terminals.

Rev. 0

Circuits from the Lab<sup>®</sup> reference designs from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2014 Analog Devices, Inc. All rights reserved.

# CN-0364

Figure 1. PLC/DCS Quad Channel Voltage and Current Input Front End (Simplified Schematic: All Connections and Decoupling Not Shown)

#### Voltage Input Circuit

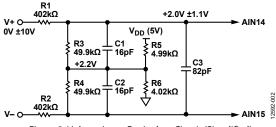

Figure 2 shows the voltage input network for Channel 1.

The circuit has differential inputs and supports an input range of up to  $\pm 10$  V with up to  $\pm 5$  V common-mode voltage. The input impedance is ~900 k $\Omega$ , and the high values of R1 and R2 also protect the input during any high voltage transient events.

The R1, R2, R3, and R4 resistors form a differential resistor divider. The matching of these resistors is critical to the dc accuracy of the circuit. Single point calibration is recommended to remove the initial errors. Multipoint calibration can be used to cancel temperature drift effects. The board is populated by default with 0.1%, 25 ppm/°C resistors for R1, R2, R3, and R4.

The R5 and R6 resistors set the common-mode voltage for the ADC. The AD7173-8 has an allowable input voltage range of 0 V to 3.9 V. The bias voltage of  $\pm 2.2$  V, along with the input divider resistors, level shifts and attenuates the  $\pm 10$  V input signal to  $\pm 1.1$  V centered on a common-mode voltage of  $\pm 2$  V at the ADC input.

Input common-mode noise filtering is provided by R1||R3/C1 and R2||R4/C2, and is approximately 200 kHz. Differential noise filtering is provided by R1||R3, R2||R4, and C3, and is approximately 20 kHz.

Table 1 summarizes the parameters of the four voltage input channels.

| Values Based on V               | vorst-Ca | ise Calcula   | tions)                                                                                                      |

|---------------------------------|----------|---------------|-------------------------------------------------------------------------------------------------------------|

| Parameter                       | Value    | Unit          | Test Conditions/<br>Comments                                                                                |

|                                 |          |               | Comments                                                                                                    |

| Input Impedance                 | 903      | kΩ            |                                                                                                             |

| Divider Ratio                   | 0.11     |               | Resistor divider of<br>402 kΩ and 49.9 kΩ                                                                   |

| Initial Error from<br>Resistors | 0.18     | %FSR<br>max   | 25°C, uncalibrated;<br>assumed 0.1% resistors                                                               |

| Error from Input<br>Leakage     | ±0.01    | %FSR          | ±10 V range; AD7173-8,<br>±2 nA typical leakage                                                             |

| Error from<br>Resistor Drift    | 18       | ppm/°C<br>max | Assumed 10 ppm/°C resistors                                                                                 |

|                                 | 9        | ppm/°C<br>max | Assumed 5 ppm/°C resistors                                                                                  |

| Error from<br>Reference Drift   | 10       | ppm/°C<br>max | Internal reference                                                                                          |

| Common Mode                     | ±5       | V             |                                                                                                             |

| Data Rate                       | 31.25    | kSPS          | 1 input enabled<br>(14.7 bit noise-free code<br>resolution for ±10 V)                                       |

|                                 | 1.55     | kSPS          | 4 channels, each fully<br>settled, sinc5+1 filter<br>(14.7 bit noise-free code<br>resolution for ±10 V)     |

|                                 | 6.25     | SPS           | 4 channels, each fully<br>settled, 50 HZ/60 Hz<br>reject (18.8 bit noise-free<br>code resolution for ±10 V) |

| Input Filter                    | 20       | kHz           | Differential                                                                                                |

|                                 | 200      | kHz           | Common mode                                                                                                 |

#### Table 1. Voltage Input Circuit Parameters (Maximum Values Based on Worst-Case Calculations)

# **Current Input Circuit**

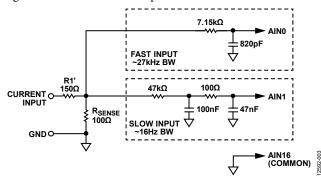

Figure 3. Current Input Equivalent Circuit (Simplified)

The circuit has four current input channels, supporting a maximum input range of 0 mA to 24 mA. The input impedance of the circuit is 250  $\Omega$ , and the input is referenced to ground. A precision 100  $\Omega$  current sense resistor is used so that a 24 mA input produces 2.4 V, which is within the 2.5 V full-scale range of the AD7173-8 (using the internal 2.5 V voltage reference). The board is populated by default with a 0.1%, 10 ppm/°C R<sub>SENSE</sub> resistor.

There are two input paths to separate ADC inputs. The fast input path is for channels not using HART, and the slow input path is for channels using HART.

The fast input path allows signals up to the full input bandwidth of the  $\Sigma$ - $\Delta$  ADC. It is also possible to use the internal sinc filters to reject the 1.2 kHz and 2.2 kHz HART frequencies. However, using the sinc filters requires running the relevant channel at the 400 SPS data rate (sinc3 filter), which increases the time required to convert all four channels.

The slow input contains a 16 Hz double-pole filter, which filters out the 1.2 kHz and 2.2 kHz HART digital signaling frequencies. Using this input, the  $\Sigma$ - $\Delta$  ADC can still run at its fast data rate and also reject the HART digital signaling frequencies. The time required to convert all four channels is not reduced. Operating the ADC at its fast data rate is especially useful if not all channels have HART enabled.

Table 2 summarizes the current input circuit parameters.

| Table 2. Current Input Circuit Parameters (Maximum |  |  |                  |

|----------------------------------------------------|--|--|------------------|

| Values Based on Worst-Case Calculations)           |  |  |                  |

|                                                    |  |  | Test Conditions/ |

| Down a tow      | Malara           | 11     | Test Conditions/                |  |

|-----------------|------------------|--------|---------------------------------|--|

| Parameter       | Value            | Unit   | Comments                        |  |

| Input Impedance | 250              | Ω      | Grounded                        |  |

| Error from      | N/A <sup>1</sup> | %FSR   | Per R <sub>SENSE</sub> resistor |  |

| Resistor        |                  | max    | specifications                  |  |

| Error from      | N/A <sup>1</sup> | ppm/°C | Per R <sub>SENSE</sub> resistor |  |

| Resistor Drift  |                  | max    | specifications                  |  |

| Error from      | 10               | ppm/°C | Internal reference              |  |

| Reference Drift |                  | max    |                                 |  |

| Data Rate       | 31.25            | kSPS   | 1 input enabled (14.8 bit       |  |

|                 |                  |        | noise-free code resolution      |  |

|                 |                  |        | for 0 mA to 20 mA)              |  |

|                 | 1.55             | kSPS   | 4 channels, each fully          |  |

|                 |                  |        | settled, sinc5+1 filter         |  |

|                 |                  |        | (14.8 bit p-p resolution        |  |

|                 |                  |        | for 0 mA to 20 mA)              |  |

|                 | 6.25             | SPS    | 4 channels, each fully          |  |

|                 |                  |        | settled, 50 Hz/60 Hz reject     |  |

|                 |                  |        | (18.1 bit p-p resolution for    |  |

|                 |                  |        | 0 mA to 20 mA)                  |  |

| Input Filter    | 27               | kHz    | Fast input                      |  |

|                 | 16               | Hz     | Slow input providing            |  |

|                 |                  |        | HART filtering                  |  |

$^{1}$  N/A = not applicable.

#### HART Input and Output Circuit

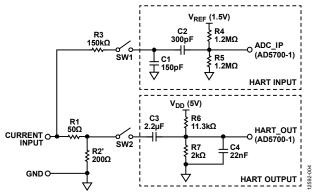

Figure 4 shows the HART input and output circuit.

Figure 4. HART Input and Output Circuits (Simplified)

The HART functionality is multiplexed between the four current input channels. The HART input and output networks are shared between the four channels using the two ADG704 multiplexers (SW1 and SW2 in Figure 4).

The HART input circuitry consists of a HART band-pass filter formed by R3, C1, C2, R4, and R5. This filter is described in the AD5700-1 data sheet. A switch (SW1) is used in each channel to switch the HART input circuitry to the active HART channel. The 150 k $\Omega$  resistor (R3) is present on each channel and is part of the HART band-pass filter, but also provides additional protection for the switch (SW1). The HART input connects directly to the current input terminal to ensure that the correct voltage levels are received at the ADC\_IP pin of the AD5700-1.

A switch (SW2) is used in each channel to switch the HART output circuitry to the active HART channel. Capacitor C3 couples the HART signal. The combination of R1, C3, R6, and R7 was carefully chosen to ensure that the voltage of the HART\_OUT pin of the AD5700-1 does not fall below GND during a 25 Hz, 4 mA to 20 mA input signal (representing the fastest allowable slew rate for a HART-enabled device).

### **Power Supply Circuit**

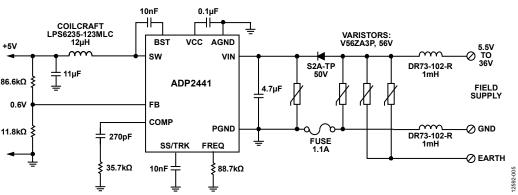

The evaluation board is powered by a 5.5 V to 36 V dc power supply and uses an on-board switching regulator to provide the 5 V supply to the system, as shown in Figure 5. In the test setup, the 5 V also powers the EVAL-SDP-CB1Z system demonstration platform (SDP) board. The EVAL-SDP-CB1Z SDP board provides a regulated 3.3 V for the VIO voltage.

The high switching frequency of the ADP2441 allows minimal output voltage ripple even when small inductors are used. Selecting the size of the inductor involves considering the trade-off between efficiency and transient response. A smaller inductor results in larger inductor current ripple, which provides excellent transient response but degrades efficiency. Due to the high switching frequency of the ADP2441, using shielded ferrite core inductors is recommended because of their low core losses and low electromagnetic interference (EMI).

In the Figure 5 circuit, the switching frequency is approximately 1 MHz with the 88.7 k $\Omega$  external resistor. The inductor value of 12  $\mu$ H (Coilcraft LPS6235-123MLC) is chosen from Table 8 of the ADP2441 data sheet.

The circuit is connected to the field supply of 5.5 V to 36 V using screw terminals. The EARTH terminal can be connected to an external earth connection or to the GND terminal if an external earth connection is not used.

Power inductors (DR73-102-R), varistors (V56ZA3P, 56 V), power diode (S2A-TP, 50 V), and a 1.1 A fuse provide additional input protection against high voltage transient events.

Figure 5. Power Supply Circuit (Simplified Schematic: All Connections Not Shown)

### Noise Test

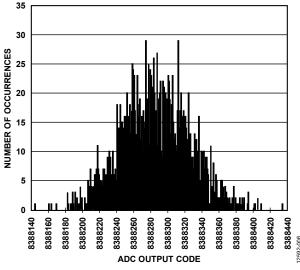

Evaluate the system noise by shorting the input terminals for each channel, which results in a zero differential voltage for the voltage input channels and grounded input for the current input channels. Gather the data with the inputs shorted, and compute the code spread and noise-free code resolution from the set number of samples.

This noise test can be done using the CN-0364 Evaluation Software. The code spread and noise-free code resolution of each channel can be obtained and the data displayed in a histogram. Figure 6 shows a histogram from sample data gathered from the voltage input of Channel 1.

Figure 6. Channel 1 Voltage Input, Inputs Shorted and Biased to Reference Voltage, 31.25 kSPS, Sinc5+1 Filter, 2000 Samples (15.8 Bit Noise-Free Code Resolution)

# HART Testing

The HART functionality was tested according to the HART physical layer test specification (HCF-TEST-2). The circuit met the requirements for the HART physical layer. More details on the HART specifications can be obtained directly from the HART Communication Foundation.

The rejection of the ADC input to the HART 1.2 kHz and 2.2 kHz signals was also measured. Table 3 shows the results.

#### Table 3. Rejection of 1.2 kHz and 2.2 kHz HART Frequencies

| Operating Mode                          | Frequency<br>(kHz) | Rejection<br>(dB) |

|-----------------------------------------|--------------------|-------------------|

| Slow Input Path, 31 kSPS Sinc5+1 Filter | 1.2                | 60.5              |

|                                         | 2.2                | 66.5              |

| Fast Input Path, 400 SPS Sinc3 Filter   | 1.2                | ≥74.4             |

|                                         | 2.2                | 66.6              |

A complete design support package for the EVAL-CN0364-SDPZ board including schematic, bill of materials, and layout can be downloaded from www.analog.com/CN0364-DesignSupport.

# **COMMON VARIATIONS**

When high channel data rates are required, the AD7175-2 ADC can be used. The AD7175-2 supports data rates of up to 250 kSPS, with channel switching rates of up to 50 kSPS. The AD7175-2 can achieve a resolution of 17.2 noise-free bits at the 250 kSPS data rate. Besides the higher data rates, the features of the AD7175-2 are similar to those of the AD7173-8.

For applications that require more than 150 mW of isolated power, the ADuM540x or ADuM347x can be used. The ADuM540x use *iso*Power technology to supply up to 500 mW of isolated power. The ADuM347x drive an external, discreet transformer to supply up to 2 W at up to 70% efficiency.

# **CIRCUIT EVALUATION AND TEST**

The circuit shown in Figure 1 uses the EVAL-CN0364-SDPZ evaluation board and the EVAL-SDP-CB1Z SDP controller board.

The EVAL-CN0364-SDPZ evaluation board features PMOD compatible headers for integration with external controller boards.

The CN-0364 Evaluation Software communicates with the SDP board to configure and capture data from the EVAL-CN0364-SDPZ evaluation board.

#### **Equipment Needed**

The following equipment is needed:

- A PC with a USB port and Windows<sup>®</sup> Vista (32-bit) or Windows 7 (32-bit)

- The EVAL-CN0364-SDPZ circuit evaluation board

- The EVAL-SDP-CB1Z SDP controller board

- The CN-0364 Evaluation Software

- A precision voltage and current source

- A power supply: 5.5 V to 36 V dc at 500 mA

#### **Getting Started**

Install the CN-0364 Evaluation Software, which is available for download at ftp://ftp.analog.com/pub/cftl/CN0364/. Follow the on-screen prompts to install and use the software. More information is available in the CN-0364 Software User Guide.

#### Functional Block Diagram

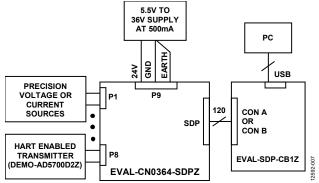

Figure 7 shows a function block diagram of the test setup.

Figure 7. Test Setup Functional Block Diagram

# CN-0364

#### Setup

The EVAL-CN0364-SDPZ evaluation board connects to the EVAL-SDP-CB1Z SDP board through a 120-pin mating connector found on both boards. The CN-0364 Evaluation Software and the SDP board allow the data to be analyzed using a PC.

The CN-0267 circuit (a complete 4 mA to 20 mA loop powered field instrument with HART interface) can be connected to easily test the HART physical layer functionality. The CN-0267 hardware responds to the HART commands available in the CN-0364 Evaluation Software.

External controllers can also be used to communicate with and power the evaluation board using the PMOD headers for SPI and UART communication.

Precision voltage and current sources can be used as input to the analog front end to evaluate system performance.

Figure 8 shows a photo of the EVAL-CN0364-SDPZ evaluation board.

Figure 8. Photo of EVAL-CN0364-SDPZ Evaluation Board

# LEARN MORE

CN-0364 Design Support Package.

SDP-B User Guide.

- CN-0267 Circuit Note, *Complete 4 mA to 20 mA Loop Powered Field Instrument with HART Interface*, Analog Devices.

- CN-0270 Circuit Note, *Complete 4 mA to 20 mA HART Solution*, Analog Devices.

- CN-0278 Circuit Note, *Complete 4 mA to 20 mA HART Solution* with Additional Voltage Output Capability, Analog Devices.

- CN-0321 Circuit Note, Fully Isolated, Single Channel Voltage and 4 mA to 20 mA Output with HART Connectivity, Analog Devices.

- CN-0328 Circuit Note, Completely Isolated 4-Channel Multiplexed HART Analog Output Circuit, Analog Devices.

- Mark Cantrell, *Recommendations for Control of Radiated Emissions with* iso*Power Devices*, Application Note AN-0971, Analog Devices.

HART<sup>®</sup> Communication Foundation

#### Data Sheets and Evaluation Boards

AD7173-8 Data Sheet

AD5700-1 Data Sheet

ADuM3151 Data Sheet

ADuM5211 Data Sheet

ADG704 Data Sheet

ADP2441 Data Sheet

#### **REVISION HISTORY**

12/14—Revision 0: Initial Version

(Continued from first page) Circuits from the Lab reference designs are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors. While you may use the Circuits from the Lab reference designs in the design of your product, no other license is granted by implication or otherwise under any patents or other intellectual property by application or use of the Circuits from the Lab reference designs. Information furnished by Analog Devices is believed to be accurate and reliable. However, Circuits from the Lab reference designs are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability, noninfringement or fitness for a particular purpose and no responsibility is assumed by Analog Devices for their use, nor for any infringements of patents or other rights of third parties that may result from their use. Analog Devices reserves the right to change any Circuits from the Lab reference designs at any time without notice but is under no obligation to do so.

©2014 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. CN12592-0-12/14(0)

Rev. 0 | Page 6 of 6