#### **MAX17491**

## Single-Phase Synchronous MOSFET Driver

### **General Description**

The MAX17491 is a single-phase synchronous noninverting MOSFET driver. The MAX17491 is intended to work with controller ICs like the MAX8736, MAX8786, or MAX17030 in multiphase notebook CPU core regulators.

The regulators can either step down directly from the battery voltage to create the core voltage or step down from the main system supply. The single-stage conversion method allows the highest possible efficiency, while the 2-stage conversion at higher switching frequency provides the minimum possible physical size.

The low-side driver is optimized to drive 3nF capacitive loads with 4ns/8ns typical fall/rise times, and the high-side driver with 8ns/10ns typical fall/rise times. Adaptive dead-time control prevents shoot-through currents and maximizes converter efficiency.

The MAX17491 features improved zero crossing and UVLO performance over the MAX8791/MAX8791B.

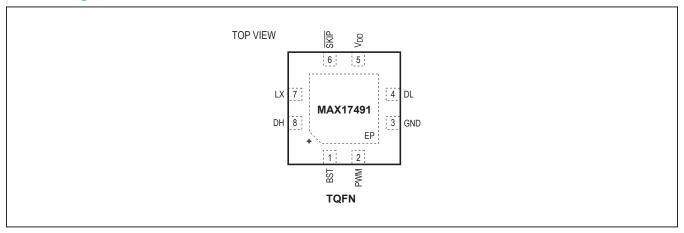

The MAX17491 is available in a small, lead-free, 8-pin, 3mm x 3mm TQFN package.

### **Applications**

- Notebooks/Desktops/Servers

- CPU Core Power Supplies

- Multiphase Step-Down Converters

Ordering Information appears at end of data sheet.

#### **Features**

- Single-Phase Synchronous MOSFET Driver

- 0.5Ω Low-Side On-Resistance

- 0.7Ω High-Side On-Resistance

- 10ns Minimum Guaranteed Dead Time

- Integrated Boost "Diode"

- 2V to 24V Input Voltage Range

- Selectable Pulse-Skipping Mode

- Low-Profile, 3mm x 3mm, TQFN Package

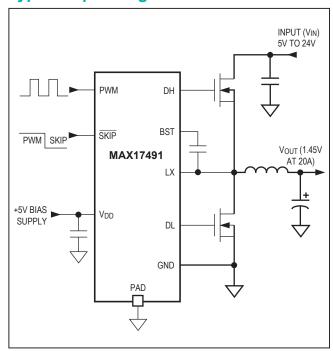

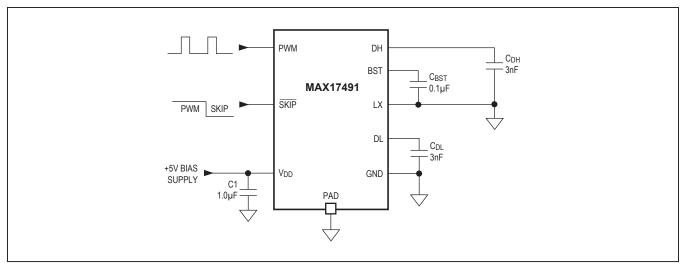

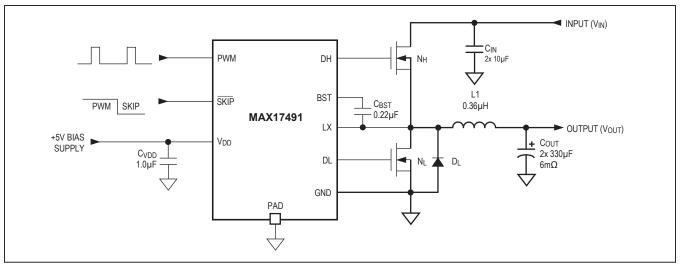

### **Typical Operating Circuit**

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND | 0.3V to +6V                       | Continuous Power Dissipation      |                |

|------------------------|-----------------------------------|-----------------------------------|----------------|

| SKIP to GND            | 0.3V to +6V                       | 8-Pin 3mm x 3mm TQFN              |                |

| PWM to GND             | 0.3V to +6V                       | (derate 14.4mW/°C above +70°C)    | 1150mW         |

| DL to GND              | 0.3V to (V <sub>DD</sub> + 0.3V)  | Operating Temperature Range       | 40°C to +105°C |

| BST to GND             | 0.3V to +36V                      | Junction Temperature              | +150°C         |

| DH to LX               | 0.3V to (V <sub>BST</sub> + 0.3V) | Storage Temperature Range         | 65°C to +150°C |

| BST to V <sub>DD</sub> | 0.3V to +30V                      | Lead Temperature (soldering, 10s) | +300°C         |

| BST to LX              | 0.3V to +6V                       | Soldering Temperature (reflow)    | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 8 TQFN-EP

| Package Code                           | TQ833+1    |  |  |  |

|----------------------------------------|------------|--|--|--|

| Outline Number                         | 21-0136    |  |  |  |

| Land Pattern Number                    | 90-0066    |  |  |  |

| Thermal Resistance, Four-Layer Board:  |            |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 69.54°C/W* |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 17.96°C/W  |  |  |  |

<sup>\*</sup>Based on JEDEC51-7

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

(Circuit of Figure 1, V<sub>DD</sub> = V<sub>SKIP</sub> = 5V, T<sub>A</sub> = -40°C to +105°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                                   | SYMBOL                 | CONDITIONS MIN                                                                                                          |      | TYP  | MAX  | UNITS |

|---------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Input Voltage Range                         | $V_{DD}$               | 4.20                                                                                                                    |      |      | 5.50 | V     |

| V <sub>DD</sub> Undervoltage-               | \/                     | Rising edge, PWM disabled below this level                                                                              |      | 3.7  | 4.05 | V     |

| Lockout Threshold                           | V <sub>UVLO(VDD)</sub> | Falling edge, PWM disabled below this level                                                                             | 3.30 | 3.40 | 3.75 | V     |

|                                             |                        | PWM = open; after the shutdown hold time has expired                                                                    |      | 0.08 | 0.20 |       |

| Quiescent Supply Current (V <sub>DD</sub> ) | I <sub>DD</sub>        | SKIP = GND, PWM = GND, LX = GND (after zero crossing); this state should be equivalent to low-power standby if LX = GND |      | 0.15 | 0.30 | mA    |

|                                             |                        | $\overline{\text{SKIP}}$ = GND or V <sub>DD</sub> , PWM = V <sub>DD</sub> , V <sub>BST</sub> = 5V                       |      | 0.35 | 0.70 |       |

| DRIVERS                                     |                        |                                                                                                                         |      |      |      |       |

|                                             | t <sub>ON(MIN)</sub>   | Minimum on-time                                                                                                         |      | 50   |      |       |

| PWM Pulse Width                             | <sup>t</sup> OFF(MIN)  | Minimum off-time; required to allow the zero-crossing comparator time to settle to the proper state                     |      | 300  |      | ns    |

| DL Propagation Delay                        | t <sub>PWM-DL</sub>    | PWM high-to-DL low                                                                                                      |      | 15   |      | ns    |

## **Electrical Characteristics (continued)**

(Circuit of Figure 1,  $V_{DD} = V_{\overline{SKIP}} = 5V$ ,  $T_A = -40^{\circ}C$  to +105°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                      | SYMBOL                  | CONDITIONS                                                            |                                                | MIN                   | TYP                         | MAX  | UNITS |  |

|--------------------------------|-------------------------|-----------------------------------------------------------------------|------------------------------------------------|-----------------------|-----------------------------|------|-------|--|

| DH Propagation Delay           | t <sub>PWM-DH</sub>     | PWM low-to-DH low                                                     |                                                |                       | 17                          |      | ns    |  |

| DL-to-DH Dead Time             |                         | Di falling to Dil vising                                              | T <sub>A</sub> = 0°C to +85°C                  | 10                    |                             |      | ns    |  |

| DL-to-DH Dead Time             | t <sub>DL-DH</sub>      | DL falling to DH rising                                               | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$ | 10                    |                             |      |       |  |

| DUA DI DA LE                   | 4                       | DH falling to DI riging                                               | $T_A = 0$ °C to +85°C                          | 10                    |                             | ne   |       |  |

| DH-to-DL Dead Time             | t <sub>DH-DL</sub>      | DH falling to DL rising                                               | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$ | 10                    |                             |      | ns    |  |

| DL Transition Time             | t <sub>F_DL</sub>       | Falling, 3.0nF load                                                   |                                                |                       | 10                          |      | ns    |  |

| DE Hansidon fille              | t <sub>R_DL</sub>       | Rising, 3.0nF load                                                    |                                                |                       | 12                          |      | 115   |  |

| DH Transition Time             | t <sub>F_DH</sub>       | Falling, 3.0nF load                                                   |                                                |                       | 8                           |      | ne    |  |

| Diff fransition fille          | t <sub>R_DH</sub>       | Rising, 3.0nF load                                                    |                                                |                       | 10                          |      | ns    |  |

| DH Driver                      | Power                   | BST - LX forced to 5V                                                 | DH, high state (pullup)                        |                       | 0.9                         | 2.5  | Ω     |  |

| On-Resistance                  | R <sub>ON(DH)</sub>     | BST - EX lorded to 5V                                                 | DH, low state (pulldown)                       |                       | 0.7                         | 2.1  | 12    |  |

| DL Driver                      | Paves                   | DL, high state (pullup)                                               |                                                |                       | 0.7                         | 1.6  | Ω     |  |

| On-Resistance                  | R <sub>ON(DL)</sub>     | DL, low state (pulldown)                                              |                                                |                       | 0.3                         | 0.9  | 12    |  |

| DH Driver Source Current       | I <sub>DH_</sub> SOURCE | DH forced to 2.5V, BST - LX forced to 5V                              |                                                |                       | 2.2                         |      | Α     |  |

| DH Driver Sink Current         | I <sub>DH_</sub> SINK   | DH forced to 2.5V, BST - LX forced to 5V                              |                                                |                       | 2.7                         |      | Α     |  |

| DL Driver Source Current       | I <sub>DL_</sub> SOURCE | DL forced to 2.5V                                                     |                                                |                       | 2.7                         |      | Α     |  |

| DL Driver Sink Current         | I <sub>DL_SINK</sub>    | DL forced to 2.5V                                                     |                                                |                       | 8                           |      | А     |  |

| Zero-Crossing Threshold        | $V_{ZX}$                | GND - LX, SKIP = GND                                                  |                                                |                       | 1.5                         |      | mV    |  |

| Boost On-Resistance            | RON(BST)                | $V_{DD}$ = 5V, DH = LX = GND (pulldown state),<br>$I_{BST}$ = 10mA    |                                                |                       | 5                           | 8    | Ω     |  |

|                                |                         |                                                                       |                                                | V <sub>DD</sub> - 0.4 |                             |      |       |  |

| PWM Input Levels               |                         |                                                                       | V <sub>DD</sub> /2<br>- 0.4                    |                       | V <sub>DD</sub> /2<br>+ 0.4 | V    |       |  |

|                                |                         | Low (DH = low, DL = high                                              | h)                                             |                       |                             | 0.4  |       |  |

| DIAMA I                        |                         | Sink; PWM forced to V <sub>DD</sub> Source; PWM forced to GND         |                                                | -370                  | -200                        | -110 |       |  |

| PWM Input Current              | I <sub>PWM</sub>        |                                                                       |                                                | 110                   | 200                         | 370  | μΑ    |  |

| Midlevel Shutdown Hold<br>Time | t <sub>MID</sub>        |                                                                       |                                                | 120                   | 300                         | 600  | ns    |  |

|                                |                         | Rising edge Falling edge                                              |                                                |                       | 1.7                         | 2.4  | _     |  |

| SKIP Input Threshold           |                         |                                                                       |                                                | 0.8                   | 1.5                         |      | V     |  |

| SKIP Input Current             | I <sub>SKIP</sub>       | Sink; SKIP forced to 0.8V to V <sub>DD</sub> , T <sub>A</sub> = +25°C |                                                | -4                    | -2                          | -0.5 | μA    |  |

| Thermal-Shutdown Threshold     | T <sub>SHDN</sub>       | Hysteresis = 20°C                                                     |                                                |                       | +160                        |      | °C    |  |

Note 1: Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Maximum and minimum limits over temperature are guaranteed through correlation using statistical-quality-control (SQC) methods.

www.maximintegrated.com Maxim Integrated | 3

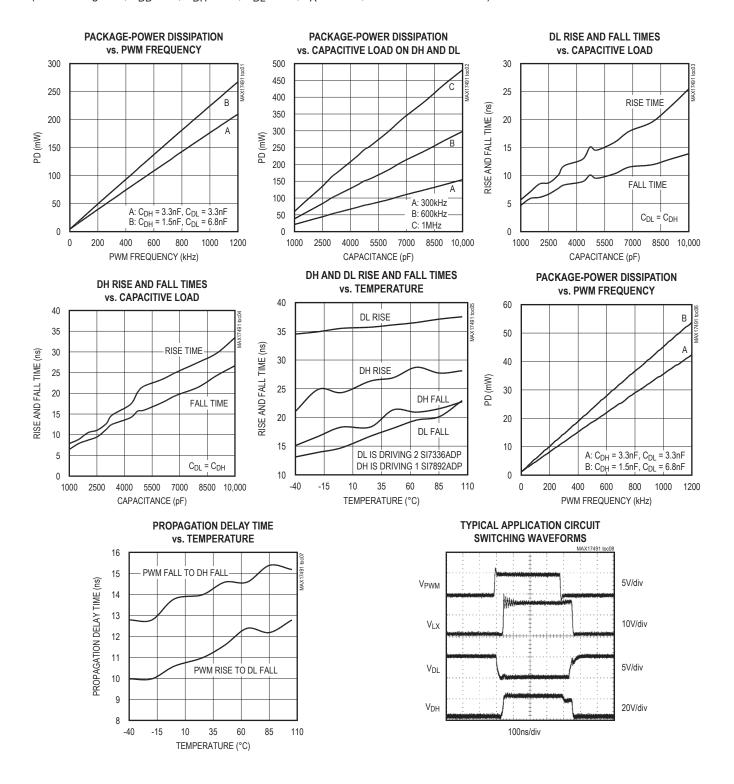

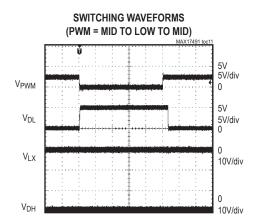

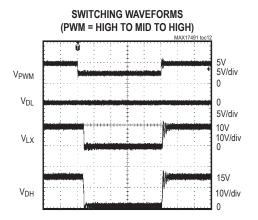

## **Typical Operating Characteristics**

(Circuit of Figure 1,  $V_{DD}$  = 5V,  $C_{DH}$  = 3nF,  $C_{DL}$  = 3nF,  $T_A$  = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

(Circuit of Figure 1, V<sub>DD</sub> = 5V, C<sub>DH</sub> = 3nF, C<sub>DL</sub> = 3nF, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **Pin Configuration**

## **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BST             | Boost Flying-Capacitor Connection. Gate-drive power supply for DH high-side gate driver. Connect a 0.1µF or 0.22µF capacitor between BST and LX.                                                                                                                                                                                                                                                                                                                                                                |

| 2   | PWM             | PWM Input. Noninverting DH control input from the controller IC:  Logic-high: DH = high (BST), DL = low (PGND).  Midlevel: After the midlevel hold time expires, the controller enters standby mode. DH and DL pulled low.  Logic-low: DH = low (LX), DL = high (V <sub>DD</sub> ) when SKIP = high.  Internal pullup and pulldown resistors create the midlevel and prevent the controller from triggering an on-time if this input is left unconnected (not soldered properly) or driven by a high impedance. |

| 3   | GND             | Power Ground for the DL Gate Drivers and Analog Ground. Connect exposed pad to GND.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | DL              | PWM Low-Side Gate-Driver Output. Swings between GND and V <sub>DD</sub> . DL forced high in shutdown.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5   | V <sub>DD</sub> | Supply Voltage Input for the DL Gate Drivers. Connect to 4.2V to 5.5V supply and bypass to GND with a 1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | SKIP            | Active-Low Pulse-Skipping Mode. Enable pulse-skipping mode (zero-crossing comparator enabled) when the driver is operating in SKIP mode:  SKIP = V <sub>DD</sub> PWM mode SKIP = GND skip mode An internal pulldown current pulls the controller into the low-power pulse-skipping state if this input is left unconnected (not soldered properly) or driven by a high impedance.                                                                                                                               |

| 7   | LX              | Switching Node and Inductor Connection. Low-power supply for the DH high-side gate driver.  LX connects to the skip-mode zero-crossing comparator.                                                                                                                                                                                                                                                                                                                                                              |

| 8   | DH              | External High-Side n-Channel MOSFET Gate-Driver Output. Swings between LX and BST.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| _   | EP              | Exposed Pad. Connect to ground through multiple vias to reduce the thermal impedance.                                                                                                                                                                                                                                                                                                                                                                                                                           |

www.maximintegrated.com Maxim Integrated 6

Figure 1. Test Circuit

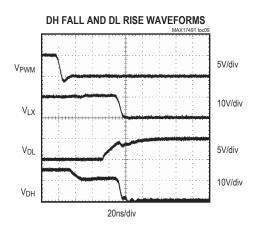

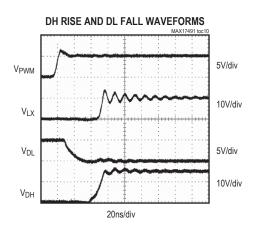

Figure 2. Timing Diagram

Figure 3. Typical MOSFET-Driver Application Circuit

### **Table 1. Typical Components**

| DESIGNATION                           | QTY           | COMPONENT SUPPLIERS               |

|---------------------------------------|---------------|-----------------------------------|

| N <sub>H</sub>                        | 1 per phase   | Siliconix Si4860DY                |

| N <sub>L</sub>                        | 1–2 per phase | Siliconix Si4336DY                |

| BST Capacitor (C <sub>BST</sub> )     | 1 per phase   | 0.1μF or 0.22μF ceramic capacitor |

| Schottky Diode                        | Optional      | 3A, 40V Schottky diode            |

| Inductor (L1)                         | 1 per phase   | 0.36μH, 26A, 0.9mΩ power inductor |

| Output Capacitors (C <sub>OUT</sub> ) | 1–2 per phase | 330μF, 6mΩ per phase              |

| Input Capacitors (C <sub>IN</sub> )   | 1–2 per phase | 10μF, 25V X5R ceramic capacitors  |

### **Detailed Description**

The MAX17491 single-phase gate driver, along with the MAX8736, MAX8786, or MAX17030 multiphase controllers, provide flexible multiphase CPU core-voltage supplies. The low driver resistance allows up to 7A output peak current. Each MOSFET driver in the MAX17491 can drive 3nF capacitive loads with only 9ns propagation delay and 4ns/8ns (typ) fall/rise times, allowing operation up to 3MHz per phase. Larger capacitive loads are allowable but result in longer propagation and transition times. Adaptive dead-time control prevents shoot-through currents and maximizes converter efficiency while allowing operation with a variety of MOSFETs and PWM controllers. An input undervoltage-lockout (UVLO) circuit allows proper power-on sequencing.

#### **PWM Input**

The drivers for the MAX17491 are disabled—DH and DL pulled low—if the PWM input remains in the midlevel window for at least 300ns (typ). Once the PWM signal is driven high or low, the MAX17491 immediately exits the low-current shutdown state and resumes active operation. Outside the shutdown state, the drivers are enabled based on the rising and falling thresholds specified in the *Electrical Characteristics*.

#### **MOSFET Gate Drivers (DH, DL)**

The high-side driver (DH) has a  $0.9\Omega$  sourcing resistance and  $0.7\Omega$  sinking resistance, resulting in 2.2A peak sourcing current and 2.7A peak sinking current with a 5V supply voltage. The low-side driver (DL) has a typical  $0.7\Omega$  sourcing resistance and  $0.3\Omega$  sinking resistance, yielding 2.7A peak sourcing current and 8A peak sinking current. This reduces switching losses, making the MAX17491 ideal for both high-frequency and high-output-current applications.

www.maximintegrated.com Maxim Integrated | 8

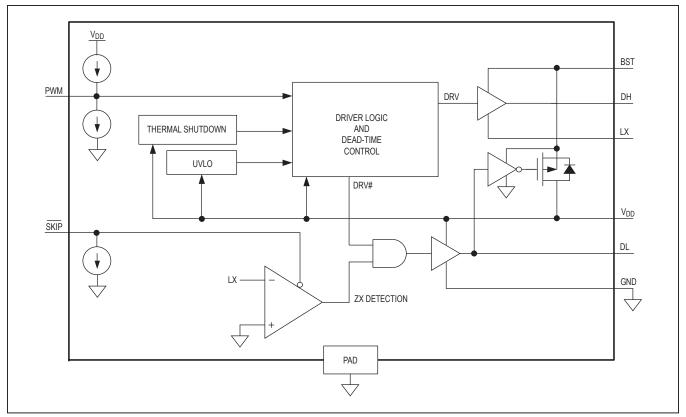

Figure 4. Overview Block Diagram

#### **Adaptive Shoot-Through Protection**

The DH and DL drivers are optimized for driving moderately sized high-side and larger low-side power MOSFETs. This is consistent with the low duty factor seen in the notebook CPU environment, where a large  $V_{\text{IN}}$  -  $V_{\text{OUT}}$  differential exists. Two adaptive dead-time circuits monitor the DH and DL outputs and prevent the opposite-side FET from turning on until the other is fully off. The MAX17491 constantly monitors the low-side driver output (DL) voltage, and only allows the high-side driver to turn on only when DL drops below the adaptive threshold. Similarly, the controller monitors the high-side driver output (DH) and prevents the low side from turning on until DH falls below the adaptive threshold before allowing DL to turn on.

The adaptive driver dead time allows operation without shoot-through with a wide range of MOSFETs, minimizing delays and maintaining efficiency. There must be a low-resistance, low-inductance path from the DL and DH drivers to the MOSFET gates for the adaptive dead-time circuits to work properly; otherwise, the sense circuitry in

the MAX17491 interprets the MOSFET gates as off while charge actually remains. Use very short, wide traces (50 mils to 100 mils wide if the MOSFET is 1in from the driver).

#### **Internal Boost Switch**

The MAX17491 uses a bootstrap circuit to generate the necessary drive voltage to fully enhance the high-side n-channel MOSFET. The internal p-channel MOSFET creates an ideal diode, providing a low voltage drop between  $V_{DD}$  and BST.

The selected high-side MOSFET determines appropriate boost capacitance values (C<sub>BST</sub> in Figure 1), according to the following equation:

#### $C_{BST} = Q_{GATE} / \Delta V_{BST}$

where  $Q_{GATE}$  is the total gate charge of the high-side MOSFET and  $\Delta V_{BST}$  is the voltage variation allowed on the high-side MOSFET driver. Choose  $\Delta V_{BST} = 0.1 V$  to 0.2V when determining  $C_{BST}$ . The boost flying capacitor should be a low equivalent-series resistance (ESR) ceramic capacitor.

www.maximintegrated.com Maxim Integrated | 9

#### 5V Bias Supply (V<sub>DD</sub>)

$V_{DD}$  provides the supply voltage for the internal logic circuits. Bypass  $V_{DD}$  with a 1µF or larger ceramic capacitor to GND to limit noise to the internal circuitry. Connect these bypass capacitors as close as possible to the IC.

#### Input Undervoltage Lockout

When  $V_{DD}$  is below the UVLO threshold, DH and DL are held low. Once  $V_{DD}$  is above the UVLO threshold and while PWM is low, DL is driven high and DH is driven low. This prevents the output of the converter from rising before a valid PWM signal is applied.

#### **Low-Power Pulse Skipping**

The MAX17491 enters into low-power pulse-skipping mode when SKIP is pulled low. In skip mode, an inherent automatic switchover to pulse-frequency modulation (PFM) takes place at light loads. A zero-crossing comparator truncates the low-side switch on-time at the  $inductor \, current \'s \, zero \, crossing. \, The \, comparator \, senses \, the \,$ voltage across LX and GND. Once V<sub>LX</sub> - V<sub>GND</sub> drops below the zero-crossing comparator threshold (see the Electrical Characteristics), the comparator forces DL low. This mechanism causes the threshold between pulse-skipping PFM and nonskipping PWM operation to coincide with the boundary between continuous and discontinuous inductor-current operation. The PFM/PWM crossover occurs when the load current of each phase is equal to 1/2 the peak-to-peak ripple current, which is a function of the inductor value. For a battery input range of 7V to 20V, this threshold is relatively constant, with only a minor dependence on the input voltage due to the typically low duty cycles. The switching waveforms can appear noisy and asynchronous when light loading activates the pulse-skipping operation, but this is a normal operating condition that results in high light-load efficiency.

## **Applications Information**

#### **Power-MOSFET Selection**

Most of the following MOSFET guidelines focus on the challenge of obtaining high load-current capability when using high-voltage (> 20V) AC adapters. Low-current applications usually require less attention. The high-side MOSFET (N<sub>H</sub>) must be able to dissipate the resistive losses plus the switching losses at both  $V_{IN(MIN)}$  and  $V_{IN(MAX)}$ . Calculate both these sums. Ideally, the losses at  $V_{IN(MIN)}$  should be roughly equal to losses at  $V_{IN(MIN)}$  are significantly higher than the losses at  $V_{IN(MAX)}$ , consider increasing the size of  $N_H$  (reducing  $R_{DS(ON)}$  but increasing  $C_{GATE}$ ). Conversely, if the losses at  $V_{IN(MAX)}$  are significantly

higher than the losses at  $V_{IN(MIN)}$ , consider reducing the size of  $N_H$  (increasing  $R_{DS(ON)}$ ) but reducing  $C_{GATE}$ ). If  $V_{IN}$  does not vary over a wide range, the minimum power dissipation occurs where the resistive losses equal the switching losses. Choose a low-side MOSFET that has the lowest possible on-resistance ( $R_{DS(ON)}$ ), comes in a moderate-sized package (i.e., one or two 8-pin SOs, DPAK, or D2PAK), and is reasonably priced. Ensure that the DL gate driver can supply sufficient current to support the gate charge and the current injected into the parasitic gate-to-drain capacitor caused by the high-side MOSFET turning on; otherwise, cross-conduction problems can occur.

#### **MOSFET Power Dissipation**

Worst-case conduction losses occur at the duty factor extremes. For the high-side MOSFET ( $N_H$ ), the worst-case power dissipation due to resistance occurs at the minimum input voltage:

$$PD(N_{H} | RESISTIVE) = \left(\frac{V_{OUT}}{V_{IN}}\right) \left(\frac{I_{LOAD}}{\eta_{TOTAL}}\right)^{2} R_{DS(ON)}$$

where  $\eta_{TOTAL}$  is the total number of phases. Generally, a small high-side MOSFET is desired to reduce switching losses at high input voltages. However, the  $R_{DS(ON)}$  required to stay within package-power dissipation often limits how small the MOSFETs can be. Again, the optimum occurs when the switching losses equal the conduction  $(R_{DS(ON)})$  losses. High-side switching losses do not usually become an issue until the input is greater than approximately 15V.

Calculating the power dissipation in high-side MOSFETs  $(N_H)$  due to switching losses is difficult since it must allow for difficult quantifying factors that influence the turn-on and turn-off times. These factors include the internal gate resistance, gate charge, threshold voltage, source inductance, and PCB layout characteristics.

The following switching-loss calculation provides only a very rough estimate and is no substitute for prototype evaluation, preferably including verification using a thermocouple mounted on  $N_{\text{H}}$ :

where  $C_{OSS}$  is the  $N_H$  MOSFET's output capacitance,  $Q_{G(SW)}$  is the charge needed to turn on the high-side MOSFET, and  $I_{GATE}$  is the peak gate-drive source/sink current (5A typ).

Switching losses in the high-side MOSFET can become an insidious heat problem when maximum AC adapter voltages are applied due to the squared term in the switching-loss equation above. If the high-side MOSFET chosen for adequate  $R_{\mbox{\footnotesize{DS(ON)}}}$  at low battery voltages becomes extraordinarily hot when biased from  $V_{\mbox{\footnotesize{IN(MAX)}}}$ , consider choosing another MOSFET with lower parasitic capacitance.

For the low-side MOSFET (N<sub>L</sub>), the worst-case power dissipation always occurs at the maximum input voltage:

$$PD\left(N_{L} \; RESISTIVE\right) = \left[1 - \left(\frac{V_{OUT}}{V_{IN(MAX)}}\right)\right] \left(\frac{I_{LOAD}}{\eta_{TOTAL}}\right)^{2} R_{DS(ON)}$$

The worst case for MOSFET power dissipation occurs under heavy load conditions that are greater than  $I_{LOAD(MAX)}$ , but are not quite high enough to exceed the current limit and cause the fault latch to trip. The MOSFETs must have a good-sized heatsink to handle the overload power dissipation. The heatsink can be a large copper field on the PCB or an externally mounted device.

An optional Schottky diode only conducts during the dead time when both the high-side and low-side MOSFETs are off. Choose a Schottky diode with a forward voltage low enough to prevent the low-side MOSFET body diode from turning on during the dead time, and a peak current rating higher than the peak inductor current. The Schottky diode must be rated to handle the average power dissipation per switching cycle. This diode is optional and can be removed if efficiency is not critical.

# IC Power Dissipation and Thermal Considerations

Power dissipation in the IC package comes mainly from driving the MOSFETs. Therefore, it is a function of both switching frequency and the total gate charge of the selected MOSFETs. The total power dissipation when both drivers are switching is given by:

$$PD(IC) = I_{BIAS} \times 5V$$

where  $I_{BIAS}$  is the bias current of the 5V supply calculated in the 5V Bias Supply ( $V_{DD}$ ) section. The rise in die temperature due to self-heating is given by the following formula:

$$\Delta T_{,J} = \theta_{,JA} \times PD(IC)$$

where PD(IC) is the power dissipated by the device, and  $\theta_{JA}$  is the package's thermal resistance. The typical thermal resistance is 69.54°C/W for the 3mm x 3mm TQFN package.

#### Avoiding dV/dt Turning on the Low-Side MOSFET

At high input voltages, fast turn-on of the high-side MOSFET can momentarily turn on the low-side MOSFET due to the high dV/dt appearing at the drain of the low-side MOSFET. The high dV/dt causes a current flow through the Miller capacitance (CRSS) and the input capacitance (CISS) of the low-side MOSFET. Improper selection of the low-side MOSFET that results in a high ratio of CRSS/CISS makes the problem more severe. To avoid this problem, minimize the ratio of CRSS/CISS when selecting the low-side MOSFET. Adding a  $1\Omega$  to  $4.7\Omega$  resistor between BST and CBST can slow the high-side MOSFET turn-on. Similarly, adding a small capacitor from the gate to the source of the high-side MOSFET has the same effect. However, both methods work at the expense of increased switching losses.

#### **Layout Guidelines**

The MAX17491 MOSFET driver sources and sinks large currents to drive MOSFETs at high switching speeds. The high di/dt can cause unacceptable ringing if the trace lengths and impedances are not well controlled. The following PCB layout guidelines are recommended when designing with the MAX17491:

- Place all decoupling capacitors as close as possible to their respective IC pins.

- Minimize the length of the high-current loop from the input capacitor, the upper switching MOSFET, and the low-side MOSFET back to the input-capacitor negative terminal.

- 3) Provide enough copper area at and around the switching MOSFETs and inductors to aid in thermal dissipation.

- 4) Connect GND of the MAX17491 as close as possible to the source of the low-side MOSFETs.

A sample layout is available in the MAX17030 evaluation kit

## **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |

|--------------|-----------------|-------------|

| MAX17491GTA+ | -40°C to +105°C | 8 TQFN-EP*  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

## **Chip Information**

PROCESS: BICMOS

## MAX17491

## Single-Phase Synchronous MOSFET Driver

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                    | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------|------------------|

| 0                  | 6/10             | Initial release                                | _                |

| 1                  | 1/20             | Updated the Package thermal resistance values. | 2, 11            |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Maxim Integrated:

MAX17491GTA+ MAX17491GTA+T