### **Smart Two Channel Low-Side Switch**

#### **Features**

- Power limitation

- Overtemperature monitoring

- · Overload protection

- Short circuit protection

- Diagnostic feedback

- · Overvoltage protection

- μC compatible input

- Electrostatic discharge (ESD) protection

### **Product Summary**

| Supply voltage       | Vs              | 6.5 - 45 | V |

|----------------------|-----------------|----------|---|

| Drain source voltage | $V_{DS(AZ)max}$ | 65       | V |

| On resistance        | $R_{ON(typ)}$   | 0.25     | Ω |

| Output current       | $I_D$           | 2 x 4    | Α |

| Nom. output current  | $I_{D(ISO)}$    | 2 x 1.3  | Α |

#### **Application**

- All kinds of resistive and inductive loads (relays, electromagnetic valves)

- μC compatible power switch for 12 and 24 V applications

- Solenoid control switch in automotive and industrial control systems

#### **General description**

Double channel Low-Side-Switch in Smart Power Technology (SPT) with two seperate inputs and two open drain DMOS output stages. The TLE 5224 G2 is fully protected by embedded protection functions and designed for automotive and industrial applications.

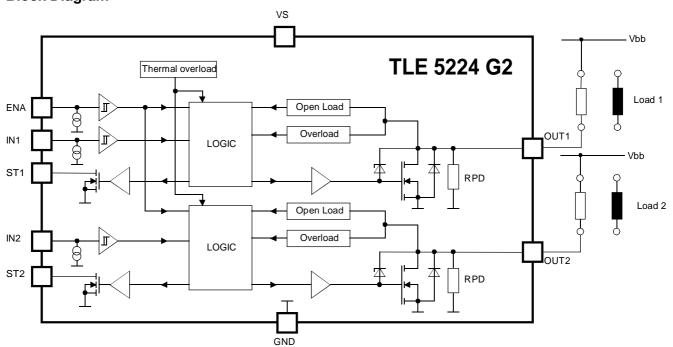

#### **Block Diagram**

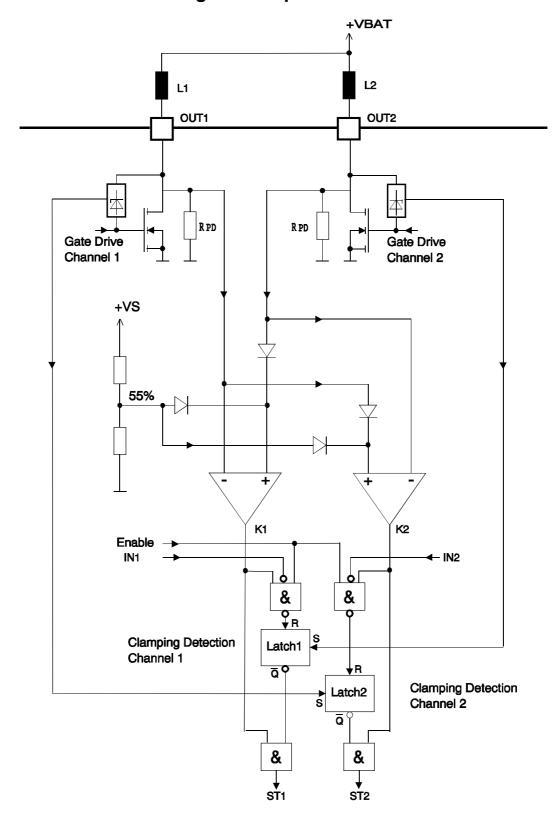

## **Block Diagram of Open Load Detection**

## Maximum Ratings for $T_j = -40$ °C to 150°C

| Parameter                                     | Symbol                       | Values                 | Unit         |     |

|-----------------------------------------------|------------------------------|------------------------|--------------|-----|

| Supply voltage                                |                              | $V_{\rm S}$            | - 0.3 + 60   | V   |

| Supply voltage operational range              |                              | V <sub>S</sub>         | + 4.8 + 45   | V   |

| Continuous drain source voltage (OUT1,        | OUT2)                        | $V_{	extsf{DS}}$       | 45           | V   |

| Input voltage IN1, IN2, ENA                   |                              | $V_{IN}$               | - 0.3 + 6    | V   |

| Status output voltage                         |                              | $V_{\rm ST}$           | - 0.3 + 32   | V   |

| Operating temperature range                   |                              | T <sub>j</sub>         | - 40 + 150   | °C  |

| Storage temperature range                     |                              | $T_{ m stg}$           | - 55 + 150   |     |

| Output current per channel                    |                              | I <sub>D(lim)</sub>    | self limited | Α   |

| Status output current                         |                              | I <sub>ST</sub>        | - 5 + 5      | mA  |

| Inductive load switch-off energy dissipation, |                              |                        |              | mJ  |

| single pulse                                  | T <sub>j</sub> = 150°C       | <b>E</b> <sub>AS</sub> | 400          |     |

| Thermal resistance                            | junction - case <sup>1</sup> | $R_{thJC}$             | 12           | K/W |

|                                               | junction - ambient           | $R_{thJA}$             | 75           |     |

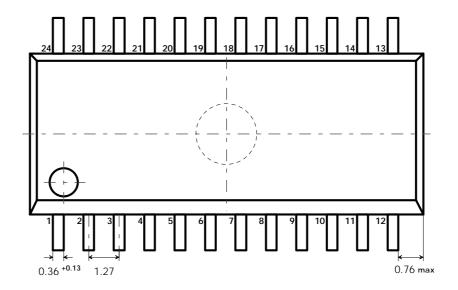

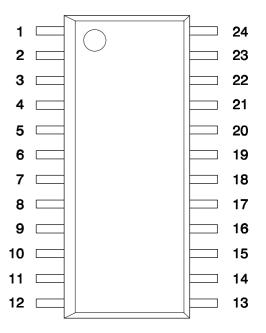

### Pin Definitions and Functions Pin Configuration(top view)

| Pin         | Symbol | Function                       |

|-------------|--------|--------------------------------|

| 1           | IN1    | Control input channel 1        |

| 2           | ST2    | Status output channel 2        |

| 3           | OUT2   | Power output channel 2         |

| 4           | N.C.   | Not connected, cooling         |

| 5,6,7,8     | GND    | Ground, cooling                |

| 9,10        | N.C.   | Not connected, cooling         |

| 11          | ENA    | Enable input for both channels |

| 12          | Vs     | Supply voltage                 |

| 13,14,15,16 | N.C.   | Not connected, cooling         |

| 17,18,19,20 | GND    | Ground, cooling                |

| 21          | N.C.   | Not connected, cooling         |

| 22          | OUT1   | Power output channel 1         |

| 23          | ST1    | Status output channel 1        |

| 24          | IN2    | Control input channel 2        |

Semiconductor Group Page 3 03.02.97

<sup>&</sup>lt;sup>1</sup> Case = Pin 5 to 8 and 17 to 20. Additionally the pins not connected (N.C.) have to be connected to the ground plane used as thermal heatsink to achieve the best thermal resistance.

| <b>Electrical Charact</b> | eristics |

|---------------------------|----------|

|---------------------------|----------|

| Parameter and Conditions                                                  |                                  | Symbol                | Values |      |     | Unit |

|---------------------------------------------------------------------------|----------------------------------|-----------------------|--------|------|-----|------|

| $V_s = 6.5 \text{ to } 45 \text{ V} \text{ ; } T_i = -40 \text{ °C to +}$ | 150 °C                           |                       | min    | typ  | max |      |

| (unless otherwise specified)                                              |                                  |                       |        |      |     |      |

| 1. Power Supply (V <sub>s</sub> )                                         |                                  |                       |        |      |     |      |

| Supply current (Outputs ON)                                               | $V_S = 45 \text{ V}$             | Is                    |        |      | 5   | mA   |

|                                                                           | $V_{\text{S}} \leq 18 \text{ V}$ |                       |        | 2    | 4   |      |

| Supply current (Output OFF)                                               | $V_{\text{S}} \leq 18 \text{ V}$ | Is                    |        | 1    | 2   | mΑ   |

| Operating voltage                                                         |                                  | V <sub>S</sub>        | 4.8    |      | 45  | V    |

| 2. Power Outputs                                                          |                                  |                       |        |      |     |      |

| ON state resistance;                                                      | T <sub>j</sub> = 25 ° C          | $R_{\rm DS(ON)}$      |        | 0.25 |     | Ω    |

| $I_D = 4A; \ V_S \ge 9.5 \ V$                                             | $T_j = 150$ °C                   |                       |        |      | 0.5 |      |

| Z-Diode clamping voltage (OUT1,                                           | OUT2)                            | $V_{DS(AZ)}$          | 45     |      | 65  | V    |

| Pull down resistor                                                        | T <sub>j</sub> = 25 ° C          | R <sub>PD</sub>       | 14     | 20   | 26  | kΩ   |

|                                                                           | $T_j \le 125  ^{\circ}  C$       |                       | 10     |      | 40  |      |

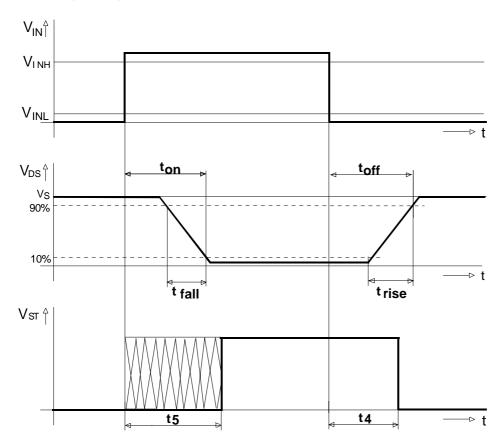

| Output on delay time <sup>2</sup>                                         | $I_D = 0.2 A$                    | <i>t</i> on           | 10     | 25   | 40  | μs   |

| Output off delay time <sup>2</sup>                                        | $I_D = 2 A$                      | $t_{ m off}$          |        | 50   |     |      |

| Output on fall time <sup>2</sup>                                          | $I_D = 0.2 A$                    | $t_{fall}$            |        | 20   |     |      |

| Output off rise time <sup>2</sup>                                         | $I_D = 2 A$                      | $t_{\sf rise}$        |        | 25   |     |      |

| Output off status delay time <sup>2</sup>                                 | $I_D = 2 A$                      | $t_4$                 | 20     | 40   | 60  |      |

| Output on status delay time <sup>2 3 4</sup>                              |                                  | <i>t</i> <sub>5</sub> |        |      | 50  |      |

| Overload switch-off delay time <sup>3</sup>                               |                                  | $t_{ m DSO}$          | 50     |      | 150 |      |

| 3. Digital Inputs (IN1, IN2, ENA)                                         |                                  |                       |        |      |     |      |

| Input low voltage                                                         |                                  | $V_{INL}$             | - 0.3  |      | 1.0 | V    |

| Input high voltage                                                        |                                  | $V_{INH}$             | 2.0    |      | 6.0 | V    |

| Input voltage hysteresis                                                  |                                  | $V_{INHys}$           | 0.2    |      | 0.6 | V    |

| Input pull down current                                                   | $V_{IN}$ =5 V; $V_S \ge 9$ V     | I <sub>IN</sub>       | 50     | 100  | 140 | μΑ   |

| Enable pull down current                                                  | $V_{ENA}$ =5 V; $V_{S} \ge 9$ V  | <b>I</b> ENA          | 15     | 30   | 45  | μΑ   |

| 4. Digital Status Outputs (ST1, S                                         | T2), open Drain                  |                       |        |      |     |      |

| Output voltage low                                                        | $I_{ST} = 2 \text{ mA}$          | V <sub>STL</sub>      |        |      | 0.5 | V    |

| Leakage current high                                                      |                                  | I <sub>STH</sub>      |        |      | 10  | μΑ   |

$<sup>^2</sup>$  See timing diagram, resitive load condition;  $V_S \geq 9 \ V$   $^3$  This parameter will not be tested but assured by design

<sup>&</sup>lt;sup>4</sup> Time till status valid after switching on or error detection

#### **Electrical Characteristics**

| Parameter and Conditions                                                                                      | Symbol | Values |     |     | Unit |

|---------------------------------------------------------------------------------------------------------------|--------|--------|-----|-----|------|

| $V_S = 6.5 \text{ to } 45 \text{ V} \text{ ; } T_i = -40 ^{\circ}\text{C} \text{ to } + 150 ^{\circ}\text{C}$ |        | min    | typ | max |      |

| (unless otherwise specified)                                                                                  |        |        |     |     |      |

#### 5. Diagnostic Functions

| Open load detection voltage            | V <sub>S</sub> ≤ 18 V        | $V_{\rm DS(OL)}$    | 0.51*V <sub>S</sub>   |     | 0.58*V <sub>S</sub>   | V  |

|----------------------------------------|------------------------------|---------------------|-----------------------|-----|-----------------------|----|

| (Output OFF)                           | $V_{S} = 12 \text{ V}$       |                     | 6.2                   |     | 7.0                   |    |

| Open load compare voltage <sup>5</sup> | $18V > V_{DSC} > 0.65*V_{S}$ | $V_{\rm DS(OL)C}$   | V <sub>DSC</sub> -1.6 |     | V <sub>DSC</sub> -0.9 | V  |

| Open load detection current (Ou        | I <sub>D(OL)</sub>           | 100                 |                       | 500 | mA                    |    |

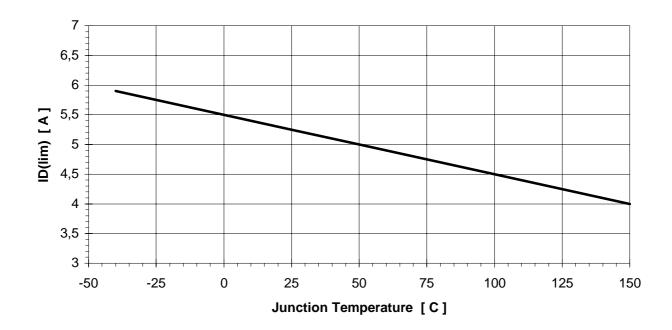

| Overload threshold current             | $T_j = 25$ °C                | I <sub>D(lim)</sub> | 5.25                  |     |                       | Α  |

| (V <sub>S</sub> ≥ 9.5 V)               | $T_j = 150$ °C               |                     | 4                     |     |                       |    |

| Overtemperature monitoring three       | eshold <sup>6</sup>          | $T_{th}$            | 170                   |     | 200                   | °C |

| Hysteresis                             |                              | $T_{hys}$           |                       | 10  |                       | K  |

### **Application Description**

This IC is specially designed to drive inductive loads (relays, electromagnetic valves). Integrated clamp-diodes limit the output voltage peak when switching off an inductive load.

For the detection of errors there are two status outputs, which monitor the following errors by logic levels:

- thermal overload monitoring,

- open and short load to ground in active an inactive mode,

- overloading of output (also shorted load to supply) in active mode.

### **Circuit Description**

#### **Input Circuits**

The control and enable inputs, all active high, consist of Schmitt triggers with hysteresis. All inputs are connected with pull-down current sources. Not connected inputs are interpreted as "low".

#### **Switching Stages**

The power outputs consist of a DMOS power transistor with open drain. The output stages are short-load-protected throughout the operating range. Integrated clamp-diodes limit voltage spikes produced when inductive loads are discharged.

#### **Protective Circuit**

The outputs are protected against current overload. There is no protection against reverse polarity of the supply voltage.

-

<sup>&</sup>lt;sup>5</sup> V<sub>DSC</sub> is the output voltage of the other channel used for open load compare detection

<sup>&</sup>lt;sup>6</sup> This parameter will not be tested but assured by design

#### **Error Detection**

The status output signal of the switching stages at normal operation is LOW = OFF; HIGH = ON. In case of any error the status outputs are set according to the table below. If <u>current overload</u> occurs, the error condition is stored in an internal register and the output is shutdown. To reset this register the control input of the affected channel has to be switched off and then on again. The state of the error detection circuit is directly dependent on the input status.

In case of <u>thermal overload</u> the output stage will not be switched off but it will be monitored via the status outputs.

Open load is detected for both on- and off-modus.

In the on-modus the load current is monitored. If it drops below the specified threshold open load is detected. In the off mode, the ouput voltage is monitored.

An open load condition is detected when the output voltage of a given channel is below 55 % of the supply voltage Vs. Also the output voltages of two outputs are compaired against each other in off condition with a fixed offset of typ. 1.25 V to recognize GND bypasses. To suppress fault diagnosis during the flyback phase of the compared output, the diagnostic circuit includes a latch function. Reset of this latch is done at end of the flyback phase, additionally it can be reseted by a low signal on the enable input and by a high signal of the input signal. See also the block diagramm of open load detection.

### **Diagnostic Table**

| Operating Condition | Inputs |     | Power Outputs |      | Status Outputs |     |     |

|---------------------|--------|-----|---------------|------|----------------|-----|-----|

|                     | ENA    | IN1 | IN2           | OUT1 | OUT2           | ST1 | ST2 |

|                     | L      | Χ   | Х             | OFF  | OFF            | L   | L   |

|                     | Н      | L   | L             | OFF  | OFF            | L   | L   |

| Normal Function     | Н      | Н   | L             | ON   | OFF            | Н   | L   |

|                     | Н      | L   | Н             | OFF  | ON             | L   | Н   |

|                     | Τ      | Η   | Н             | ON   | ON             | Η   | Н   |

|                     | Χ      | L   | L             | OFF  | OFF            | L   | L   |

| Thermal Overload    | L      | X   | X             | OFF  | OFF            | L   | L   |

|                     | Η      | Η   | Н             | ON   | ON             | L   | L   |

|                     | Χ      | L   |               | OFF  |                | Η   |     |

| Open Load Channel 1 | L      | Н   | 1)            | OFF  | 1)             | Н   | 1)  |

|                     | Н      | Н   |               | ON   |                | L   |     |

|                     | Χ      |     | L             |      | OFF            |     | Η   |

| Open Load Channel 2 | L      | 1)  | Н             | 1)   | OFF            | 1)  | Н   |

|                     | Η      |     | Н             |      | ON             |     | L   |

|                     | L      | Χ   |               | OFF  |                | L   |     |

| Overload Channel 1  | Н      | L   | 1)            | OFF  | 1)             | L   | 1)  |

|                     | Н      | Н   |               | OFF  |                | L   |     |

|                     | L      |     | X             |      | OFF            |     | Ĺ   |

| Overload Channel 2  | Н      | 1)  | L             | 1)   | OFF            | 1)  | L   |

|                     | Н      |     | Н             |      | OFF            |     | L   |

1) see normal function

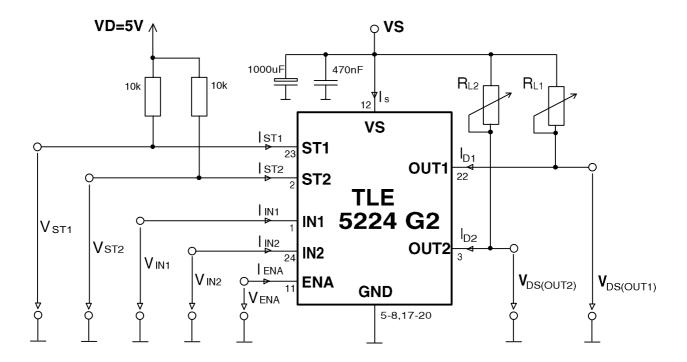

### **Test Circuit**

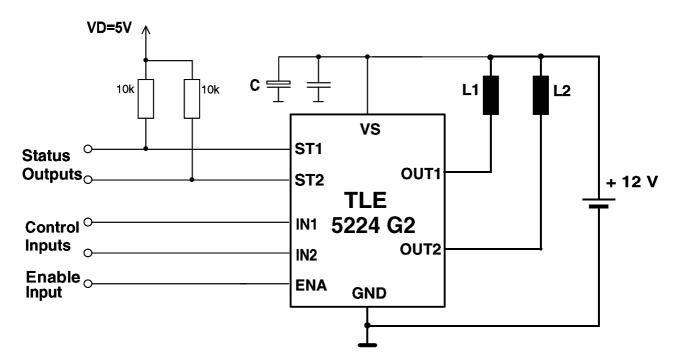

## **Application Circuit**

The blocking capacitor C is recommended to avoid critical negative voltage spikes on  $V_s$  in case of battery interruption during OFF-commutation.

## **Timing Diagram**

## **Overload Current versus temperature**

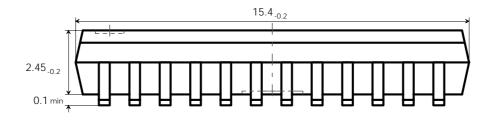

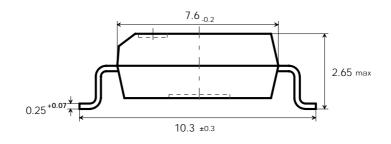

## Package and ordering code

all dimensions in mm

| P - DSO - 24 - L16 | Ordering code |

|--------------------|---------------|

|                    | Q67006-A9253  |

(Dual-in-line package, small-outline) 24 B 24 DIN 41870 T17