# High Reliability, Ultra-Low Power Microcontroller Powered by Arm Cortex M4 Processor with FPU for Industrial and IoT

### **General Description**

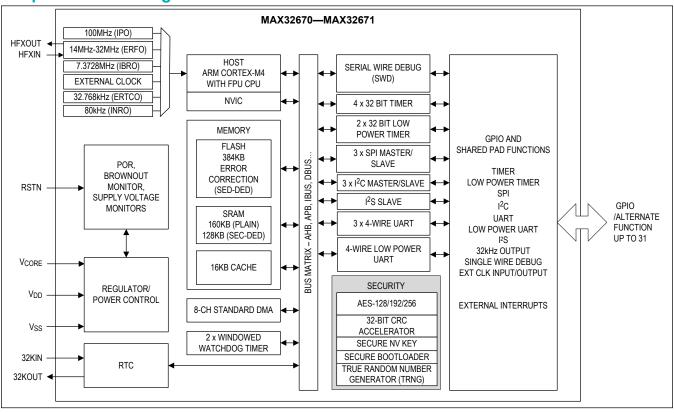

In the Darwin family, the MAX32670/MAX32671 are ultralow power, cost-effective, high reliability 32-bit microcontrollers enabling designs with complex sensor processing without compromising battery life. They combine a flexible and versatile power management unit with the powerful Arm® Cortex®-M4 processor with floating point unit (FPU). The MAX32670/MAX32671 also offer legacy designs an easy and cost optimal upgrade path from 8- or 16-bit microcontrollers.

The devices integrate up to 384KB of flash and 160KB of SRAM to accommodate application and sensor code. error correction coding (ECC), capable of single error correction and double error detection (SEC-DED), is implemented over the entire flash, RAM, and cache to ensure ultra-reliable code execution for demanding applications. Additional features such as the two windowed watchdog timers with fully flexible and independent clocking have been added to further enhance reliable operation. Brownout detection ensures proper operation during power-down and power-up events and unexpected supply transients.

Multiple high-speed peripherals such as 3.4MHz I<sup>2</sup>C, 50MHz SPI, and 4MBAUD UARTs are included to maximize communication bandwidth. In addition, a low-power UART is available for operation in the lowest power sleep modes to facilitate wakeup on activity without any loss of data. A total of six timers with I/O capability are provided, including two low-power timers to enable pulse counting, capture/compare and PWM generation even in the lowest power sleep modes. The devices pack all this capability in tiny form factors: 5mm x 5mm 40-pin TQFN-EP and 1.842mm x 2.670mm 24-bump WLP packages.

### **Applications**

- Smart Sensor Controller

- Industrial Sensors

- Optical Communication Modules

- Secure Radio Modem Controller

- Battery-Powered Medical Devices

- System Housekeeping Controller

- Algorithm Coprocessor

#### Ordering Information appears at end of data sheet.

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

### **Benefits and Features**

- High-Efficiency Microcontroller for Low Power, High Reliability Devices

- · Arm Cortex-M4 Core with FPU Up to 100MHz

- 384KB Flash Memory with Error Correction

- 160KB SRAM (128KB with ECC Enabled), Optionally Preserved in Lowest Power Modes

- 16KB Unified Cache with ECC

- UART Bootloader

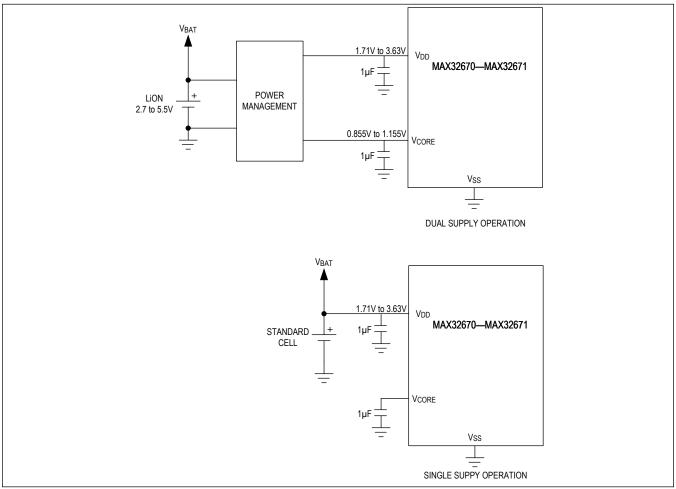

- Dual or Single-Supply Operation

- Ultra-Low 0.9-1.1V V<sub>CORE</sub> Supply Voltage

- Internal LDO Operation from Single Supply 1.7V to 3.6V

- Wide Operating Temperature: -40°C to +105°C

- Flexible Clocking Schemes

- · Internal High Speed 100MHz Oscillator

- Internal Low Power 7.3728MHz and Ultra-Low Power 80kHz Oscillators

- 14MHz to 32MHz Oscillator (External Crystal Required)

- 32.768kHz Oscillator (External Crystal Required)

- · External Clock Input for the Core

- · External Clock Input for the LPUART and LPTMR

- Power Management Maximizes Uptime for Battery Applications

- 44µA/MHz Active at 0.9V Up to 12MHz

- 50μA/MHz Active at 1.1V Up to 100MHz

- 2.6μA Full Memory Retention Power in Backup Mode at V<sub>DD</sub> = 1.8V

- 350nA Ultra-Low Power RTC at V<sub>DD</sub> = 1.8V

- Wake from LPUART or LPTMR

- Optimal Peripheral Mix Provides Platform Scalability

- Up to 31 General-Purpose I/O Pins

- Up to Three SPI Master/Slave (Up to 50MHz)

- Up to Three 4-Wire UART (Up to 4MBAUD)

- · One Low Power UART (LPUART)

- Up to Three I<sup>2</sup>C Master/Slave 3.4Mbps High Speed

- Eight-Channel Standard DMA Controller

- Up to Four 32-Bit Timers (TMR)

- Up to Two Low Power 32-Bit Timers (LPTMR)

- · Two Windowed Watchdog Timers

- One I<sup>2</sup>S Slave for Digital Audio Interface

- · Security and Integrity

- Available Secure Boot

- AES 128/192/256 Hardware Acceleration Engine

- TRNG Compliant to SP800-90B

- · 32-Bit CRC Acceleration Engine

# High Reliability, Ultra-Low Power Microcontroller Powered by Arm Cortex M4 Processor with FPU for Industrial and IoT

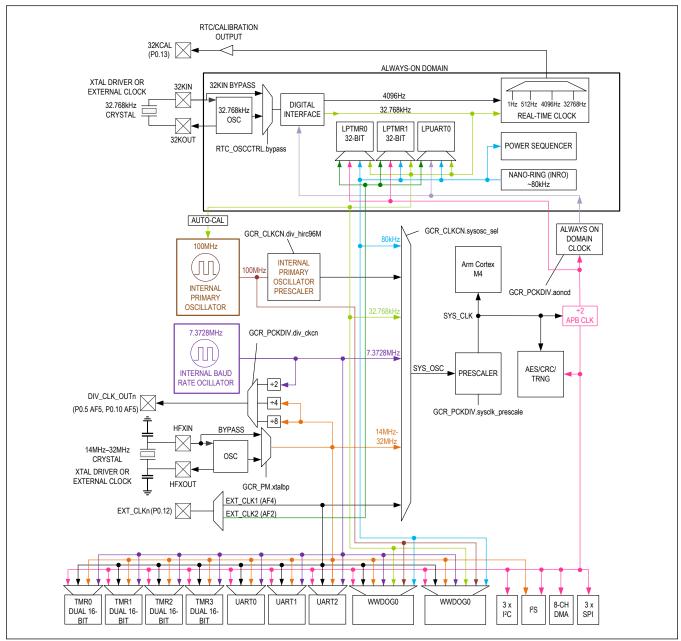

### **Simplified Block Diagram**

# High Reliability, Ultra-Low Power Microcontroller Powered by Arm Cortex M4 Processor with FPU for Industrial and IoT

### **TABLE OF CONTENTS**

| General Description                               |    |

|---------------------------------------------------|----|

| Applications                                      | 1  |

| Benefits and Features                             | 1  |

| Simplified Block Diagram                          | 2  |

| Package Information                               | 7  |

| 40 TQFN-EP                                        | 7  |

| Electrical Characteristics                        | 7  |

| Electrical Characteristics—SPI                    | 23 |

| Electrical Characteristics—I <sup>2</sup> C       |    |

| Electrical Characteristics—I <sup>2</sup> S Slave | 26 |

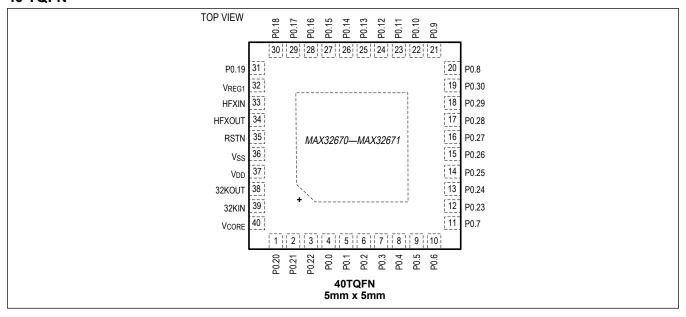

| Pin Configuration                                 | 30 |

| 40 TQFN                                           | 30 |

| Pin Description                                   | 30 |

| Detailed Description                              | 34 |

| MAX32670/MAX32671                                 | 34 |

| Arm Cortex-M4 Processor with FPU Engine           | 34 |

| Memory                                            | 34 |

| Internal Flash Memory                             | 34 |

| Internal SRAM                                     | 34 |

| Clocking Scheme                                   |    |

| General-Purpose I/O and Special Function Pins     |    |

| Standard DMA Controller                           |    |

| Power Management                                  |    |

| Power Management Unit                             |    |

| Active Mode                                       | 36 |

| Sleep Mode                                        |    |

| DeepSleep Mode                                    | 36 |

| Backup Mode                                       |    |

| Storage Mode                                      |    |

| Real-Time Clock                                   | 37 |

| Windowed Watchdog Timer (WWDT)                    |    |

| 32-Bit Timer/Counter/PWM (TMR, LPTMR)             | 38 |

| Serial Peripherals                                | 39 |

| I <sup>2</sup> C Interface (I2C)                  | 39 |

| Serial Peripheral Interface (SPI)                 |    |

| I <sup>2</sup> S Interface (I2S)                  | 40 |

| UART (UART, LPUART)                               | 40 |

| Security                                          | 41 |

## High Reliability, Ultra-Low Power Microcontroller Powered by Arm Cortex M4 Processor with FPU for Industrial and IoT

# TABLE OF CONTENTS (CONTINUED) AES 41 True Random Number Generator (TRNG) 41 CRC Module 41 Secure Boot 41 Debug and Development Interface (SWD) 41 Applications Information 42 Bypass Capacitors 42 Ordering Information 42

# High Reliability, Ultra-Low Power Microcontroller Powered by Arm Cortex M4 Processor with FPU for Industrial and IoT

### LIST OF FIGURES

| Figure 1. Power-Supply Operational Modes  | 27 |

|-------------------------------------------|----|

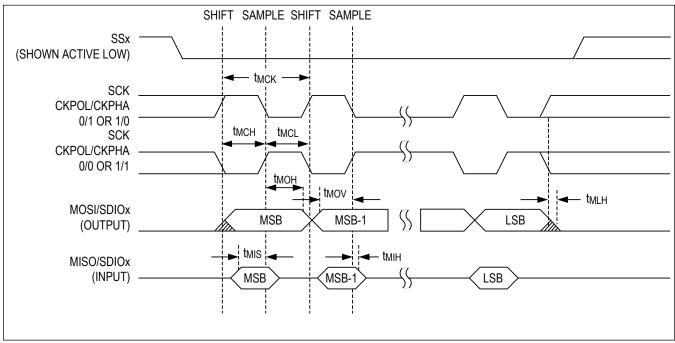

| Figure 2. SPI Master Mode Timing Diagram  | 28 |

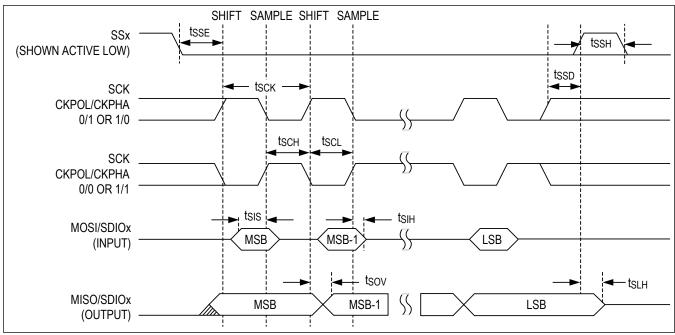

| Figure 3. SPI Slave Mode Timing Diagram   | 28 |

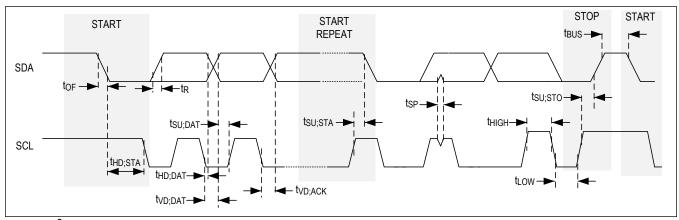

| Figure 4. I <sup>2</sup> C Timing Diagram | 29 |

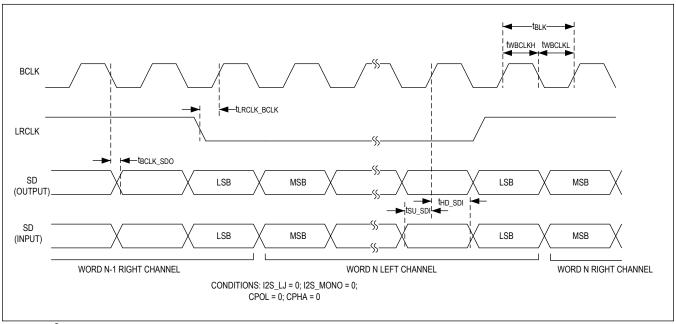

| Figure 5. I <sup>2</sup> S Timing Diagram | 29 |

| Figure 6. Clocking Scheme                 | 35 |

# High Reliability, Ultra-Low Power Microcontroller Powered by Arm Cortex M4 Processor with FPU for Industrial and IoT

### **LIST OF TABLES**

| Table 1. Backup Mode RAM Retention   | 37 |

|--------------------------------------|----|

| Table 2. Timer Configuration Options | 38 |

| Table 3. SPI Configuration Options   | 40 |

| Table 4 LIART Configuration Options  | 41 |

### **Package Information**

### 40 TQFN-EP

| Package Code                            | T4055+1 |  |  |  |

|-----------------------------------------|---------|--|--|--|

| Outline Number                          | 21-0140 |  |  |  |

| Land Pattern Number                     | 90-0016 |  |  |  |

| Thermal Resistance, Single-Layer Board: |         |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 45°C/W  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 2 °C/W  |  |  |  |

| Thermal Resistance, Four-Layer Board:   |         |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 28°C/W  |  |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 2°C/W   |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

| PARAMETER                                                      | SYMBOL                                              | CONDITIONS                                              |                    | MIN   | TYP  | MAX   | UNITS |  |

|----------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------|--------------------|-------|------|-------|-------|--|

| POWER / BOTH SINGLE-SUPPLY OPERATION AND DUAL-SUPPLY OPERATION |                                                     |                                                         |                    |       |      |       |       |  |

| Supply Voltage                                                 | V <sub>DD</sub>                                     |                                                         |                    | 1.71  | 1.8  | 3.63  | V     |  |

|                                                                |                                                     |                                                         | OVR = [00]         | 0.855 | 0.9  | 0.945 |       |  |

|                                                                |                                                     | Dual-supply operation                                   | OVR = [01]         | 0.95  | 1.0  | 1.05  | V     |  |

| Supply Voltage, Core                                           | V <sub>CORE</sub>                                   |                                                         | Default OVR = [10] | 1.045 | 1.1  | 1.155 |       |  |

|                                                                |                                                     | No power supply connection for single supply operation  |                    |       | _    |       |       |  |

| Dower Feil Dooet                                               |                                                     | Monitors V <sub>DD</sub>                                |                    | 1.58  |      | 1.71  |       |  |

| Power-Fail Reset<br>Voltage                                    | V <sub>RST</sub> Monitors V <sub>CC</sub> operation | Monitors V <sub>CORE</sub> operation                    | during dual-supply | 0.77  |      | 0.845 | V     |  |

| Power-On Reset<br>Voltage                                      |                                                     | Monitors V <sub>DD</sub>                                |                    |       | 1.4  |       |       |  |

|                                                                | V <sub>POR</sub>                                    | Monitors V <sub>CORE</sub> during dual supply operation |                    |       | 0.65 |       | V     |  |

### **Electrical Characteristics (continued)**

| PARAMETER                              | SYMBOL                                                                                                                                                                                                                       | COND                                                                                                                                                                                                                    | ITIONS                                                                         | MIN TYP | MAX | UNITS  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------|-----|--------|

| POWER / SINGLE-SUPP                    | LY OPERATION                                                                                                                                                                                                                 | (V <sub>DD</sub> ONLY)                                                                                                                                                                                                  |                                                                                |         |     |        |

|                                        |                                                                                                                                                                                                                              | Dynamic, IPO enabled, total                                                                                                                                                                                             | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>fSYS_CLK(MAX) =<br>100MHz | 64.5    |     |        |

|                                        |                                                                                                                                                                                                                              | current into V <sub>DD</sub><br>pin, V <sub>DD</sub> = 3.3V,<br>CPU in Active<br>mode, executing<br>Coremark, ECC<br>disabled, inputs                                                                                   | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>fSYS_CLK(MAX) =<br>50MHz  | 62.5    |     |        |

|                                        |                                                                                                                                                                                                                              | tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA                                                                                                                                              | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>fSYS_CLK(MAX) =<br>12MHz  | 59.5    |     |        |

|                                        |                                                                                                                                                                                                                              | Dynamic, IPO enabled, total current into V <sub>DD</sub> pin, V <sub>DD</sub> = 1.8V, CPU in Active mode, executing Coremark, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink 0mA | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>fSYS_CLK(MAX) =<br>100MHz | 64.2    |     | μΑ/MHz |

| V <sub>DD</sub> Current Active<br>Mode | IDD_DACTS                                                                                                                                                                                                                    |                                                                                                                                                                                                                         | OVR = [01],<br>Internal regulator<br>set to 1.0V,<br>fSYS_CLK(MAX) =<br>50MHz  | 62.1    |     |        |

|                                        | Dynamic, IPO enabled, total current into V <sub>D</sub> pin, V <sub>DD</sub> = 3.3\times CPU in Active mode, executir While(1), ECC disabled, inputs tied to V <sub>SS</sub> or \times 1000000000000000000000000000000000000 |                                                                                                                                                                                                                         | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>fSYS_CLK(MAX) =<br>12MHz  | 59.1    |     |        |

|                                        |                                                                                                                                                                                                                              | enabled, total                                                                                                                                                                                                          | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>fSYS_CLK(MAX) =<br>100MHz | 49.4    |     |        |

|                                        |                                                                                                                                                                                                                              | pin, V <sub>DD</sub> = 3.3V,<br>CPU in Active<br>mode, executing<br>While(1), ECC<br>disabled, inputs                                                                                                                   | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>fSYS_CLK(MAX) =<br>50MHz  | 47      |     |        |

|                                        |                                                                                                                                                                                                                              | tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink                                                                                                                                                        | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>fSYS_CLK(MAX) =<br>12MHz  | 44.1    |     |        |

### **Electrical Characteristics (continued)**

| PARAMETER | SYMBOL                | COND                                                                                                  | ITIONS                                                                                                           | MIN                                              | TYP                                              | MAX | UNITS |    |

|-----------|-----------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|-----|-------|----|

|           |                       | Dynamic, IPO<br>enabled, total<br>current into V <sub>DD</sub>                                        | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>fSYS_CLK(MAX) =<br>100MHz                                   |                                                  | 49.3                                             |     |       |    |

|           |                       | pin, V <sub>DD</sub> = 1.8V,<br>CPU in Active<br>mode, executing<br>While(1), ECC<br>disabled, inputs | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>fSYS_CLK(MAX) =<br>50MHz                                    |                                                  | 46.7                                             |     |       |    |

|           |                       | tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA                            | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>fSYS_CLK(MAX) =<br>12MHz                                    |                                                  | 44.1                                             |     |       |    |

|           |                       | current into V <sub>DD</sub><br>pin, V <sub>DD</sub> = 3.3V,<br>CPU in Active<br>mode 0MHz            | OVR = [10],<br>internal regulator<br>set to 1.1V                                                                 |                                                  | 796                                              |     |       |    |

|           |                       |                                                                                                       | CPU in Active mode 0MHz                                                                                          | CPU in Active mode 0MHz                          | OVR = [01],<br>internal regulator<br>set to 1.0V |     | 647   |    |

|           |                       |                                                                                                       | execution, ECC<br>disabled, inputs<br>tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA | OVR = [00],<br>internal regulator<br>set to 0.9V |                                                  | 475 |       | μA |

|           | I <sub>DD_FACTS</sub> | Fixed, IPO<br>enabled, total<br>current into V <sub>DD</sub>                                          | OVR = [10],<br>internal regulator<br>set to 1.1V                                                                 |                                                  | 762                                              |     | μΑ    |    |

|           |                       | pin, V <sub>DD</sub> = 1.8V,<br>CPU in Active<br>mode 0MHz<br>execution, ECC                          | CPU in Active mode 0MHz                                                                                          | OVR = [01],<br>internal regulator<br>set to 1.0V |                                                  | 620 |       |    |

|           |                       | disabled, inputs<br>tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA        | OVR = [00],<br>internal regulator<br>set to 0.9V                                                                 |                                                  | 450                                              |     |       |    |

### **Electrical Characteristics (continued)**

| PARAMETER                                    | SYMBOL                                                                                                       | COND                                                                                                                                                                                                     | ITIONS                                                                                    | MIN TYP | MAX | UNITS  |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|-----|--------|

|                                              | 1 1 1                                                                                                        | Dynamic, IPO enabled, total                                                                                                                                                                              | OVR = [10],<br>internal regulator<br>set to 1.1V                                          | 39.2    |     |        |

| V <sub>DD</sub> Current Sleep Mode IDD_DSLPS |                                                                                                              | current into V <sub>DD</sub> pin, V <sub>DD</sub> = 3.3V, CPU in Sleep mode, ECC disabled, standard DMA with two                                                                                         | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz | 37.5    |     |        |

|                                              |                                                                                                              | channels active, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink 0mA                                                                                                             | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>12MHz | 36.1    |     |        |

|                                              |                                                                                                              | Dynamic, IPO<br>enabled, total<br>current into V <sub>DD</sub>                                                                                                                                           | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>fSYS_CLK(MAX) =<br>100MHz            | 39.2    |     |        |

|                                              | I <sub>DD_DSLPS</sub>                                                                                        | pin, V <sub>DD</sub> = 1.8V,<br>CPU in Sleep<br>mode, ECC<br>disabled, standard<br>DMA with two<br>channels active,<br>inputs tied to V <sub>SS</sub><br>or V <sub>DD</sub> , outputs<br>source/sink 0mA | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz | 37.5    |     | μΑ/MHz |

|                                              |                                                                                                              |                                                                                                                                                                                                          | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>12MHz | 36.4    |     |        |

|                                              |                                                                                                              | Dynamic, IPO enabled, total current into V <sub>DD</sub>                                                                                                                                                 | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>fSYS_CLK(MAX) =<br>100MHz            | 21.1    |     |        |

|                                              | pin, V <sub>DD</sub> = 3.3 CPU in Sleep mode, ECC disabled, DMA disabled, input tied to V <sub>SS</sub> or V | pin, V <sub>DD</sub> = 3.3V,<br>CPU in Sleep<br>mode, ECC<br>disabled, DMA<br>disabled, inputs                                                                                                           | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz | 19      |     |        |

|                                              |                                                                                                              | tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA                                                                                                                               | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>fsys_clk(MAX) =<br>12MHz             | 17.2    |     |        |

### **Electrical Characteristics (continued)**

| PARAMETER                                        | SYMBOL                | COND                                                                                                                                                                              | ITIONS                                                                         | MIN                                              | TYP  | MAX | UNITS |

|--------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------|------|-----|-------|

|                                                  |                       | Dynamic, IPO<br>enabled, total<br>current into V <sub>DD</sub>                                                                                                                    | OVR = [10],<br>internal regulator<br>set to 1.1V,<br>fSYS_CLK(MAX) =<br>100MHz |                                                  | 21.2 |     |       |

|                                                  |                       | pin, V <sub>DD</sub> = 1.8V,<br>CPU in Sleep<br>mode, ECC<br>disabled, DMA<br>disabled, inputs                                                                                    | OVR = [01],<br>internal regulator<br>set to 1.0V,<br>fSYS_CLK(MAX) =<br>50MHz  |                                                  | 19.1 |     |       |

|                                                  |                       | tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA                                                                                                        | OVR = [00],<br>internal regulator<br>set to 0.9V,<br>fSYS_CLK(MAX) =<br>12MHz  |                                                  | 17.3 |     |       |

|                                                  |                       | enabled, total current into V <sub>DD</sub> pin, V <sub>DD</sub> = 3.3V, CPU in Sleep mode, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink | OVR = [10],<br>internal regulator<br>set to 1.1V                               |                                                  | 796  |     |       |

|                                                  |                       |                                                                                                                                                                                   | OVR = [01],<br>internal regulator<br>set to 1.0V                               |                                                  | 647  |     |       |

|                                                  |                       |                                                                                                                                                                                   | tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink               | OVR = [00],<br>internal regulator<br>set to 0.9V |      | 475 |       |

|                                                  | IDD_FSLPS             | Fixed, IPO<br>enabled, total<br>current into V <sub>DD</sub>                                                                                                                      | OVR = [10],<br>internal regulator<br>set to 1.1V                               |                                                  | 762  |     | μΑ    |

|                                                  |                       | pin, V <sub>DD</sub> = 1.8V,<br>CPU in Sleep<br>mode, ECC                                                                                                                         | OVR = [01],<br>internal regulator<br>set to 1.0V                               |                                                  | 620  |     |       |

|                                                  |                       | outputs source/sink ir                                                                                                                                                            | OVR = [00],<br>internal regulator<br>set to 0.9V                               |                                                  | 450  |     |       |

|                                                  |                       | Standby state with                                                                                                                                                                | V <sub>DD</sub> = 3.3V                                                         |                                                  | 4.0  |     |       |

| V <sub>DD</sub> Fixed Current,<br>DeepSleep Mode | I <sub>DD_FDSLS</sub> | full data retention                                                                                                                                                               | V <sub>DD</sub> = 1.8V                                                         |                                                  | 3.6  |     | μΑ    |

### **Electrical Characteristics (continued)**

| PARAMETER                      | SYMBOL                 | CONE                                    | DITIONS                                               | MIN | TYP   | MAX | UNITS |

|--------------------------------|------------------------|-----------------------------------------|-------------------------------------------------------|-----|-------|-----|-------|

|                                |                        |                                         | 0KB SRAM<br>retained, retention<br>regulator disabled |     | 0.32  |     |       |

|                                |                        |                                         | 20KB SRAM retained                                    |     | 1.04  |     |       |

|                                |                        | V <sub>DD</sub> = 3.3V, RTC<br>disabled | 40KB SRAM retained                                    |     | 1.37  |     |       |

|                                |                        |                                         | 80KB SRAM retained                                    |     | 1.90  |     |       |

| V <sub>DD</sub> Fixed Current, | lee segue              |                                         | 160KB SRAM retained                                   |     | 2.84  |     | μA    |

| Backup Mode                    | IDD_FBKUS              | V <sub>DD</sub> = 1.8V, RTC disabled    | 0KB SRAM<br>retained, retention<br>regulator disabled |     | 0.11  |     | μΑ    |

|                                |                        |                                         | 20KB SRAM retained                                    |     | 0.77  |     | -     |

|                                |                        |                                         | 40KB SRAM retained                                    |     | 1.14  |     |       |

|                                |                        |                                         | 80KB SRAM retained                                    |     | 1.68  |     |       |

|                                |                        |                                         | 160KB SRAM retained                                   |     | 2.64  |     |       |

| V <sub>DD</sub> Fixed Current, | lan sasaa              | V <sub>DD</sub> = 3.3V                  |                                                       |     | 0.362 |     | μA    |

| Storage Mode                   | I <sub>DD_</sub> FSTOS | V <sub>DD</sub> = 1.8V                  |                                                       |     | 0.075 |     | μΑ    |

| Sleep Mode Resume<br>Time      | t <sub>SLP_ONS</sub>   |                                         |                                                       |     | 2.1   |     | μs    |

| DeepSleep Mode                 | t                      | fast_wk_en = 1                          |                                                       |     | 89    |     | us    |

| Resume Time                    | t <sub>DSL_ONS</sub>   | fast_wk_en = 0                          |                                                       |     | 129   |     | us    |

| Backup Mode Resume<br>Time     | t <sub>BKU_ONS</sub>   | Includes system init execution time     | Includes system initialization and ROM                |     | 1.25  |     | ms    |

| Storage Mode Resume<br>Time    | t <sub>STO_ONS</sub>   | Includes system init execution time     | alization and ROM                                     |     | 1.5   |     | ms    |

### **Electrical Characteristics (continued)**

| PARAMETER                              | SYMBOL                                                      | COND                                                                                                                         | ITIONS                                                                            | MIN                                                    | TYP                                            | MAX                                                                              | UNITS     |      |

|----------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------|-----------|------|

| POWER / DUAL-SUPPL                     | Y OPERATION (\                                              | / <sub>DD</sub> AND V <sub>CORE</sub> )                                                                                      | 1                                                                                 |                                                        |                                                |                                                                                  |           |      |

|                                        |                                                             | Dynamic, IPO<br>enabled, total<br>current into V <sub>CORE</sub>                                                             | OVR = [10], V <sub>CORE</sub><br>= 1.1V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz |                                                        | 63.7                                           |                                                                                  |           |      |

|                                        |                                                             | pin, CPU in Active<br>mode, executing<br>Coremark, ECC<br>disabled, inputs                                                   | OVR = [01], V <sub>CORE</sub><br>= 1.0V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz  |                                                        | 61.9                                           |                                                                                  |           |      |

| V <sub>CORE</sub> Current, Active Mode |                                                             | tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA                                                   | OVR = [00], V <sub>CORE</sub><br>= 0.9V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>12MHz  |                                                        | 59.4                                           |                                                                                  | 0 /041.1- |      |

|                                        |                                                             | Dynamic, IPO enabled, total current into V <sub>CORE</sub> pin, CPU in Active mode, executing While(1), ECC disabled, inputs | OVR = [10], V <sub>CORE</sub><br>= 1.1V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz |                                                        | 48.9                                           |                                                                                  | – μA/MHz  |      |

|                                        |                                                             |                                                                                                                              | pin, CPU in Active<br>mode, executing<br>While(1), ECC                            | pin, CPU in Active<br>mode, executing<br>While(1), ECC | mode, executing While(1), ECC disabled, inputs | OVR = [01], V <sub>CORE</sub><br>= 1.0V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz |           | 46.6 |

|                                        |                                                             | tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA                                                   | OVR = [00], V <sub>CORE</sub><br>= 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  |                                                        | 44.5                                           | 5                                                                                |           |      |

|                                        |                                                             | Fixed, IPO enabled, total                                                                                                    | OVR = [10], V <sub>CORE</sub><br>= 1.1V                                           |                                                        | 362                                            |                                                                                  |           |      |

|                                        |                                                             | current into V <sub>CORE</sub> pin, CPU in Active                                                                            | OVR = [01], V <sub>CORE</sub><br>= 1.0V                                           |                                                        | 217                                            |                                                                                  | -         |      |

|                                        | ICORE_FACTD   mode 0MHz   execution, ECC   disabled, inputs | OVR = [00], V <sub>CORE</sub><br>= 0.9V                                                                                      |                                                                                   | 109                                                    |                                                | μΑ                                                                               |           |      |

### **Electrical Characteristics (continued)**

| PARAMETER                            | SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                        | COND                                                                                                                                                                                                                    | ITIONS                                               | MIN TYP | MAX | UNITS      |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------|-----|------------|

| V <sub>DD</sub> Current, Active Mode |                                                                                                                                                                                                                                                                                                                                                                                                                                               | Dynamic, IPO enabled, total current into V <sub>DD</sub> pin, V <sub>DD</sub> = 3.3V, CPU in Active mode, executing Coremark, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink 0mA | OVR = [10],<br>fsys_clk(MAX) =<br>100MHz             | 0.51    |     |            |

|                                      | outputs source/sink omA  Dynamic, IPO enabled, total current into V <sub>DD</sub> pin, V <sub>DD</sub> = 3.3V, CPU in Active mode, executing Coremark, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> outputs source/sink omA  Dynamic, IPO enabled, total current into V <sub>DD</sub> pin, V <sub>DD</sub> = 1.8V, CPU in Active mode, executing Coremark, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> | enabled,total current into V <sub>DD</sub> pin, V <sub>DD</sub> = 3.3V, CPU in Active mode, executing Coremark, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink                   | OVR = [01],<br>fsys_clk(MAX) =<br>50MHz              | 0.51    |     | μΑ/MHz     |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                               | enabled, total current into V <sub>DD</sub> pin, V <sub>DD</sub> = 3.3V, CPU in Active mode, executing Coremark, ECC disabled, inputs tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink                  | OVR = [00],<br>fsys_clk(MAX( =<br>12MHz              | 0.51    |     | prvivii iz |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                               | enabled, total current into V <sub>DD</sub>                                                                                                                                                                             | OVR = [10],<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz | 0.23    |     |            |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                               | CPU in Active mode, executing                                                                                                                                                                                           | OVR = [01],<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz  | 0.23    |     |            |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                               | disabled, inputs<br>tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink                                                                                                                                 | OVR = [00],<br>fsys_clk(MAX) =<br>12MHz              | 0.23    |     |            |

### **Electrical Characteristics (continued)**

| PARAMETER | SYMBOL    | COND                                                                                                                                                          | ITIONS                                               | MIN TYP | MAX | UNITS |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------|-----|-------|

|           |           | Dynamic, IPO<br>enabled, total<br>current into V <sub>DD</sub>                                                                                                | OVR = [10],<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz | 0.51    |     |       |

|           |           | pin, V <sub>DD</sub> = 3.3V,<br>CPU in Active<br>mode, executing<br>While(1), ECC                                                                             | OVR = [01],<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz  | 0.51    |     |       |

|           |           | disabled, inputs<br>tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA                                                                | OVR = [00],<br>f <sub>SYS_CLK(MAX(</sub> =<br>12MHz  | 0.51    |     |       |

|           |           | Dynamic, IPO<br>enabled, total<br>current into V <sub>DD</sub>                                                                                                | OVR = [10],<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz | 0.23    |     |       |

|           |           | pin, V <sub>DD</sub> = 1.8V,<br>CPU in Active<br>mode, executing                                                                                              | OVR = [01],<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz  | 0.23    |     |       |

|           |           | tied to V <sub>SS</sub> or V <sub>DD</sub> ,                                                                                                                  | OVR = [00],<br>fsys_clk(MAX) =<br>12MHz              | 0.23    |     |       |

|           |           | Fixed, IPO enabled, total                                                                                                                                     | OVR = [10], V <sub>CORE</sub><br>= 1.1V              | 367     |     |       |

|           |           | current into $V_{DD}$<br>pin, $V_{DD} = 3.3V$ ,                                                                                                               | OVR = [01], V <sub>CORE</sub><br>= 1.0V              | 367     |     |       |

|           |           | CPU in Active<br>mode 0MHz<br>execution, ECC<br>disabled, inputs<br>tied to VSS or<br>VDD, outputs<br>source/sink 0mA                                         | OVR = [00], V <sub>CORE</sub><br>= 0.9V              | 307     |     | μA    |

|           | IDD_FACTD | Fixed, IPO enabled, total                                                                                                                                     | OVR = [10], V <sub>CORE</sub><br>= 1.1V              | 350     |     | μΑ    |

|           |           | current into V <sub>DD</sub> pin, V <sub>DD</sub> = 1.8V, CPU in Active mode 0MHz execution, ECC disabled, inputs tied to VSS or VDD, outputs source/sink 0mA | OVR = [01], V <sub>CORE</sub><br>= 1.0V              | 350     |     | 1     |

|           |           |                                                                                                                                                               | OVR = [00], V <sub>CORE</sub> = 0.9V                 | 290     |     |       |

### **Electrical Characteristics (continued)**

| PARAMETER                        | SYMBOL     | COND                                                                                           | ITIONS                                                                            | MIN TY | P MAX | UNITS                                |

|----------------------------------|------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------|-------|--------------------------------------|

|                                  |            | Dynamic, IPO<br>enabled, total<br>current into V <sub>CORE</sub>                               | OVR = [10], V <sub>CORE</sub><br>= 1.1V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz | 39     | .2    |                                      |

| V <sub>CORE</sub> Current, Sleep |            | pin, CPU in Sleep<br>mode, ECC<br>disabled, standard<br>DMA with two<br>channels active.       | OVR = [01], V <sub>CORE</sub><br>= 1.0V,<br>f <sub>SYS</sub> CLK(MAX) =<br>50MHz  | 37     | .5    | UNITS  μΑ/ΜΗz  μΑ                    |

|                                  |            | inputs tied to V <sub>SS</sub> or V <sub>DD</sub> , outputs source/sink 0mA                    | OVR = [00], V <sub>CORE</sub><br>= 0.9V,<br>f <sub>SYS</sub> CLK(MAX) =<br>12MHz  | 3:     | 7     | \ /\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|                                  | CORE_DSLPD | Dynamic, IPO enabled, total current into V <sub>CORE</sub>                                     | OVR = [10], V <sub>CORE</sub><br>= 1.1V,<br>f <sub>SYS_CLK(MAX)</sub> = 100MHz    | 21     | .1    | μA/MHz                               |

| Mode Mode                        |            | pin, CPU in Sleep<br>mode, ECC<br>disabled, DMA<br>disabled, inputs                            | OVR = [01], V <sub>CORE</sub><br>= 1.0V,<br>f <sub>SYS_CLK(MAX)</sub> = 50MHz     | 19     | .2    |                                      |

|                                  |            | tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA                     | OVR = [00], V <sub>CORE</sub><br>= 0.9V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>12MHz  | 17     | .9    |                                      |

|                                  |            | Fixed, IPO enabled, total                                                                      | OVR [10], V <sub>CORE</sub> = 1.1V                                                | 36     | 52    |                                      |

|                                  | loope eers | current into V <sub>CORE</sub><br>pin, CPU in Sleep<br>mode, ECC                               | OVR [01], V <sub>CORE</sub> = 1.0V                                                | 21     | 7     | ]<br>A                               |

|                                  | CORE_FSLPD | disabled, inputs<br>tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA | OVR [00], V <sub>CORE</sub> = 0.9V                                                | 10     | 9     | μπ                                   |

### **Electrical Characteristics (continued)**

| PARAMETER                              | SYMBOL                | COND                                                                                                        | ITIONS                                                                            | MIN TYP | MAX | UNITS                               |

|----------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------|-----|-------------------------------------|

|                                        |                       | Dynamic, IPO<br>enabled, total<br>current into V <sub>DD</sub><br>pin, V <sub>DD</sub> = 3.3V,              | OVR = [10], V <sub>CORE</sub><br>= 1.1V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz | 0.001   |     |                                     |

|                                        |                       | CPU in Sleep<br>mode, ECC<br>disabled, standard<br>DMA with two                                             | OVR = [01], V <sub>CORE</sub><br>= 1.0V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz  | 0.001   |     | μA/MHz                              |

|                                        | l                     | channels active,<br>inputs tied to V <sub>SS</sub><br>or V <sub>DD</sub> , outputs<br>source/sink 0mA       | OVR = [00], V <sub>CORE</sub><br>= 0.9V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>12MHz  | 0.001   |     | \ /\ /\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|                                        | IDD_DSLPD             | Dynamic, IPO<br>enabled, total<br>current into V <sub>DD</sub><br>pin, V <sub>DD</sub> = 1.8V,              | OVR = [10], V <sub>CORE</sub><br>= 1.1V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>100MHz | 0.001   |     | μA/MHz                              |

|                                        |                       | CPU in Sleep<br>mode, ECC<br>disabled, standard<br>DMA with two                                             | OVR = [01], V <sub>CORE</sub><br>= 1.0V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>50MHz  | 0.001   |     |                                     |

| V <sub>DD</sub> Current, Sleep<br>Mode |                       | channels active,<br>inputs tied to V <sub>SS</sub><br>or V <sub>DD</sub> , outputs<br>source/sink 0mA       | OVR = [00], V <sub>CORE</sub><br>= 0.9V,<br>f <sub>SYS_CLK(MAX)</sub> =<br>12MHz  | 0.001   |     |                                     |

|                                        |                       | Fixed, IPO enabled, total                                                                                   | OVR = [10], V <sub>CORE</sub><br>= 1.1V                                           | 367     |     |                                     |

|                                        |                       | current into V <sub>DD</sub><br>pin, V <sub>DD</sub> = 3.3V,<br>CPU in Sleep                                | OVR = [01], V <sub>CORE</sub><br>= 1.0V                                           | 367     |     |                                     |

|                                        |                       | mode, ECC<br>disabled, inputs<br>tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA | OVR = [00], V <sub>CORE</sub> = 0.9V                                              | 307     |     |                                     |

|                                        | I <sub>DD_FSLPD</sub> | Fixed, IPO enabled, total                                                                                   | OVR = [10], V <sub>CORE</sub><br>= 1.1V                                           | 350     |     | μΑ                                  |

|                                        |                       | current into V <sub>DD</sub><br>pin, V <sub>DD</sub> = 1.8V,<br>CPU in Sleep                                | OVR = [01], V <sub>CORE</sub><br>= 1.0V                                           | 350     |     |                                     |

|                                        |                       | mode, ECC<br>disabled, inputs<br>tied to V <sub>SS</sub> or V <sub>DD</sub> ,<br>outputs source/sink<br>0mA | OVR = [00], V <sub>CORE</sub> = 0.9V                                              | 290     |     |                                     |

# High Reliability, Ultra-Low Power Microcontroller Powered by Arm Cortex M4 Processor with FPU for Industrial and IoT

### **Electrical Characteristics (continued)**

| PARAMETER                                          | SYMBOL      | CONDITIONS                                         | MIN TY | P MAX | UNITS |

|----------------------------------------------------|-------------|----------------------------------------------------|--------|-------|-------|

| V <sub>CORE</sub> Fixed Current,<br>DeepSleep Mode |             | V <sub>DD</sub> = 3.3V, V <sub>CORE</sub> = 1.1V   | 10     | )     |       |

|                                                    | ICORE FDSLP | V <sub>DD</sub> = 3.3V, V <sub>CORE</sub> = 0.855V | 3.     | 8     | ]     |

|                                                    | D           | V <sub>DD</sub> = 1.8V, V <sub>CORE</sub> = 1.1V   | 10     | )     | - μA  |

|                                                    |             | V <sub>DD</sub> = 1.8V, V <sub>CORE</sub> = 0.855V | 3.     | 8     |       |

|                                                    |             | V <sub>DD</sub> = 3.3V, V <sub>CORE</sub> = 1.1V   | 0.3    | 34    |       |

| V <sub>DD</sub> Fixed Current,                     | l           | V <sub>DD</sub> = 3.3V, V <sub>CORE</sub> = 0.855V | 0.3    | 34    | ]     |

| DeepSleep Mode                                     | IDD_FDSLPD  | V <sub>DD</sub> = 1.8V, V <sub>CORE</sub> = 1.1V   | 0.0    | )8    | - μΑ  |

|                                                    |             | V <sub>DD</sub> = 1.8V, V <sub>CORE</sub> = 0.855V | 0.0    | )8    |       |

### **Electrical Characteristics (continued)**

| PARAMETER                        | SYMBOL      | COND                                   | ITIONS                                                | MIN TYP MAX | UNITS |

|----------------------------------|-------------|----------------------------------------|-------------------------------------------------------|-------------|-------|

|                                  |             |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 0.225       |       |

|                                  |             | 0KB SRAM retained, RTC                 | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V | 0.13        |       |

|                                  |             | disabled, retention regulator disabled | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 0.23        |       |

|                                  |             |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 0.14        |       |

|                                  |             |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 1.256       |       |

|                                  |             | 20KB SRAM<br>retained with RTC         | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V | 0.507       |       |

|                                  |             | disabled                               | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 1.256       |       |

|                                  |             |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 0.507       |       |

|                                  |             |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 2.243       |       |

| V <sub>CORE</sub> Fixed Current, |             | 40KB SRAM retained with RTC            | $V_{DD} = 3.3V,$<br>$V_{CORE} = 0.855V$               | 0.877       | μA    |

| Backup Mode                      | ICORE_FBKUD | disabled                               | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 2.243       | μΑ    |

|                                  |             |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 0.877       |       |

|                                  |             |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 3.97        |       |

|                                  |             | 80KB SRAM                              | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V | 1.49        |       |

|                                  |             | retained with RTC disabled             | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 3.97        |       |

|                                  |             |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 1.49        |       |

|                                  |             |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 7.22        |       |

|                                  |             | 160KB SRAM                             | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V | 2.61        |       |

|                                  |             | retained with RTC disabled             | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 7.22        |       |

|                                  |             |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 2.61        |       |

### **Electrical Characteristics (continued)**

| PARAMETER                      | SYMBOL                | COND                                   | ITIONS                                                | MIN TYP MAX | UNITS |

|--------------------------------|-----------------------|----------------------------------------|-------------------------------------------------------|-------------|-------|

|                                |                       |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 0.34        |       |

|                                |                       | 0KB SRAM retained with RTC             | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V | 0.34        |       |

|                                |                       | disabled, retention regulator disabled | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 0.12        |       |

|                                |                       |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 0.12        |       |

|                                |                       |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 0.32        |       |

|                                |                       | 20KB SRAM<br>retained with RTC         | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V | 0.32        |       |

|                                |                       | disabled                               | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 0.108       |       |

|                                |                       |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 0.108       |       |

|                                |                       |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 0.32        |       |

| V <sub>DD</sub> Fixed Current, | 1                     | 40KB SRAM retained with RTC            | $V_{DD} = 3.3V,$<br>$V_{CORE} = 0.855V$               | 0.108       | μA    |

| Backup Mode                    | I <sub>DD_FBKUD</sub> | disabled                               | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 0.108       | μΑ    |

|                                |                       |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 0.108       |       |

|                                |                       |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 0.32        |       |

|                                |                       | 80KB SRAM retained with RTC            | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V | 0.32        |       |

|                                |                       | disabled                               | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 0.108       |       |

|                                |                       |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 0.108       |       |

|                                |                       |                                        | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 1.1V   | 0.32        |       |

|                                |                       | 160KB SRAM                             | V <sub>DD</sub> = 3.3V,<br>V <sub>CORE</sub> = 0.855V | 0.32        |       |

|                                |                       | retained with RTC disabled             | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 1.1V   | 0.108       |       |

|                                |                       |                                        | V <sub>DD</sub> = 1.8V,<br>V <sub>CORE</sub> = 0.855V | 0.108       |       |

### **Electrical Characteristics (continued)**

| PARAMETER                                                                                   | SYMBOL               | CONDITIONS                                                               | MIN                      | TYP   | MAX                      | UNITS                 |

|---------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------|--------------------------|-------|--------------------------|-----------------------|

|                                                                                             |                      | V <sub>DD</sub> = 3.3V, V <sub>CORE</sub> = 1.1V                         |                          | 0.226 |                          |                       |

| V <sub>CORE</sub> Fixed Current,                                                            |                      | V <sub>DD</sub> = 3.3V, V <sub>CORE</sub> = 0.855V                       |                          | 0.112 |                          | μA μs μs us ms V V V  |

| Storage Mode                                                                                | CORE_FSTOD           | V <sub>DD</sub> = 1.8V, V <sub>CORE</sub> = 1.1V                         |                          | 0.226 |                          |                       |

|                                                                                             |                      | V <sub>DD</sub> = 1.8V, V <sub>CORE</sub> = 0.855V                       |                          | 0.112 |                          | 1                     |

|                                                                                             |                      | V <sub>DD</sub> = 3.3V; V <sub>CORE</sub> = 1.1V                         |                          | 0.335 |                          |                       |

| V <sub>DD</sub> Fixed Current,                                                              |                      | V <sub>DD</sub> = 3.3V; V <sub>CORE</sub> = 0.855V                       |                          | 0.335 |                          | 1                     |

| Storage Mode                                                                                | IDD_FSTOD            | V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> = 1.1V                         |                          | 0.085 |                          | - μΑ                  |

|                                                                                             |                      | V <sub>DD</sub> = 1.8V; V <sub>CORE</sub> = 0.855V                       |                          | 0.085 |                          | μA μs μs μs us ms V V |

| Sleep Mode Resume<br>Time                                                                   | t <sub>SLP_OND</sub> |                                                                          |                          | 2.1   |                          | μs                    |

| DeepSleep Mode                                                                              |                      | fast_wk_en = 1                                                           |                          | 81    |                          | μs                    |

| Resume Time                                                                                 | . I IDOL OND         | fast_wk_en = 0                                                           |                          | 129   |                          | us                    |

| Backup Mode Resume<br>Time                                                                  | t <sub>BKU_OND</sub> | Includes system initialization and ROM execution time                    |                          | 1.25  |                          | ms                    |

| Storage Mode Resume<br>Time                                                                 | tsto_ond             | Includes system initialization and ROM execution time                    |                          | 1.5   |                          | ms                    |

| GENERAL-PURPOSE I/O                                                                         | )                    |                                                                          |                          |       |                          | 1                     |

| Input Low Voltage for All GPIO, RSTN                                                        | V <sub>IL_GPIO</sub> | Pin configured as GPIO                                                   |                          |       | 0.3 ×<br>V <sub>DD</sub> | V                     |

| Input High Voltage for All GPIO, RSTN                                                       | V <sub>IH_GPIO</sub> | Pin configured as GPIO                                                   | 0.7 ×<br>V <sub>DD</sub> |       |                          | V                     |

|                                                                                             |                      | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 1mA, DS[1:0] = 00<br>(Note 1) |                          | 0.2   | 0.4                      |                       |

| Output Low Voltage for All GPIO Except P0.6,                                                | V                    | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 2mA, DS[1:0] = 10<br>(Note 1) |                          | 0.2   | 0.4                      |                       |

| P0.7, P0.12, P0.13,<br>P0.18, and P0.19                                                     | V <sub>OL_GPIO</sub> | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 4mA, DS[1:0] = 01<br>(Note 1) |                          | 0.2   | 0.4                      |                       |

|                                                                                             |                      | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 6mA, DS[1:0] = 11<br>(Note 1) |                          | 0.2   | 0.4                      |                       |

| Output Low Voltage for                                                                      |                      | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 2mA, DS = 0 (Note 1)          |                          | 0.2   | 0.4                      |                       |

| GPIO P0.6, P0.7, P0.12, P0.13, P0.18, P0.19                                                 | V <sub>OL_I2C</sub>  | V <sub>DD</sub> = 1.71V, I <sub>OL</sub> = 10mA, DS = 1 (Note 1)         |                          | 0.2   | 0.4                      | V                     |