#### **NUP4302MR6**

# Schottky Diode Array for Four Data Line ESD Protection

The NUP4302MR6 is designed to protect high speed data line interface from ESD, EFT and lighting.

#### **Features**

- Very Low Forward Voltage Drop

- Fast Switching

- PN Junction Guard Ring for Transient and ESD Protection

- ESD Rating of Class 3B (Exceeding 16 kV) per Human Body Model and Class C (Exceeding 400 V) per Machine Model

- IEC 61000-4-2 Level 4 ESD Protection

- Flammability Rating: UL 94 V-0

- Pb-Free Package is Available

#### **Applications**

- Ultra High-Speed Switching

- USB 1.1 and 2.0 Power and Data Line Protection

- Digital Video Interface (DVI)

- Monitors and Flat Panel Displays

#### ON Semiconductor®

http://onsemi.com

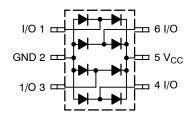

### PIN CONFIGURATION AND SCHEMATIC

#### TSOP-6 CASE 318G STYLE 12

67

MARKING DIAGRAM

= Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

\*Date Code orientation may vary depending upon manufacturing location.

#### **ORDERING INFORMATION**

| Device        | Package             | Shipping <sup>†</sup> |

|---------------|---------------------|-----------------------|

| NUP4302MR6T1  | TSOP-6              | 3000/Tape & Reel      |

| NUP4302MR6T1G | TSOP-6<br>(Pb-Free) | 3000/Tape & Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **NUP4302MR6**

#### **MAXIMUM RATINGS** ( $T_J = 25^{\circ}C$ unless otherwise noted)

| Rating                                            | Symbol           | Value       | Unit |

|---------------------------------------------------|------------------|-------------|------|

| Peak Reverse Breakdown Voltage                    | V <sub>BR</sub>  | 30          | V    |

| Forward Power Dissipation (T <sub>A</sub> = 25°C) | P <sub>F</sub>   | 225         | mW   |

| Forward Continuous Current                        | Ι <sub>F</sub>   | 200         | mA   |

| Junction Operating Temperature                    | TJ               | -55 to +125 | °C   |

| Storage Temperature Range                         | T <sub>stg</sub> | −55 to +150 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS** ( $T_J = 25^{\circ}C$ unless otherwise noted)

| Parameter                 | Symbol          | Conditions                                                                   | Min Typ |          | Max  | Unit |

|---------------------------|-----------------|------------------------------------------------------------------------------|---------|----------|------|------|

| Reverse Breakdown Voltage | $V_{BR}$        | I <sub>R</sub> = 100 μA                                                      | 30      |          |      | V    |

| Reverse Leakage           | I <sub>R</sub>  | V <sub>R</sub> = 25 V                                                        |         |          | 30   | μΑ   |

| Forward Voltage           | V <sub>F</sub>  | I <sub>F</sub> = 0.1 mAdc                                                    |         |          | 0.28 | V    |

| Forward Voltage           | V <sub>F</sub>  | I <sub>F</sub> = 1.0 mAdc                                                    |         |          | 0.35 | V    |

| Forward Voltage           | V <sub>F</sub>  | I <sub>F</sub> = 10 mAdc                                                     |         |          | 0.45 | V    |

| Forward Voltage           | V <sub>F</sub>  | I <sub>F</sub> = 100 mAdc                                                    |         |          | 1.00 | V    |

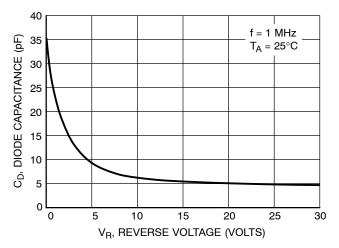

| Total Capacitance         | C <sub>T</sub>  | $V_R$ = 0 V, f = 1.0 MHz, I/O to Ground $V_R$ = 0 V, f = 1.0 MHz, I/O to I/O |         | 28<br>18 | pF   |      |

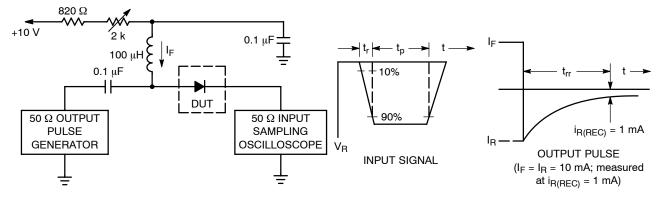

| Reverse Recovery Time     | t <sub>rr</sub> | $I_F = I_R = 10 \text{ mA}, I_{R(REC)} = 1.0 \text{ mA} \text{ (Figure 1)}$  |         |          | 5.0  | ns   |

Notes: 1. A 2.0 k $\Omega$  variable resistor adjusted for a Forward Current (I<sub>F</sub>) of 10 mA.

- 2. Input pulse is adjusted so  $I_{R(peak)}$  is equal to 10 mA.

- 3.  $t_p \gg t_{rr}$

Figure 1. Recovery Time Equivalent Test Circuit

#### NUP4302MR6

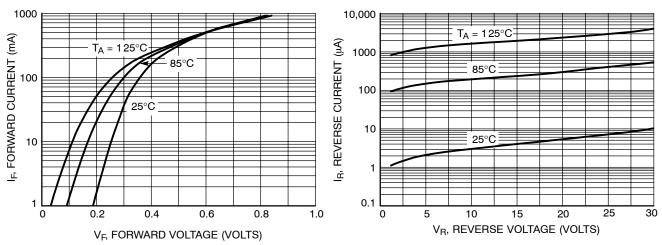

Figure 2. Forward Current as a Function of Forward Voltage; Typical Values

Figure 3. Reverse Current as a Function of Reverse Voltage; Typical Values

Figure 4. Diode Capacitance as a Function of Reverse Voltage; Typical Values

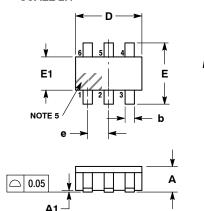

#### TSOP-6 CASE 318G-02 **ISSUE V**

L2

C SEATING PLANE

**DATE 12 JUN 2012**

STYLE 6: PIN 1. COLLECTOR 2. COLLECTOR

3. BASE 4. EMITTER

5. COLLECTOR 6. COLLECTOR

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM

- MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSIONS D

- AND E1 ARE DETERMINED AT DATUM H.

PIN ONE INDICATOR MUST BE LOCATED IN THE INDICATED ZONE.

|     | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN         | NOM  | MAX  |  |

| Α   | 0.90        | 1.00 | 1.10 |  |

| A1  | 0.01        | 0.06 | 0.10 |  |

| b   | 0.25        | 0.38 | 0.50 |  |

| С   | 0.10        | 0.18 | 0.26 |  |

| D   | 2.90        | 3.00 | 3.10 |  |

| E   | 2.50        | 2.75 | 3.00 |  |

| E1  | 1.30        | 1.50 | 1.70 |  |

| е   | 0.85        | 0.95 | 1.05 |  |

| L   | 0.20        | 0.40 | 0.60 |  |

| L2  | 0.25 BSC    |      |      |  |

| М   | 0°          | _    | 10°  |  |

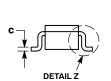

**DETAIL Z**

Н

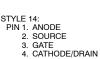

| STYLE 1: PIN 1. DRAIN 2. DRAIN 3. GATE 4. SOURCE 5. DRAIN 6. DRAIN | STYLE 2:<br>PIN 1. EMITTER 2<br>2. BASE 1<br>3. COLLECTO<br>4. EMITTER 1<br>5. BASE 2<br>6. COLLECTO |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| STYLE 7:<br>PIN 1. COLLECTOR<br>2. COLLECTOR<br>3. BASE<br>4. N/C  | STYLE 8:<br>PIN 1. Vbus<br>2. D(in)<br>3. D(in)+<br>4. D(out)+                                       |

COLLECTOR

6. EMITTER

2. SOURCE 2

3. GATE 2

4. DRAIN 2

5. SOURCE 1

DRAIN 1

STYLE 13: PIN 1. GATE 1

STYLE 3: PIN 1. ENABLE 2. N/C 3. R BOOST 4. Vz 5. V in 6. V out

STYLE 9:

STYLE 15: PIN 1. ANODE

3 GATE

5. N/C

SOURCE

DRAIN

6. CATHODE

| IN 1 | LOW VOLTAGE GATE  |  |

|------|-------------------|--|

| 2    | DRAIN             |  |

| 3    | SOURCE            |  |

| 4    | DRAIN             |  |

| 5    | DRAIN             |  |

| 6    | HIGH VOLTAGE GATE |  |

STYLE 4: PIN 1. N/C

2. GND

STYLE 16: PIN 1. ANODE/CATHODE BASE 3 FMITTER COLLECTOR 5. ANODE CATHODE

STYLE 5: PIN 1. EMITTER 2 2. BASE 2 2. V in 3. NOT USED 4. GROUND 3. COLLECTOR 1 EMITTER 1 5. ENABLE 6. LOAD BASE 1 6. COLLECTOR 2 STYLE 10: PIN 1. D(OUT)+

| STYLE  | 11:            |

|--------|----------------|

| PIN 1. | SO             |

| 2.     | DR             |

| 3.     | DR             |

| 4.     | SC             |

| 5.     | GA             |

| 6.     | DR             |

|        |                |

|        | 3.<br>4.<br>5. |

STYLE 17: PIN 1. EMITTER

BASE

STYLE 12: OURCE 1 RAIN 2 RAIN 2 2. GROUND 3. I/O 4. I/O URCF 2 RAIN 1/GATE 2 6. I/O

## 3 ANODE/CATHODE

#### CATHODE COLLECTOR

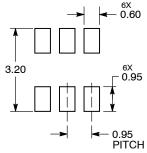

#### **RECOMMENDED SOLDERING FOOTPRINT\***

**DIMENSIONS: MILLIMETERS**

#### **GENERIC** MARKING DIAGRAM\*

XXX = Specific Device Code Α =Assembly Location

Υ = Year

W = Work Week = Pb-Free Package

XXX = Specific Device Code M = Date Code

= Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ", may or may not be present.

| DOCUMENT NUMBER: | 98ASB14888C | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TSOP-6      |                                                                                                                                                                                 | PAGE 1 OF 1 |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

**TECHNICAL SUPPORT**

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative